目录

1 硬件描述语言简介

1.1 硬件描述语言简介

1.2 硬件编程语言的发展历史

1.3 两种硬件描述的比较

1.4 硬件描述语言的应用场景

1.5 基本程序结构

1.5.1 基本程序结构

1.5.2 基本语句和描述方法

1.5.3 仿真

1 硬件描述语言简介

1.1 硬件描述语言简介

硬件描述语言(Hardware Description Language, HDL)是一种用于描述电子系统(尤其是数字电路)结构、行为和功能的专用编程语言。它允许工程师以文本形式对硬件(如集成电路、FPGA、ASIC等)进行建模、设计和验证,是电子设计自动化(EDA)流程的核心工具之一。

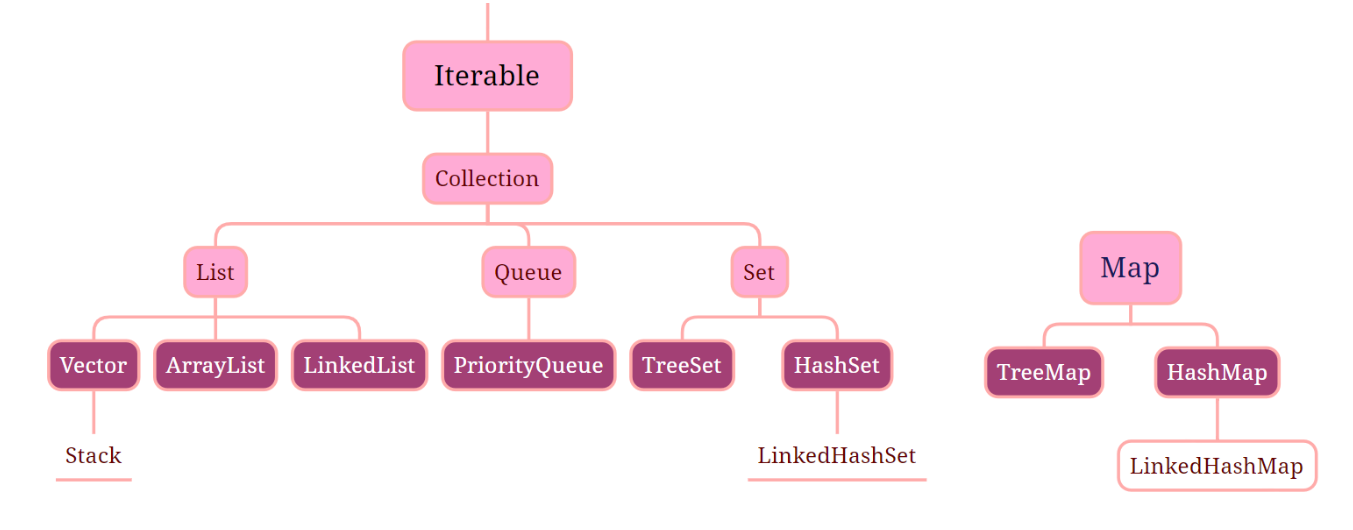

相较于传统的编程语言,例如C、Java等,硬件描述更加注重硬件之间的连接关系、时序运行以及并行操作等物理特性。主流的硬件描述语言包括Verilog HDL和VHDL,如下所示:

1.2 硬件编程语言的发展历史

上世纪1970s开始,随着电路的复杂度的提升,传统的手工绘图的方式开始变得低效,学术界开始研究文本硬件描述方法。1972年,美国南加州大学 D. D. Gajski开始研究AHDL(A Hardware Programing Lauguage),这是早期的数字电路描述语言。

目前主流的两种硬件描述语言均诞生在20世纪80年代,在上世纪80年代时,已经有上百种硬件描述语言,是硬件描述语言快速发展的时代。其中,Verilog HDL是由Gateway Design Automation公司开发的,后来被Cadence公司收购。VHDL是上世界80年代美国国防部资助开发的,作为ADA语言的一部分,用于规范文档和设计。VHDL和Verilog HDL分别在1985年和1997年成为IEEE标准。

2000年以后,衍生了更加高级的HDL,支持系统级验证和混合信号建立。

1.3 两种硬件描述的比较

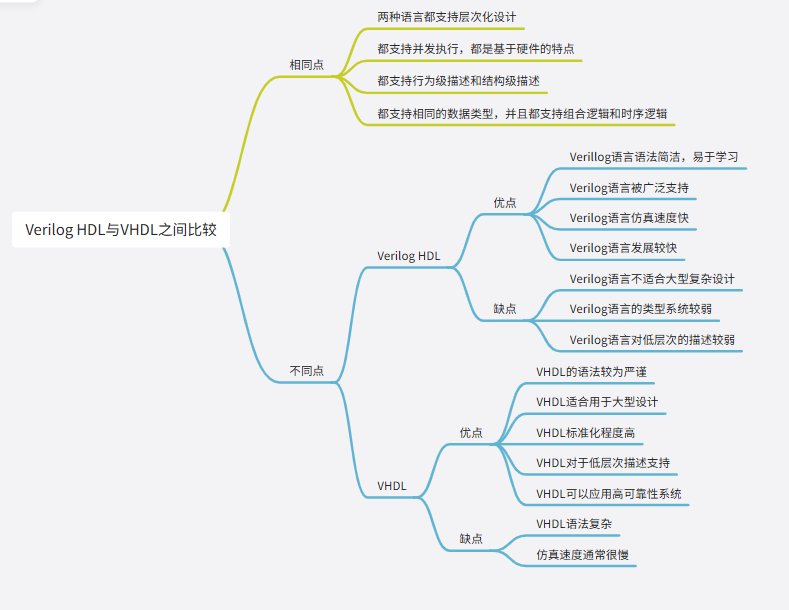

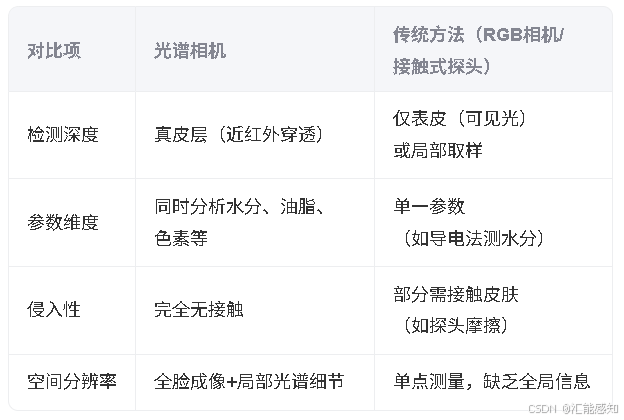

Verilog HDL和VHDL之间都有相同点:

- 两种语言都支持层次化设计。

- 都支持并发执行,都是基于硬件的特点。

- 都支持行为级描述和结构级描述。

- 都支持相同的数据类型,并且都支持组合逻辑和时序逻辑。

除了相同点之外,Veriilog HDL和VHDL之间也存在不同点,对于Verilog HDL语言来说,相对于VHDL,优点为:

- Verillog语言语法简洁,易于学习。

- Verilog语言被广泛支持。

- Verilog语言仿真速度快。

- Verilog语言发展较快。

缺点为:

- Verilog语言不适合大型复杂设计。

- Verilog语言的类型系统较弱。

- Verilog语言对低层次的描述较弱。

对于VHDL语言,其优势为:

- VHDL的语法较为严谨。

- VHDL适合用于大型设计。

- VHDL标准化程度高。

- VHDL对于低层次描述支持。

- VHDL可以应用高可靠性系统。

而其劣势为:

- VHDL语法复杂。

- 仿真速度通常很慢。

将上面内容进行总结得:

1.4 硬件描述语言的应用场景

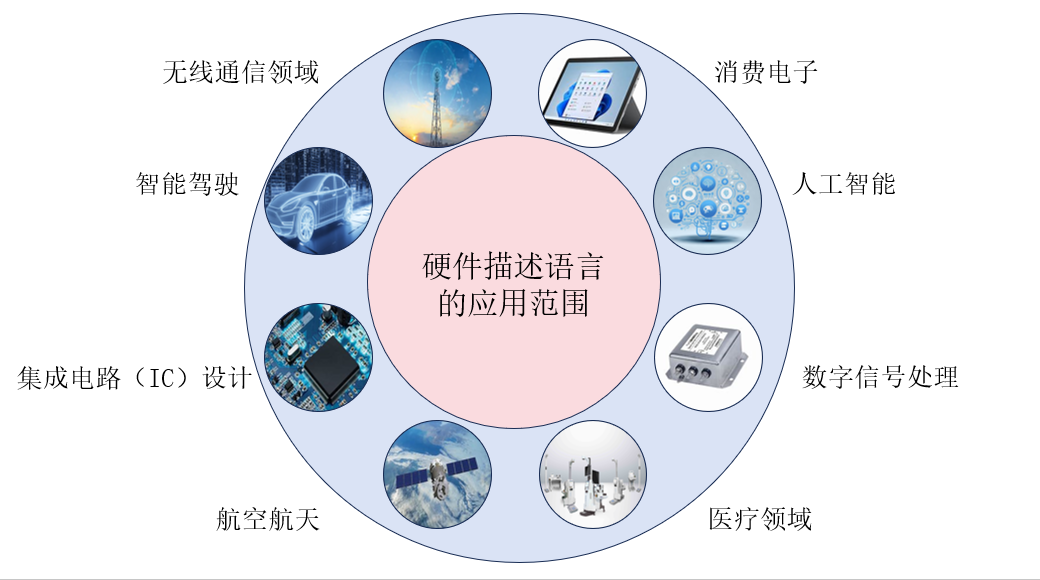

硬件描述语言的应用十分广泛,涵盖范围如下所示:

下面对于各个方面基进行简答介绍。

(1)人工智能

人工智能是当下火热的研究内容,HDL可以显著提升了深度学习中的神经网络计算,特别是图像识别中的卷积运算。通过硬件并行性,HDL可以有效地处理大量的图像数据,减少计算资源的浪费。同时,随着物联网(IoT)的发展,边缘计算是相对热门的话题,FPGA在边缘计算中可以提供快速、高效的数据处理能力,减少数据传输到云端的需求,降低延迟和带宽消耗。

(2)智能驾驶

CAN(Controller Area Network)总线是一种广泛应用于汽车电子、工业控制、航空航天等领域的可靠串行通信协议。CAN协议的数据帧结构包括帧起始位、仲裁字段、控制字段、数据字段、校验字段等多个部分。VHDL可以通过行为级描述来实现对这些字段的解析和生成,同时利用其并行处理能力来处理多个字段的同步操作。VHDL的高抽象性和模块化设计使得CAN协议的实现具有很高的灵活性和可扩展性。设计者可以根据不同的应用场景和需求,对CAN协议进行定制和优化。

(3)通信领域

HDL在通信领域同样也有应用。例如,在基带信号处理方面,完成各种调制方式,如相移键控(PSK)、正交幅度调制(QAM)等。HDL可根据不同的通信标准和需求,灵活实现调制和解调算法,将数字信号转换为适合在信道中传输的模拟信号。在射频信号处理方面,在发射端将基带信号上变频到射频频段以便通过天线发射,在接收端,将射频信号下变频到基带频段进行后续处理。FPGA 可以生成各种频率的本振信号,并与基带信号进行混频,实现频谱搬移。

(4)集成电路(IC)设计

在 IC 设计的早期阶段,设计人员通常使用 HDL 进行行为级描述。这种描述方式侧重于对电路功能的抽象表达,而不涉及具体的硬件结构。在 IC 设计过程中,需要对设计的功能进行验证,确保其符合设计要求。HDL 可以用于搭建测试平台,生成激励信号并监测电路的输出响应。例如,对于一个设计好的存储器芯片,使用 HDL 编写测试平台可以模拟不同的读写操作,检查存储器的读写功能是否正常。

(5)数字信号处理

HDL在数字信号处理有很多应用。例如在滤波器的设计方面,如果想设计一个FIR(有限冲击响应)滤波器,可以通过HDL代码在FPGA中实现。HDL代码可以定义滤波器的系数存储、乘法累加运算等逻辑,从而实现对输入信号的滤波处理。在快速傅里叶变化的应用中,FFT是数字信号处理中的重要算法,用于将时域信号转换为频域信号。HDL可以在FPGA中实现FFT算法的硬件加速。通过编写HDL代码,可以定义蝶形运算单元、数据存储和调度等逻辑,实现高效的FFT运算。

(6)医疗领域

HDL在医疗领域也有较多的应用,例如在医疗成像领域,在 MRI、CT 等医学成像设备中,HDL 可用于设计图像重建算法模块。通过对采集到的大量原始数据进行快速处理和运算,利用 HDL 实现如反投影算法、迭代重建算法等,能够在短时间内重建出高质量的人体内部器官图像,为医生提供准确的诊断依据。在医疗监护领域,DL 可用于设计生理信号采集与处理模块。可以对心电、血压、血氧等多种生理信号进行实时采集、放大、滤波和模数转换等处理。

(7)航空航天

HDL在高性能、高可靠性和和复杂系统设计方面有很多应用。例如,在航空发动机系统设计中,基于模型的系统工程(MBSE)方法结合HDL工具,可以实现需求驱动的正向设计流程,快速搭建系统模型,并与多学科联合仿真验证程序融合。HDL工具通过内置的设计规则集合(包括DO-254等安全关键设计规则集),能够确保设计满足航空航天行业的严格标准。

(8)消费电子

消费电子是普通人接触较多的领域,HDL在消费电子也有很大的应用。例如,在显示驱动方面实现屏幕控制和显示优化,在智能手机、平板电脑、智能手表等各类显示屏设备中,HDL 可用于设计显示驱动芯片。它能精确控制屏幕的像素点发光,实现不同分辨率、刷新率和色彩模式的显示。在音视频处理方面对于高清视频的解码,在智能电视、机顶盒、蓝光播放器等设备中,HDL 可用于设计专用的视频解码芯片。

1.5 基本程序结构

1.5.1 基本程序结构

和其他编程类似,Verilog HDL也是采用模块化的结构,以模块化的形式来描述数字电路系统。模块(module)是Verilog HDL语言中描述电路的基本单元。模块的基本语法如下所示:

module<模块化>(<端口列表>)

<定义>

<模块条目>

endmodule最基本的模块如下所示:

module module_name (

input [width] input1, // 输入端口

input [width] input2,

output [width] output1, // 输出端口

output [width] output2

);

// 模块内部逻辑

endmodule上面的端口定义两个输入端口和两个输出端口。

1.5.2 基本语句和描述方法

对于组合逻辑来说,使用assign实现组合逻辑:

assign output = input1 & input2; // 逻辑与操作组合逻辑是输出信号仅依赖于当前输入信号的逻辑。例如,设计一个简单的2输入与门:

module and_gate (

input wire a,

input wire b,

output wire y

);

assign y = a & b; // 组合逻辑

endmodule而对于时序逻辑电路来说,使用always块实现时序逻辑,通常与clock信号结合。如下所示:

always @(posedge clk) begin

if (reset) begin

reg_out <= 0;

end else begin

reg_out <= input;

end

end

时序逻辑的输出不仅依赖于当前输入,还依赖于过去的输入。例如,设计一个D触发器:

module d_ff (

input wire clk, // 时钟信号

input wire reset, // 异步复位信号

input wire d, // 数据输入

output reg q // 数据输出

);

always @(posedge clk or posedge reset) begin

if (reset) begin

q <= 0; // 异步复位

end else begin

q <= d; // 数据锁存

end

end

endmodule生成结构是Verilog中一种强大的功能,允许在编译时根据参数条件创建或重复模块实例、寄存器、线网或其他Verilog元素。它主要用于创建可配置和可重用的设计。主要的生产结果包括generate-for循环、generate-if循环、generate-case循环:

例如generate-for循环:

generate

if (WIDTH > 4) begin : wide_block

// 当WIDTH>8时包含的代码

reg [WIDTH-1:0] wide_reg;

end

else begin : narrow_block

// 否则包含的代码

reg [7:0] narrow_reg;

end

endgenerateVerilog中一种编译时循环结构,主要用于在硬件描述中创建重复的电路结构。

1.5.3 仿真

仿真用于验证Verilog代码的功能是否正确。通常使用仿真工具(如ModelSim、Vivado Simulator等)进行仿真。仿真工具会生成波形图,显示输入和输出信号随时间的变化。设计人员可以根据波形图判断是否设计正确。

因为本系列主要讲的是数字电子技术内容,在这里对于Verilog HDL和VHDL不进行更加细致的讲解,以后有机会的话可能对于这编程语言进行讲解。

![协同推荐算法实现的智能商品推荐系统 - [基于springboot +vue]](https://i-blog.csdnimg.cn/direct/f56aace797e04e46aac5ee9783213d0b.png)