前言

图片来源: 存储随笔

2022年8月份在美国FMS峰会上,Solidigm公司(前身为 Intel NAND 部门) 展示了全球第一款基于PLC NAND研发的SSD。这也标志着,PLC时代已正式拉开序幕。出于对 PLC 的好奇,本文分享PLC NAND 知识, 聊聊 PLC NAND 的前景。

1. PLC NAND 是什么?

PLC NAND 指的 Penta-Level Cell NNAD。 PLC 指的是单个存储单元

存储元

\color {#FF6D00}{存储元}

存储元 存 5 bit。对应的 TLC 每个存储元存 3 bit, QLC每个存储元存4 bit.

PLC 指的是单个存储单元

存储元

\color {#FF6D00}{存储元}

存储元 存 5 bit。对应的 TLC 每个存储元存 3 bit, QLC每个存储元存4 bit.

2. PLC NAND 发展历史?

PLC(第五代) 是 Intel 出售 NAND 部门给海力士之前研发出来的,实际上是相当超前的, 毕竟 QLC (第四代) 还没有成为主流。 现在主流的还是 TLC (第三代)。

其他大厂还没有推进 PLC, 可能是还不看好吧。

Solidigm 是独树一帜,别人都觉得你 QLC 还没稳住呢, 就去捣鼓 PLC 了。而 Solidigm 就是这么我行我素,颇有的像:

他人笑我太痴颠, 我笑他人看不穿

3. PLC 带来了什么变化?

3.1 PLC 容量提升

TLC 相对 MLC 容量提升了

50

%

\color {#FF6D00}{50\% }

50% 技术复杂读增加了 100%

QLC 相对 TLC 容量提升了

33

%

\color {#FF6D00}{33\% }

33%, 技术复杂读增加了 100%

PLC 相对于 QLC 容量提升了

25

%

\color {#FF6D00}{25\% }

25%, 技术复杂读增加了 100%

可以看出, 技术的复杂度增长远大于容量的增长。越往后, 这种投入产出低越低,所以单个存储元存的bit 数也不可能无限扩大。

3.2 QLC 延时增长

PLC 单个page页的写延迟是SLC的8倍,是TLC的2倍,读延迟是SLC的4倍,是TLC的约1.3倍。

3.3 QLC 寿命下降

不出意外, QLC NAND 的 物理块擦除次数也大幅降低,最大擦除次数降到了 35。对于 NAND 单个物理块, 使用寿命变得更少, 擦写 35 轮就寿终正寝了。

为了弥补擦除次数对产品使用寿命的影响,PLC势必要用在更大的容量的产品。

大容量存储换取更多的物理块, 弥补单个物理块擦除次数少的缺点

3.4 QLC 误码率 RBER 提高

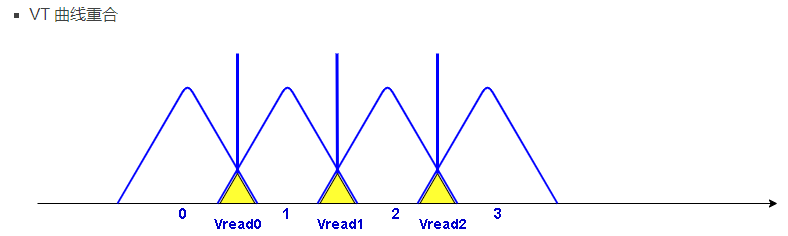

因为每个存储元存5 bit, 对应有 32 个电位(NAND VT 包络)。 每个电位的区间变得更窄,相邻的电位容易合在一起无法区分,这就是误码率 RBER ,可预见的是RBER 会显著升高。

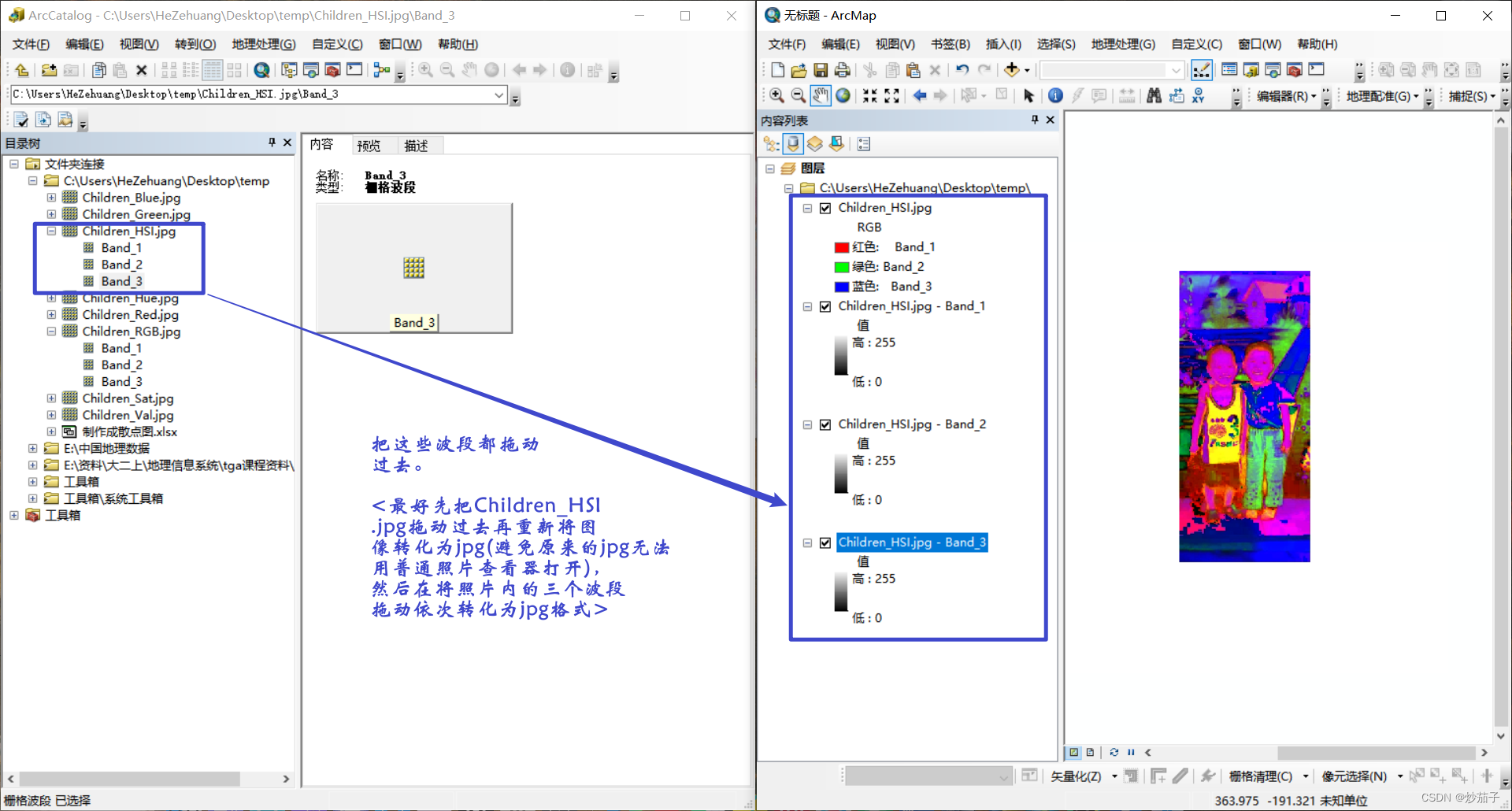

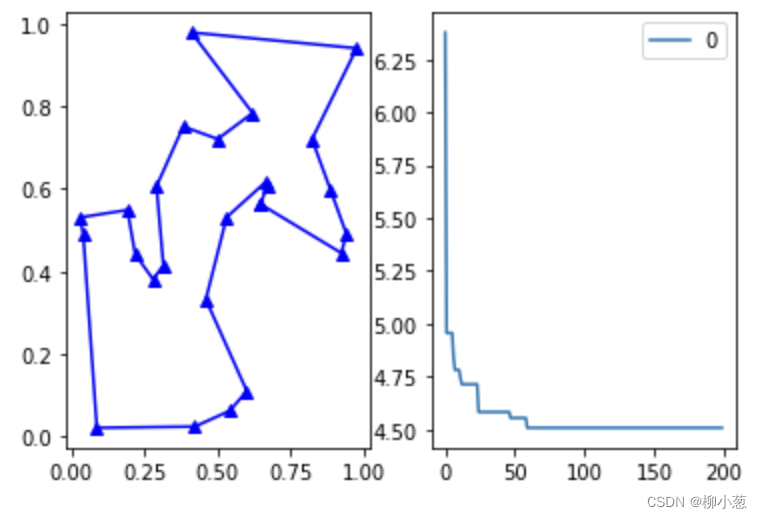

上图示意的是4 个包络,黄色的位置, 是两个电位重合在一起了, 这导致无法区分除它属于左边的电位还是右边的电位,引起误码。

4. PLC NAND 发展阻碍?

虽然PLC充满了浪漫的梦想,但现实是PLC SSD要想量产,难上青天。目前都没有一个清晰的量产时间表。

不是说单个存储元存的 bit 数越多越好吗, 这么好的研究成果为啥不能发展起来呢?

其实不然, 千鸟在林不如一鸟在手。再好的东西, 要有相应的技术来实现量产才行。不然就只能束之高阁。

3D XPoint 内存 就是因为成本居高不小,被束之高阁。 赢得了性能,跑输了市场。

新的PLC NAND 闪存, 需要有闪存控制器来支援。

目前业内尚未有控制器公司对外宣称可以支持PLC NAND。市场上当前主流的SSD控制器主要都是基于ARM Cortex-R8 Core,提供4K LDPC ECC纠错能力。可预见的是QLC 的RBER 会显著升高,需要主控有更高的纠错能力,需要更强大的 ARM 处理器支持实时高速运算,目前还没有量产。

灵魂三问?

PLC 增加延迟体现在最终产品速度上, 用户是否可以接受?

PLC相应的工艺和匹配的技术复杂也更加严苛,最终降低成本能真有多少?

PLC 的可靠些如何, 使用寿命?

这些在没有大规模量产之前, 都没有可参考的数据,也谈不上是否能接受?

PLC NAND 没有支持控制器的支持以及看得见的收益,PLC NAND的普及还路漫漫。

所以,PLC SSD的未来还充满悬念? 是雪藏襁褓还是石破天惊,静待时光的答案吧?

当下看来, PLC 的普及或多或少有蛮大阻碍。

新生事物总是寄于期盼,未来可期。如果克服了一些痛点,未来我们再看它的时候,就要刮目相看了。

————————————————

参考:

https://memory-logger.blog.csdn.net/article/details/126879185

https://baijiahao.baidu.com/s?id=1670800477494165014&wfr=spider&for=pc