一、任务

设计一个二级运放,第一级为有源负载差动对(五管OTA),第二级为电流源负载的共源极。

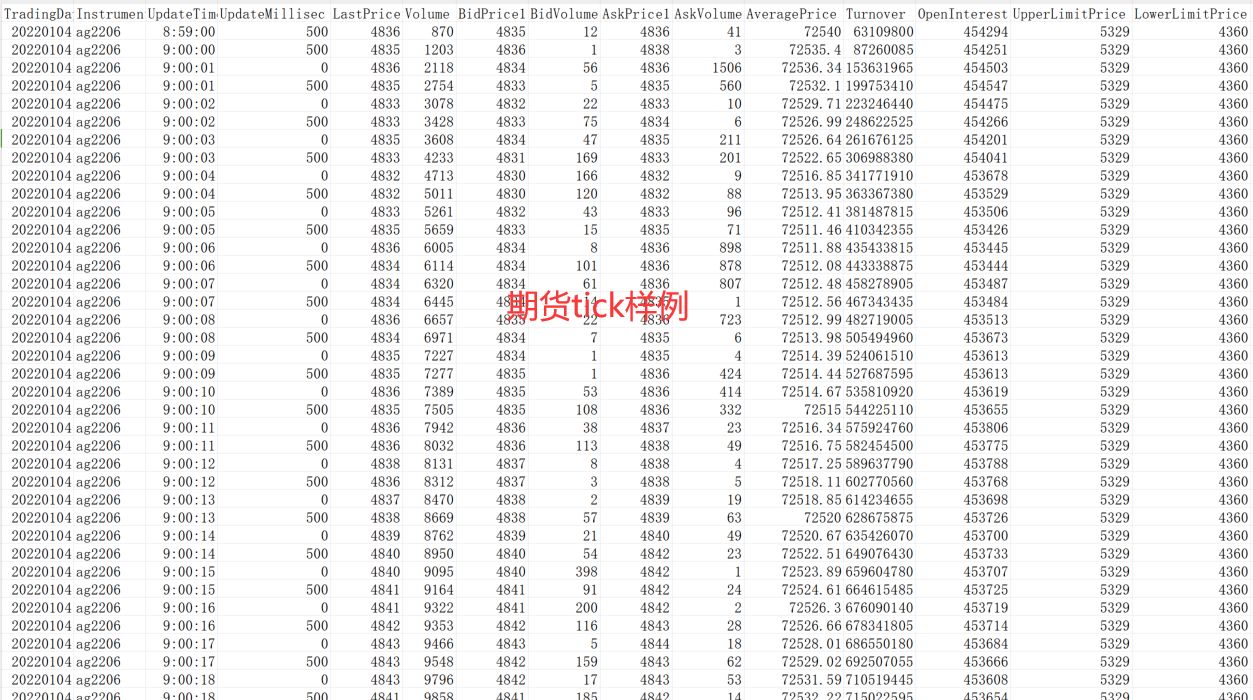

二、参数指标

| GBW | ≥50MHz |

| |Av| | ≥80dB |

| PM | 60°~70° |

| SR | ≥50V/us |

| 10pF |

本文使用smic13mmrf_1233工艺库进行设计。

三、电路设计

(一)原理图

(二)密勒补偿

对于一级运放来说,其可以看成是单极点系统,相移不会大于90°,不需要考虑相位裕度。

但对于两级运放,其相移是会达到180°的,在设计时需要考虑相位裕度。

对于频率补偿,我们可以增加负载电容,使主极点的频率

降低。由此,本文引入了密勒补偿。

密勒补偿以一个中等的密勒电容建立了一个低频极点。根据设计经验,若相位裕度取值为60°,

取值为0.25到0.5倍

。

【引入密勒补偿还有一个问题需要解决,就是系统频率响应的零点,这个零点会导致更大的相移,同时幅频特性曲线会出现+20dB/dec的变化(属于右半平面的零点,对反馈系统的稳定性更加有害,因为它提高增益,但延迟相位)】

零极点影响,可以看我这个博客:

运放零极点对幅频特性、相频特性曲线的影响-CSDN博客

由于引入密勒补偿电容后,出现了极点分裂现象。为了简化计算,我们使系统变成单极点系统(单极点近似)。

- 第一极点wp1左移,但它并没有消失,而是作为电路的主极点;

- 第二极点wp2右移,直至大于单位增益带宽wu,增益小于1后当它不存在了。

单极点近似要求,一般

取值为

的2~3倍。同时,

。

极点和结点的关联,可以看我这个博客:

极点和结点的关联-CSDN博客

对于以上值的取值,有以下的式子。其中,gm-in1和gm-in2分别代表第一级和第二级运放的输入管跨导,是整个运放的负载电容(也是第二级运放的负载电容),

为与密勒补偿电容串联的电阻(将零点移至左平面,并抵消第一非主极点)。

第二极点(第一非主极点):

单位增益带宽:

零点:

的取值:

, 解得:

极点和结点的关联-CSDN博客

计算一下跨导的取值,这里选取最低限度的取值,也就是理论上相位裕度是60°,但实际上可能达不到。

令 ,

可得:

在最低限度下,第二级输入管的跨导是第一级的8倍,在实际设计时,最好取10或以上才能有一定裕度。

(三)确定第一级输入对管M1和M2的尺寸

注:本文管子序号均按照上图中的编号

注:下面对n管和p管扫描时并联数均设为4

考虑寄生电容对负载电容的影响。指标要求负载电容为10pF,根据设计经验,加上寄生参数后,一般取1.2

也就是12pF做计算。

此时,密勒补偿电容Cc大约在3pF到6pF之间(一般取不到6pF那么大)。一般的文献或方法会教直接用Cc作为GBW公式中的CL,但是我们最好加上一点第一级输出和第二级输入的寄生电容。所以第一级运放的负载电容取值6pF时留有的裕度会比较大。由得到的

可以利用GBW得到输入对管的跨导,有以下式子:

因为

可得

对增益Av进行解算。整体的增益是10000,那就令每一级增益为100,这就要求晶体管的自身增益大于200。

同时,为了让压摆率满足50V/us的需求,gm/id就不能取太大,以此来保证电流不会太小,这里gm/id取值为12。

观察晶体管的self_gain - gmoverid曲线,找出在gm/id=12时,哪个沟道长度L下的增益大于200。最终确定L=550nm。

再观察id/w - gmoverid曲线,得到gm/id取值为12,L=550nm下的电流密度。

至此,M1和M2的W就可以确定:

因为: ,

可得:

又因为:

所以:

(四)确定第一级负载管M3和M4的尺寸

和前面一样,选取gm/id=8,self_gain大于200时沟道长度L=950nm。

再观察id/w - gmoverid曲线,得到gm/id取值为8,L=950nm下的电流密度。

至此,M3和M4的W就可以确定:

因为

又因为

所以

(五)对第一级放大电路进行初步仿真

设置第一级电流源电流为314uA,负载电容为5pF:

在ADE_L的setup中的配置AVDD,AGND,Vin+和Vin-:

在Results中的Direct Plot中点击AC gain&phase,得到如下波特图:

从波特图中,我们可以看到第一级放大电路的低频增益为50.093dB,GBW为109.139MHz(快捷键H创建一个横向光标)。

因为

解得:

【这意味着后面的密勒电容在第一级GBW为109.139MHz时,最高可以取到2.75pF;若第一级GBW减少至指标50MHz,则最高可为6pF】

查看某个器件的直流工作点参数:

Results ——> Print ——> DC Operating points ——> 点击选中某个器件

(六)确定M6的尺寸

由图可知M6管的vgs为834.368mV。观察N-MOS晶体管的VGS-gmoverid曲线,看看对应的范围是多少。从图中看出,gmoverid的取值在9左右。

选取gm/id=9,self_gain大于200时沟道长度L=900nm。

根据前面分析, 为了二级运放具备一定的相位裕度,。

所以 ,

解得:

再观察id/w - gmoverid曲线,得到gm/id取值为9,L=900nm下的电流密度。

因为 ,

所以

代入,

,并联数mul为4后,M6管未能进入饱和区,vds很小。

减小宽长比可以提高vds,这里将L调大,其他参数保持不变,管子M6很好地进入了饱和区。为了留有一定裕度,使vds比过驱动电压再多大一些,根据饱和区管子的输出阻抗

正比于

调大L为1.41um时,M6管的vds很好地满足了要求。

(七)仿真测试

仿真得到增益和相位的频率特性曲线。

由于第二级输入管M6的跨导未达到第一级输入对管M1,M2跨导的倍(下次计算可以按照第一级输入对管跨导的11倍12倍来计算第二级输入管的跨导,留有一定的裕度。)

so,刚开始相位裕度没能达到60°,这里增加一个调零电阻R跟密勒电容串联,用来调整零点位置来抵消第一非主极点的作用。

从图中得出,GBW=85.6441MHz,Av=100.19dB,PM=180°-115.092°=64.908°

下面进行压摆率的测试:

- 当M2管输入正的阶跃信号时,直接使得M2截止,此时电流几乎全部往M1流,M3和M4构成电流镜,M4也会流过尾电流源M5等量的电流,但是此时M2截止,电流只有一个通路,就是往Cc流动,节点3的电压几乎不会变化【节点3电压变化比较小只在Ids7比Ids5大很多的时候才成立,即当Ids7的电流能够同时带动负载电容和米勒补偿电容且有较大的余量时节点3的电压变化才可以忽略(电路的最大压摆率受限于Cc)】,因此电路的SR为Ids5/Cc,但是我们还是需要考虑到M7是偏置住的(即能流过的最大电流有限),因此还需要考虑M7流过的最大电流能不能以Ids5/Cc的摆率将负载电容CL电压同时拉上去,所以就有了设计教程中的外部摆率(Ids7-Ids5)/CL。最后得到的摆率SR=min{Ids5/Cc,(Ids7-Ids5)/CL}。

- 而当输入接入一个负的阶跃信号时,M1截止M2导通,但是此时M6能够通过的电流是受到M4漏级控制的,所以其摆率SR=Ids5/Cc。

- 虽然理论分析确实如 1、 2 所示,但是我们在许多参考书上都可以看到二级运放的摆率SR=Iss/Cc,这是因为就上图这种没有控制零点的二级运放,为了满足相位裕度,需要使得零点远离单位增益处。(按照波特图绘制那么理解一般零点远离单位增益处10倍,零点对单位增益处的相位影响较小),同时为了60°以上的相位裕度,可以得到第二级M6管子的跨导gm6>=10gm2,密勒补偿电容Cc≥0.22CL。

压摆率测试电路

由仿真输出波形,可以得到

所以压摆率SR为47.5V/us, 与指标50V/us差一点。(可以增大电流,即取gm/id较小点的值来增大压摆率SR使其满足要求。)

四、总结

| 设计值 | 指标 | |

| GBW | ≈85.6MHz | ≥50MHz |

| |Av| | ≈100.2dB | ≥80dB |

| PM | ≈64.9° | 60°~70° |

| SR | ≈47.5V/us | ≥50V/us |

| 10pF | 10pF |

五、后话:

声明:本文仅供个人学习交流,无任何商业行为。

参考文章链接

链接一:

用Cadence Virtuoso IC617结合gm/id方法设计两级运放(五管OTA加共源极)_virtuoso波形图放大-CSDN博客

链接二:

二级运放压摆率分析(SR)_压摆率仿真-CSDN博客