1 SPI外设简介

STM32内部集成了硬件SPI收发电路,可以由硬件自动执行时钟生成、数据收发等功能,减轻CPU的负担

可配置8位/16位数据帧、高位先行/低位先行

时钟频率: fPCLK / (2, 4, 8, 16, 32, 64, 128, 256)

支持多主机模型、主或从操作

可精简为半双工/单工通信

支持DMA

兼容I2S协议

STM32F103C8T6 硬件SPI资源:SPI1、SPI2

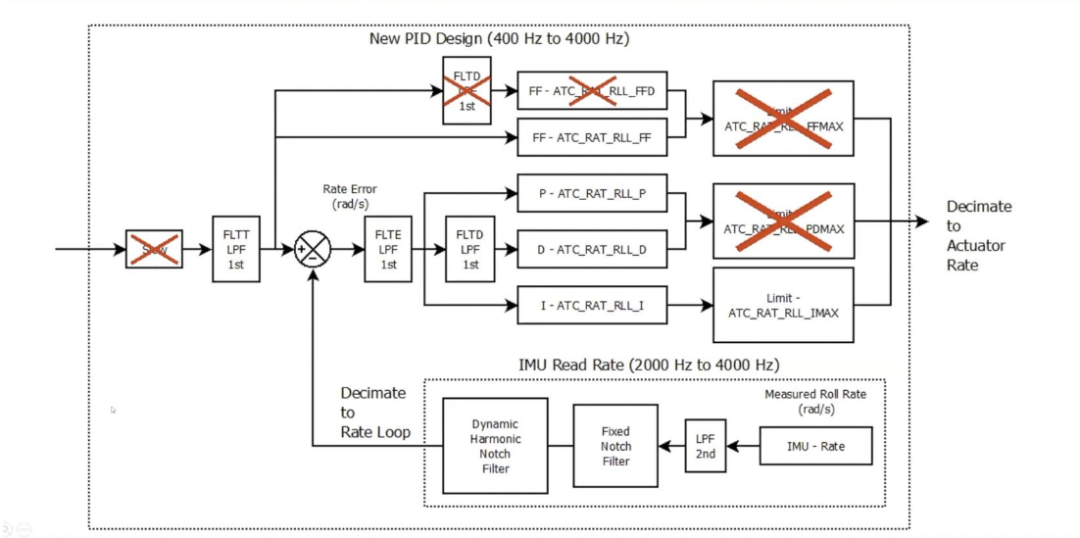

2 SPI框图

左上角为数据寄存器和移位寄存器打配合的过程,实现连续的数据流。右下角为控制逻辑。

左上的核心部分为移位寄存器,右边的数据低位一位一位从MOSI移出去,MISO的数据一位一位的移入到左边的数据高位(数据右移,低位先行,LSBFIRST控制位可以控制低位先行或高位先行)。两个缓冲区就是数据寄存器DR,发送缓存区为发送数据寄存器TDR,接收缓冲区为接受数据寄存器RDR。若要连续发送一批数据,第一个数据写入到TDR,当移位寄存器没有数据移位时TDR的数据会立刻转入移位寄存器开始移位,转入时刻会置状态寄存器的TXE为1表示发送寄存器为空,当TXE置1后下一个数据就可以提前写入到TDR里候着了,一旦上一个数据发完下一个数据就可以立即跟进,移位寄存器一旦有数据过来就会自动产生时钟将数据移出,在移出过程中MISO的数据也会移入,移入的数据会整体从移入寄存器到移入寄存器RDR,此时会置状态寄存器的RXNE为1表示接受寄存器非空,此时可以读出数据。

右下角为控制逻辑。波特率发生器主要产生SCK时钟,内部为一个分频器,输入时钟为PCLK(72M的SPI1和36M的SPI2),经过分频后输出到SCK引脚,每产生一个周期的时钟移入移出一个bit。右边CR1寄存器的三个位BR0、BR1、BR2用来控制分频系数。最后左下角有NSS