AI Infra 基础知识 - NVLink 入门

NVLink,一种专有互连硬件,实现Nvidia GPU与CPU之间的高效、一致数据和控制传输,提升多GPU系统性能。

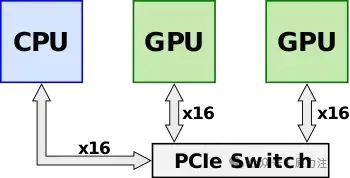

概述 NVLink 于 2014 年初发布,旨在作为 PCI Express 的替代解决方案,具有更高的带宽和附加功能(例如共享内存),专门设计用于与 Nvidia 自己的多 GPU 系统的 GPU ISA 兼容。在推出 NVLink 和 Pascal(例如Kepler)之前,多个 Nvidia 的 GPU 会位于共享的PCIe总线上。尽管已经可以使用 Nvidia 的统一虚拟寻址通过PCIe总线实现直接的 GPU-GPU 传输和访问,但随着数据集的大小不断增长,总线成为越来越大的系统瓶颈。通过使用PCIe 交换机,吞吐量可以进一步提高。

NVLink,一项旨在取代PCIe通道进行GPU间通信的技术,其独特之处在于,它设计用于实现带宽超过PCIe的CPU-GPU通信。尽管AMD和Intel在x86系统上实现NVLink的可能性不大,但IBM已与Nvidia联手,在其POWER微处理器上引入了NVLink支持。对于这些支持NVLink的微处理器,NVLink能够完全替代所有链路的PCIe,从而实现更高效、更快速的数据传输。这一创新技术将为高性能计算领域带来革命性的变革,让数据处理更加迅速、流畅。

链接

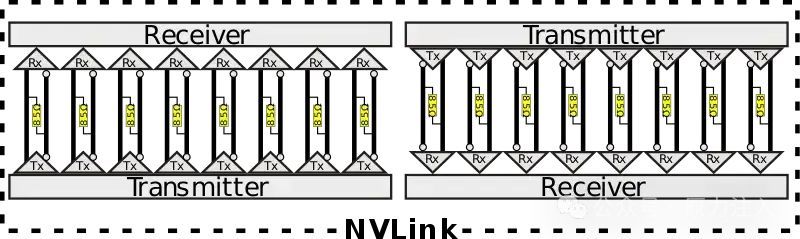

NVLink通道,被形象地称为"Brick"(或NVLink Brick)。每个NVLink都是双向接口,每个方向拥有8个差分对,合计32条线路。这些线路是直流耦合的,采用带有嵌入式时钟的85Ω差分终端。为了优化路由,NVLink支持通道反转和极性调整,这意味着两个设备间的物理通道顺序及其极性可以自由切换。

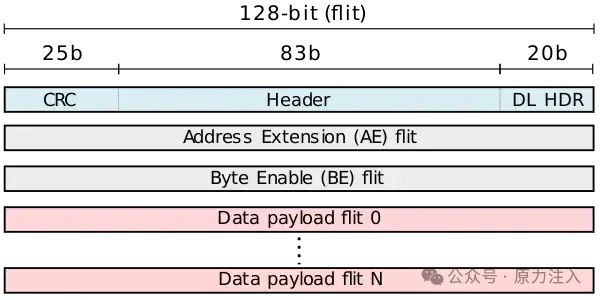

NVLink 数据包的尺寸在1至18个flit之间变化。每个flit包含128位,通过单个header flit和16个payload flit的组合,可传输256字节的数据,峰值效率高达94.12%。若采用单个header flit和4个data payload flit的组合,则可传输64字节的数据,单向效率为80%。然而,在双向流量中,这些效率会略微下降,分别为88.9%和66.7%。

数据包至少由一个标头构成,并可选择加入地址扩展(AE)、字节启用(BE)数据块,以及多达16个的数据负载块。典型的事务包括请求和响应,而发布操作则无需回应。

头部 flit

Header flit,拥有128位的宽度,由25位CRC、83位事务和20位数据链路(DL)层字段构成。其中,事务字段涵盖请求类型、地址、流控制及标签标识等关键信息;而数据链路字段则包含数据包长度、应用程序编号标签以及确认标识符等内容。

地址扩展 (AE) 数据块保留用于相当静态的位,并且通常仅传输变化的位。

纠错

Nvidia的误码率被精确设定为1/1×10 ^12,这一数字背后是其强大的错误检测技术。借助25位循环冗余校验头字段,我们能确保数据无误。接收器则负责将这些数据安全地存放在重放缓冲区中。当数据传输包按序到达并经过CRC校验确认无误后,发送端将收到确认信息。若超时未收到确认,系统将自动启动回复序列,重新传输所有后续数据包。

CRC字段由25位构建,确保数据包在最多有5个随机位出错的情况下仍可正常工作。对于差分对突发,该字段甚至能容忍多达25个连续位错误。CRC的计算基于报头和前一有效载荷,因此无需为数据有效载荷设置独立的CRC字段。值得注意的是,由于报头中包含了数据包长度信息,因此在CRC校验过程中也将其纳入考虑。

例如,有两个32字节的数据载荷flit和其相关的头部序列。下一个数据包会对当前的头部以及来自上一个事务的这两个数据载荷进行CRC校验。如果这是首个事务,则CRC会默认上一个事务为空事务。

以PCIe 2.0为例,其每秒可完成5GT的原始数据传输,采用8b/10b编码方式,即每10比特中只有8比特有效。换算下来,其有效带宽为4Gb/s,等效于500MByte/s。

NVLink 1.0

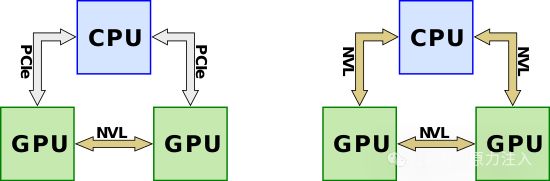

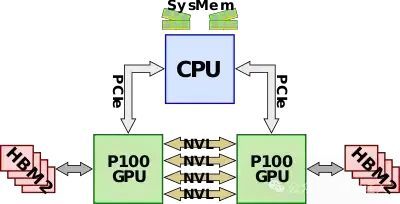

NVLink 1.0 最初是在基于Pascal微架构的P100 GPGPU中引入的。除了能够从 CPU 端访问系统内存外, P100还配备了自己的HBM内存。P100 有四个 NVLink,支持高达 20 GB/s 的双向带宽,即 40 GB/s,总聚合带宽为 160 GB/s。在最基本的配置中,除了连接到 CPU 以访问系统 DRAM 的 PCIe 通道外,所有四个链路都连接在两个 GPU 之间,以实现 160 GB/s 的 GPU-GPU带宽。

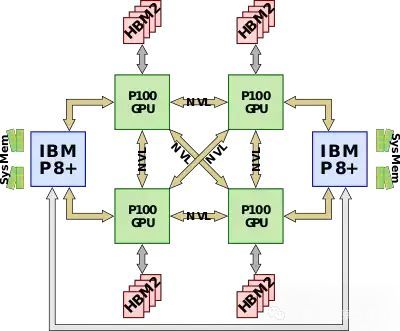

首款原生支持NVLink的CPU,IBM POWER8+,引领了一场技术革命。它通过NVLink互连技术,将CPU与速度缓慢的PCIe链路彻底告别。由于P100 GPU仅配备四个NVLink,因此我们巧妙地利用每个GPU的单个链路,实现了CPU与GPU之间的紧密连接。在典型的全配置节点中,我们可以看到两个强大的Power CPU与四个高性能的P100 GPU共同组成。这四个GPU之间完全相互连接,而第四个链路则延伸至CPU,形成了一个高效、协同的工作体系。

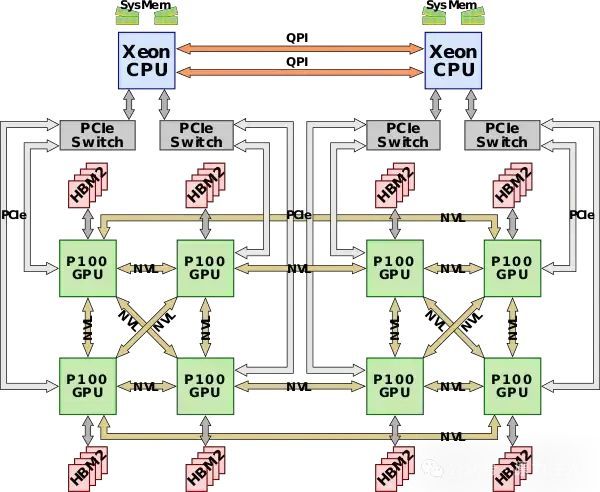

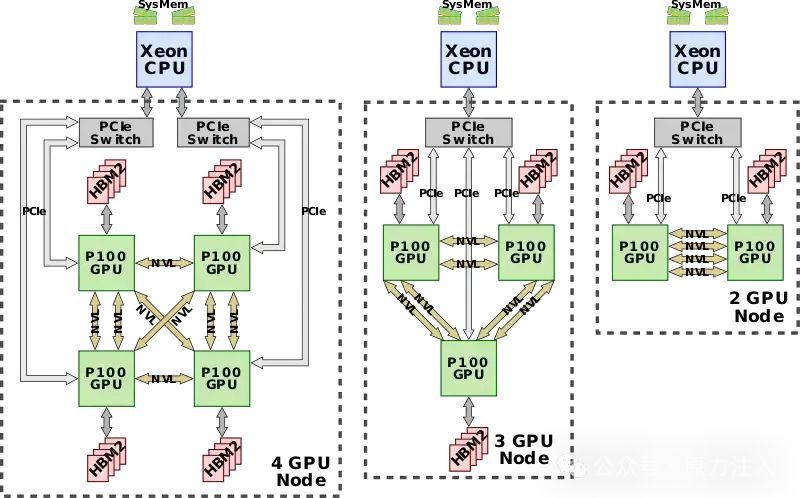

在Intel CPU的环境下,由于NVLink的不兼容性(且长期无望支持),P100 GPU的配置变化可能从两个增至四个。无论何种配置,所有GPU都完全互联,每两个GPU都通过一个直连CPU的PCIe交换机连接。值得注意的是,无论配置如何,每个连接都具有40GB/s的双向带宽。此外,这些链接可以聚合,以在任何两个GPU之间提供更高的带宽,使用链接越多,带宽越高。

DGX-1 配置

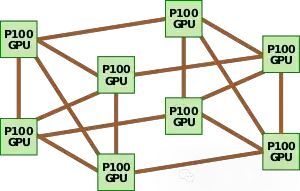

在2017年,NVIDIA引领科技潮流,推出了DGX-1系统,充分利用NVLink技术。这款DGX-1系统由8个Tesla P100 GPU和双插槽Xeon CPU精心打造,以混合立方体网格NVLink网络拓扑巧妙连接。两个Xeon处理器通过英特尔的QPI实现高效通信,而GPU则通过NVLink进行高速数据传输。这一创新组合,让DGX-1成为高性能计算的杰出代表。

NVLink 2.0

NVLink 2.0 最早是在基于Volta微架构的V100 GPGPU和IBM的POWER9中推出的。Nvidia 增加了 CPU 主控支持,允许 GPU 和 CPU 在平面地址空间中访问彼此的内存(即直接加载和存储)。平面地址空间通过新的地址转换服务得到支持。此外,还为 CPU 和 GPU 添加了对原子操作的本机支持。随着平面地址空间的增加,NVLink 现在具有缓存一致性支持,允许 CPU 高效缓存 GPU 内存,显著改善延迟并提高性能。NVLink 2.0 将信令速率提高到每线 25 Gbps(25 GT/s),实现 50 GB/s 双向带宽。V100 还将片上 NVLink 的数量增加到 6 个,总聚合带宽为 300 GB/s。值得注意的是,还添加了额外的省电功能,例如在空闲期间停用通道。

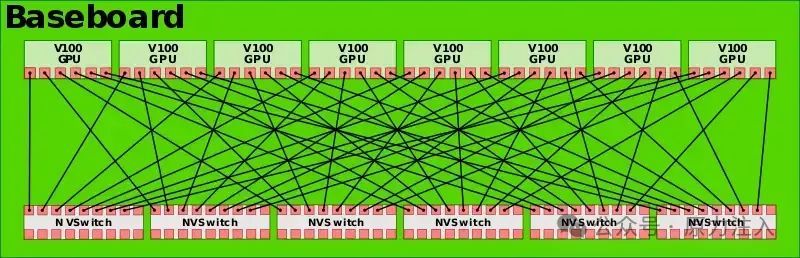

NVLink 2.0 首次亮相于第二代DGX-1,但其全面的拓扑结构优化则在DGX-2中实现。Nvidia 还携手 DGX-2 推出了NVSwitch,这款拥有18个NVLink端口的交换机实力非凡。这款集成了20亿晶体管的交换机,能够实现从9个端口到其他任一端口的流量路由。每个端口提供高达50 GB/s的传输速率,使得整个交换机能够提供惊人的900 GB/s带宽。

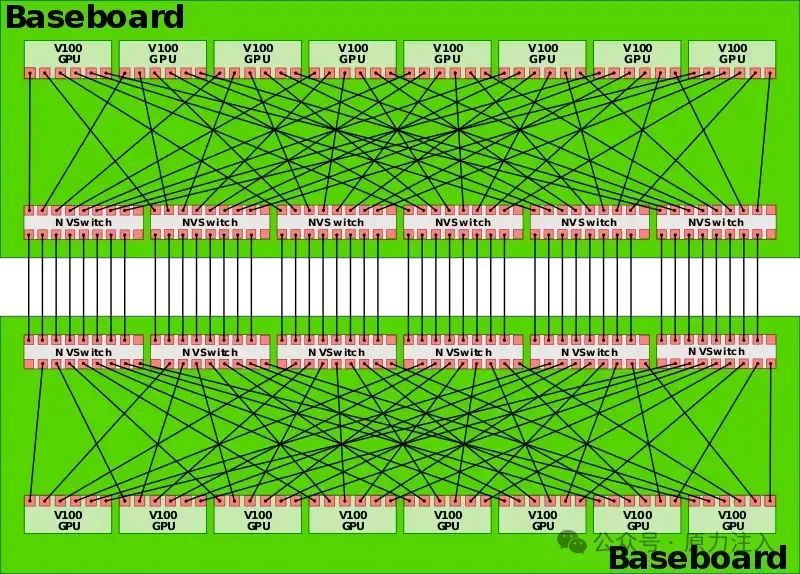

DGX-2,Nvidia的杰作,通过六个NVSwitches将八个GPU完全互连。每个GPU都可与同一块底板上的其他七个GPU无缝对接,实现卓越的性能和效率。

然后将两个底板相互连接,以将所有 16 个 GPU 完全连接在一起。

NVLink 3.0

首次亮相的NVLink 3.0,基于Ampere微架构的A100 GPGPU中引入。它引领技术新潮,以50 Gbps的信号速率,彰显无与伦比的速度优势。

-对此,您有什么看法见解?-

-欢迎在评论区留言探讨和分享。-