【综合】数字IC设计需要考虑的时序参数;Race Hazard;同步系统时序要求;建立时间、保持时间;偏斜;抖动;毛刺、竞争冒险;亚稳态

- 数字设计时需要考虑的时序参数

- 传播延迟 propagation delay, 上升时间 rising time,下降时间 fall time

- 建立时间 setup time , 保持时间 hold time

- setup time violation 违例, hold time violation违例

- 时钟偏斜 Clock skew

- 同步系统 Synchronous System

- 时钟抖动 jitter

- 毛刺 glitch

- 竞争冒险 Race Hazard

- 组合逻辑电路中的竞争冒险

- 时序逻辑电路中的竞争冒险

- SystemVerilog非阻塞赋值可以避免阻塞赋值时的不确定性造成的race condition

- 亚稳态 metastability ——一种不平衡的状态

数字设计时需要考虑的时序参数

hold time violation 和 setup time violation 意味着电路设计不能满足时序要求!而race hazard意味着您编写的代码经过综合后实施到真实的电路上时会导致某些状态不确定。这种不确定不稳定的状态称作是亚稳态(Metastability)。

同步系统中要求数据Data必须在下一个时钟上升沿之前稳定,保证寄存器可以取到正确的值。

传播延迟 propagation delay, 上升时间 rising time,下降时间 fall time

这三个参数都算是如反相器等器件从输入到输出传递信号的参数,是元件自带的参数。Transition is the time it takes for the pin to change state.

- 上升时间 (tr) 是转换期间输出从最大值的 10%切换到 90% 的时间。

- 下降时间 (tf) 是转换期间输出从最大值的 90%切换到 10% 的时间。(有的工厂会设置为30-70%)

- 传播延迟(t propagation delay)通常在输入输出切换的50%点计算。高到低的传播延迟 (t pHL ) 是在输入从低到高切换之后,输出从高到低切换时的延迟。

建立时间 setup time , 保持时间 hold time

对于D触发器的当前待传输的数据,相对于时钟取值的边缘来说,必须早来setup time晚走hold time。

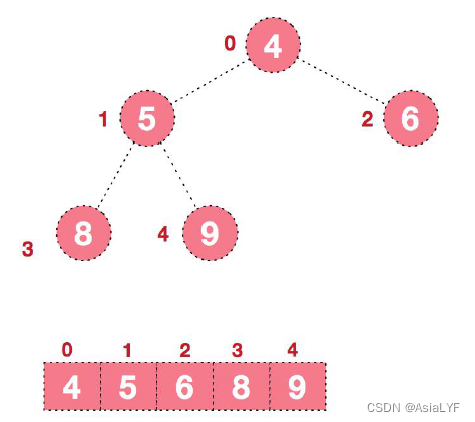

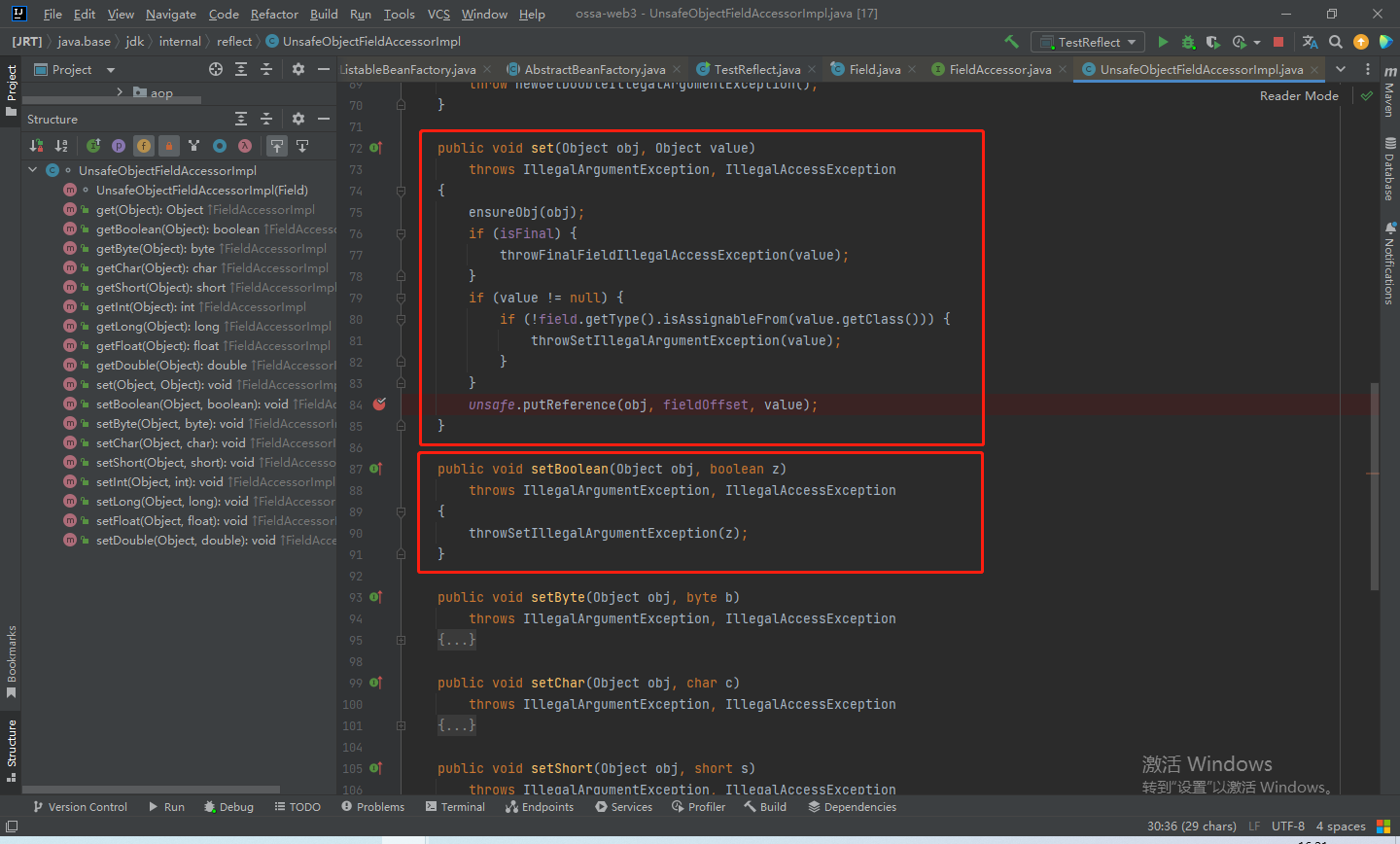

如上图所示:

- setup time是指在时钟上升沿之前,数据输入端信号必须保持稳定的最短时间。输入端的数据必须在时钟上升沿之前的一个小时间窗口内保持稳定,否则不能取到值;

- hold time是指在时钟上升沿之后,数据输入端信号必须保持稳定的最短时间。hold time时序检查确保新数据不会在触发器稳定输出初始数据之前,过早到达D端而下周期出现的新数据覆盖其初始数据;

- D触发器的时钟周期T,在时钟周期内可以正常提取D到Q,dcq代表clock to Q delay是触发器的延迟,故最小的时钟周期要求: T m i n i m u m = t s e t u p + d c q T_{minimum} = t_{setup}+d_{cq} Tminimum=tsetup+dcq;

- 如果数据在 tsu 中发生变化,则会导致setup time violation 违规,如果数据在 thd 中发生变化,则会导致hold time violation 违规;

建立时间(setup time)和保持时间(hold time)详析

From Process Variations to Reliability: A Survey of Timing of Digital Circuits in the Nanometer Era

setup time violation 违例, hold time violation违例

如果数据在 t s u t_{su} tsu中发生变化,则会导致设置违规,如果数据在 t h d t_{hd } thd中发生变化,则会导致保持违规。

-

如何解决setup time violation 违例:

解决setup time violation 违例的唯一方法是添加缓冲区,而不是减慢整个系统时钟。您不能通过减慢时钟来修复保持时间违规,您需要向路径添加缓冲区以确保它稍后转换并被下一个上升沿捕获,我们可以在最快路径中添加一些延迟以消除。 -

如何解决hold time violation违例:

减少时钟频率,增加时间周期。如果降低时钟频率,则可以修复设置违规。P.S. 我们不能让数据恰好在目标时钟的上升沿接近时到达,因为这会导致亚稳态。要修复保持时间违规,请在两个触发器之间添加额外的逻辑(通常是缓冲器)。这将延迟从一个 FF 到下一个 FF 的数据更改“在”满足下一个触发器的保持时间之后。如果您有设置违规,那么减慢时钟将使它工作。但是,如果你已经为设定的频率设计了电路,那么你需要从循环中移除一些逻辑并将其放在下一个或上一个循环中。

Iain McNally-Synchronous Design

VLSI placement-CMOS part 3

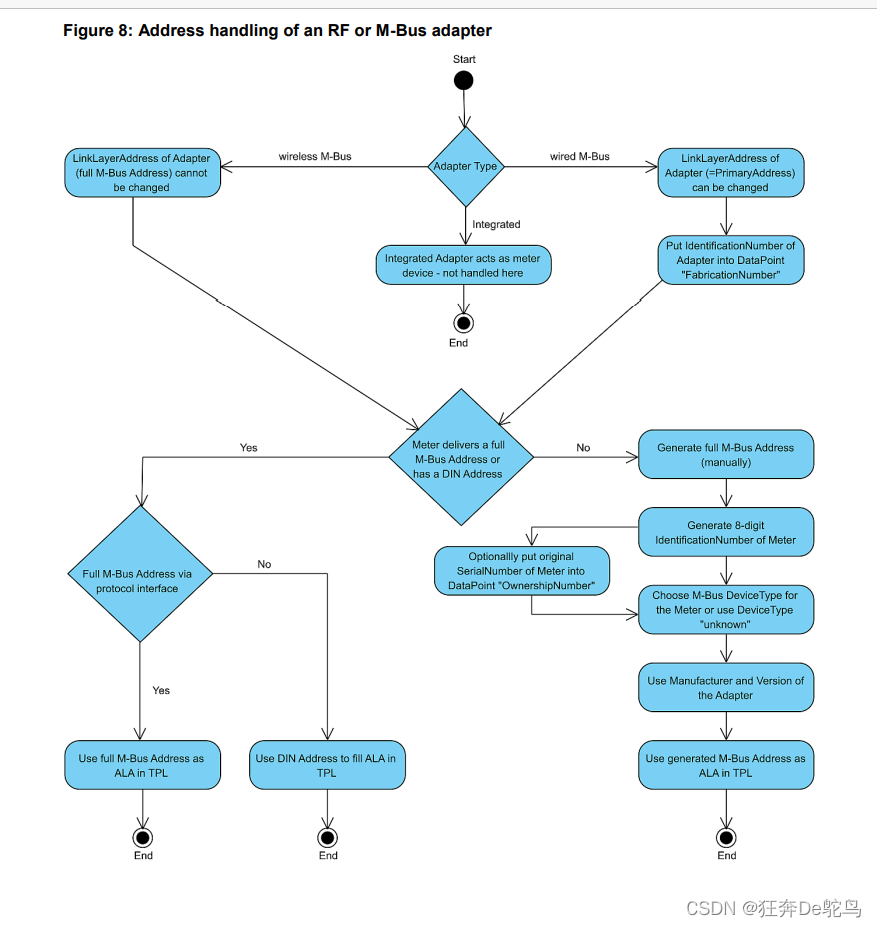

时钟偏斜 Clock skew

Clock skew——时钟经过不同的路径之后产生的相位上的偏差

- Clock Skew 是时钟信号到达两个触发器的时间差;

同步系统 Synchronous System

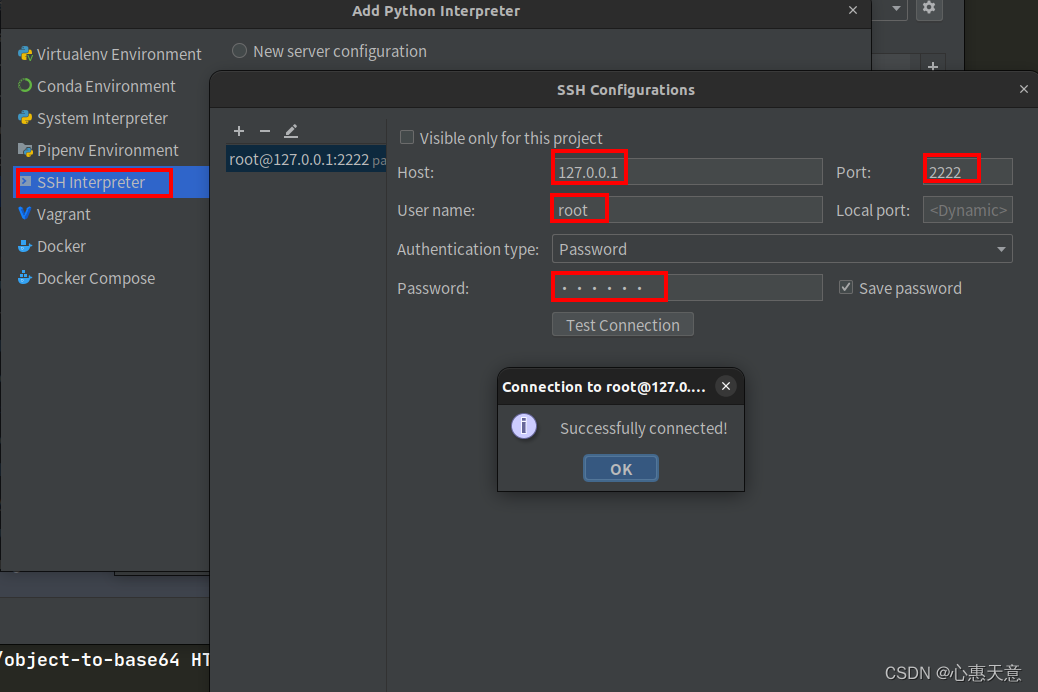

在Synchronous System系统里,只有同一个时钟,同步系统内Clock上不允许添加buffer,这样试图增加了clock skew使得Clock不是同一个了,变成了异步。

CTS (PART-II) (crosstalk and useful skew)

数据Data必须在下一个时钟上升沿之前稳定!

- 在当前时钟上升沿捕获的数据是由上一个触发器在前一个时钟边沿启动的,由于非阻塞赋值在上一个时钟周期末尾才开始赋值,再加上传播延迟的时间就必须保证数据Data在当前时钟边沿之前的建立时间是稳定的。

- 因此,遵守设置时间可确保在当前时钟沿可靠地捕获在前一个边沿发射的数据。换句话说,set up time确保了设计顺利过渡到下一个状态。

Iain McNally-Synchronous Design

Setup time

时钟抖动 jitter

- jitter 特指clock jitter,是时钟频率上的抖动,时钟抖动在同一个触发器上但时钟边沿的位置由于振荡器中的一些噪声而边沿移动。可能是由电磁干扰和噪声引起的。

jitter is the cycle-by-cycle variation in the arrival time of the clock.

毛刺 glitch

-

glitch指的是信号毛刺,是输出端出现的极小的不需要的脉冲。

-

glitches有可能是因为噪声或者传播延迟不匹配造成的,由于噪声影响的glitch可能经常发生。如下图所示串扰毛刺(glitch):

- 从同步系统的角度来考虑,在一定的程度上,设计的数字电路系统应该允许一些glitches存在的,这不应该影响D触发器取到正确的Data。在实际的芯片上如果没取到正确的数据,有可能是因为glitch引起的;

Crosstalk Analysis and Its Impact on Timing in 7nm Technology

Iain McNally-Synchronous Design

竞争冒险 Race Hazard

由于本科期间一直学的叫做“竞争冒险”,所以搞得我有些分不清“race”, “risk”(这个词可以等同于hazard), “hazard”这三个词。

- hold time violation 和 setup time violation 意味着电路设计不能满足时序要求!而race hazard意味着您编写的代码经过综合后实施到真实的电路上时会导致某些状态不确定。这种不确定不稳定的状态称作是亚稳态(Metastability)。

what is hazard in digital electronics | Types of hazards in digital electronics

- glitch和hazard不能互换使用,glitch是观察到的现象(如观察到的脉冲信号翻转),hazard是具体电路里的小缺陷(如延迟不匹配)。例如,我们说波形里发生了小glitch,而不是直接说发生了hazard。我们说存在hazard,这意味着我们肯定知道在某些条件下产生了这些glitches,并且我们知道这些race condition条件是什么。

组合逻辑电路中的竞争冒险

-

逻辑冒险(也称static hazard):组合逻辑电路中,某一个信号电平发生变化,到达门电路的时间不相同,导致瞬时干扰脉冲的现象。不同的路径延迟可能导致数据传到输出端节点存在抖动。

-

功能冒险(也称dynamic hazard):组合逻辑电路中,多个输入信号同时发生变化,因为时延到达门电路时间各不相同,导致瞬时干扰脉冲的现象。dynamic hazard不存在于两级传递的电路,存在于三级或三级以上不相等的信号路径上。通常由多级最小化中的因式分解不良引起,可通过去掉

Lecture 10 -hazard

组合逻辑中的 竞争冒险问题

Difference between Static and Dynamic Hazard

P.S. 锁存器的最大缺陷倒不是毛刺,而是捕获瞬间出现的异常状态并锁存,导致实际输出难以预料

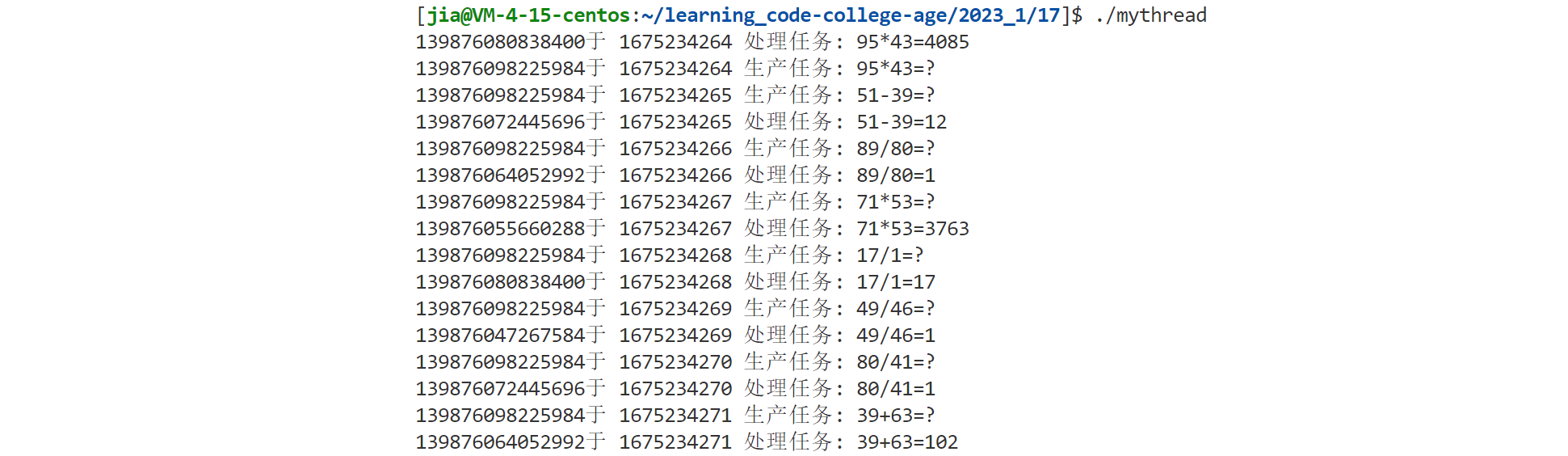

时序逻辑电路中的竞争冒险

System Timing - Clock Race Conditions

- 当输入到寄存器的数据不符合设置和保持时间约束时发生race conditions。

数据到达 Reg B 较晚,保留旧数据而不是锁存新数据。

- Clock skew can cause race conditions,时序不佳可能导致竞争条件,门级模型在仿真运行期间每个时钟周期报告数百个保持时间违规。

Introduction to CMOS VLSI Design Lecture 1: Circuits & Layout David Harris

SystemVerilog非阻塞赋值可以避免阻塞赋值时的不确定性造成的race condition

-

阻塞分配的执行可以看作是一步过程,在不中断任何其他 Verilog 语句的情况下评估 RHS 并更新阻塞分配的 LHS;

-

非阻塞赋值在时间开始时评估非阻塞语句的 RHS 端,并安排 LHS 更新在时间步结束时发生;

-

Nonoverlapping clocks can prevent races – As long as nonoverlap exceeds clock skew;

Blocking, Nonblocking Assignments and Verilog Race Condition

亚稳态 metastability ——一种不平衡的状态

亚稳态是指数字块/电路处于不稳定平衡状态的状态。也就是说,电路将无法稳定到稳定的 0/1,而是介于 0/1 之间。

pic From Wikimedia Commons

-

每当任何触发器中存在建立时间和保持时间违规时,它都会进入其输出不可预测的状态:这种状态称为亚稳态(准稳态);在亚稳态结束时,触发器稳定为“1”或“0”。整个过程称为亚稳态。

-

在触发器的设置时间内,输入到触发器的数据已从低电平变为高电平。这导致输出是亚稳态的。输出在一段时间内是亚稳态的,之后稳定为 0 或 1。但是我们仍然不知道输出结束于哪个状态。有时它可能是 0,其他时候可能会出现这种情况是 1。同样,这不是期望的行为。

如何降低同步系统中的亚稳态失效的可能性?

- 降低时钟频率

- 降低数据速度

- 使用更快的触发器

由于本文没讨论异步,故异步系统下的亚稳态产生与分析没列举。

亚稳态专题(亚稳态的概念、亚稳态的产生、亚稳态的后果、以及如何避免亚稳态)

静态时序分析(STA)基础知识-STA和动态时序分析比较、单元传播延迟、slew/transition time、时钟偏斜skew、时钟抖动jitter、最小最大时序路径、同步时钟、异步时钟、时钟域

DC综合之时序约束

![[Lua实战]Skynet-2.如何启动(Win10-WSL环境Ubuntu18.04)[开箱可用]](https://img-blog.csdnimg.cn/8bb6a88778c547e68736987ed94e7d13.png)