引言

此文针对 XILINX的用户指南 UG761进行学习简单对AXI作说明。从下篇文章开始,通过阅读ARM官网的AXI协议标准进行系统学习。可以持续关注~

AXI是什么?

AXI是ARM AMBA的一部分,ARM AMBA是1996年首次引入的一系列微控制器总线。

AXI的第一个版本首次包含在2003年发布的AMBA 3.0中。AMBA 4.0,发布于2010年,包括AXI的第二个版本AXI4。

有三种类型的 AXI4接口:

- AXI4——针对高性能存储器映射的需求;

- AXI4-Lite——针对简单、低数据吞吐量的存储器映射通信(例如写入和读取控制、状态寄存器);

- AXI4-Stream——针对高速数据流;

AXI4的优势(对于XILINX FPGA)?

•灵活性——为应用程序提供正确的协议:

AXI4用于内存映射接口,只需一个地址相位,即可实现多达256个数据传输周期的突发。

AXI4-Lite是一个轻量级的单事务内存映射接口。它的逻辑占地面积很小,是一个简单的界面,无论在设计还是使用上都可以使用。

AXI4流完全消除了对地址阶段的要求,并允许无限的数据突发大小。AXI4流接口和传输没有地址阶段,因此不被认为是内存映射的。

•可用性——通过转向行业标准,还可以访问全球ARM合作伙伴社区。

许多IP提供商支持AXI协议。

第三方AXI工具供应商的强大集合可提供各种验证、系统开发和性能表征工具。当您开始开发基于AXI的高性能系统时,这些工具的可用性至关重要。

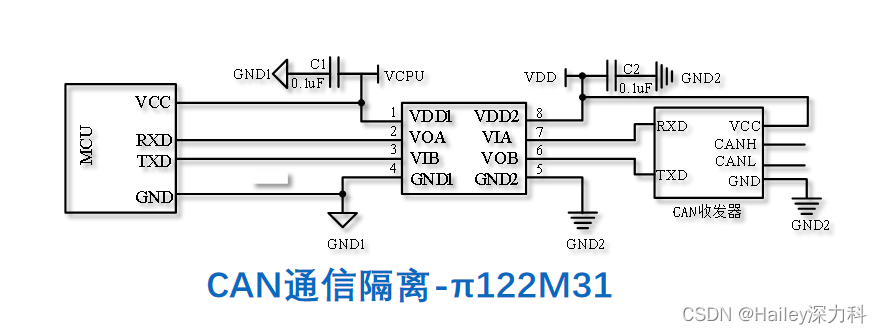

AXI如何工作?

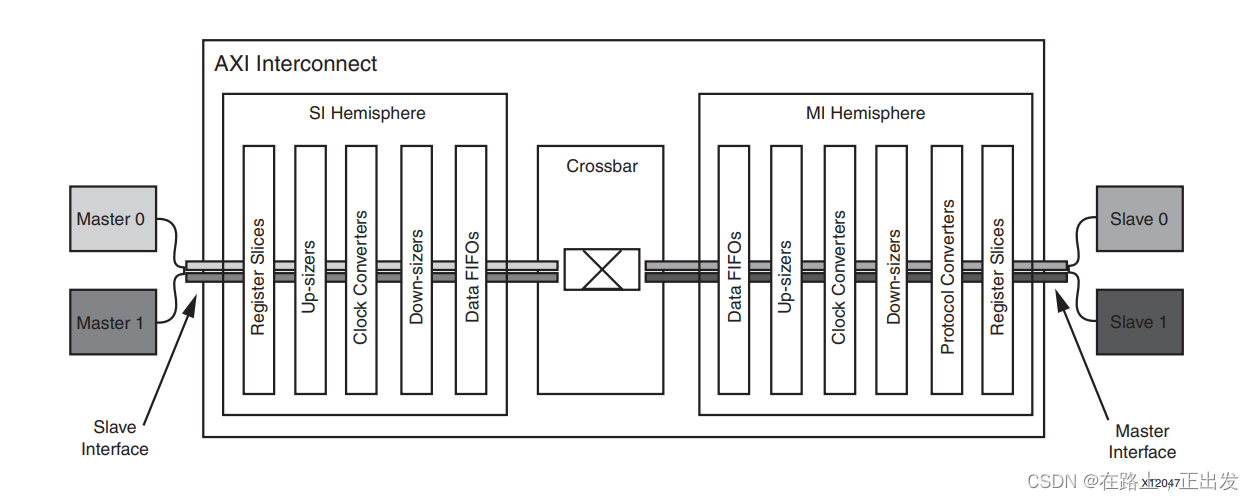

AXI4和AXI4-Lite接口都由5种通道组成:

- 读地址通道

- 写地址通道

- 读数据通道

- 写数据通道

- 写响应通道

数据可以在主侧/从侧设备之间同时双向流通(全双工),数据传输尺寸可以变化。AXI4的限制是突发传输的数据个数最大为256,AXI4-Lite仅允许一次传输事务传输一个数据。

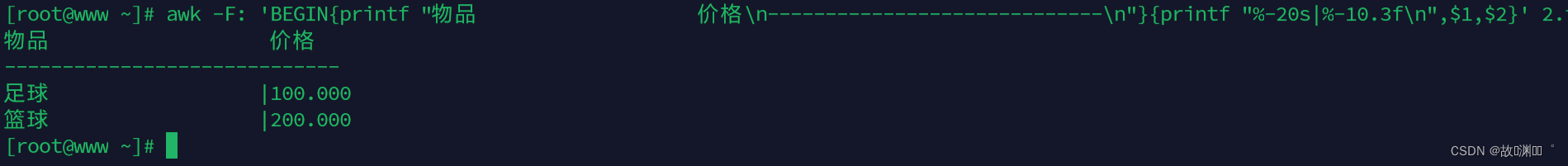

读通道架构

写通道架构

AXI4为读和写分别提供了独立的数据和地址通道连接。这就允许了同时的双向数据传输。

AXI-Stream接口可以突发传输无限长度的数据,但是其不支持数据的重排顺序。

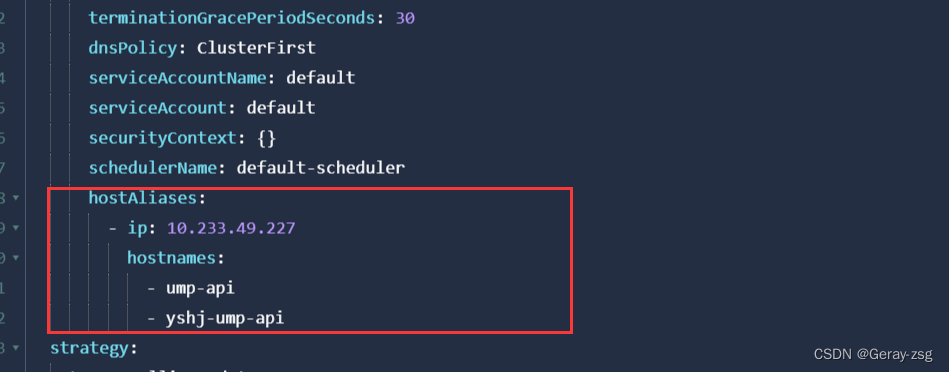

AXI互联的顶层结构

参考说明

【1】AXI Reference Guide