1.2.2存储结构:Cache--高速缓存

- Cache--高速缓存(相联存储器)

- Cache特点

- Cache改善系统性能局部性原理

Cache–高速缓存(相联存储器)

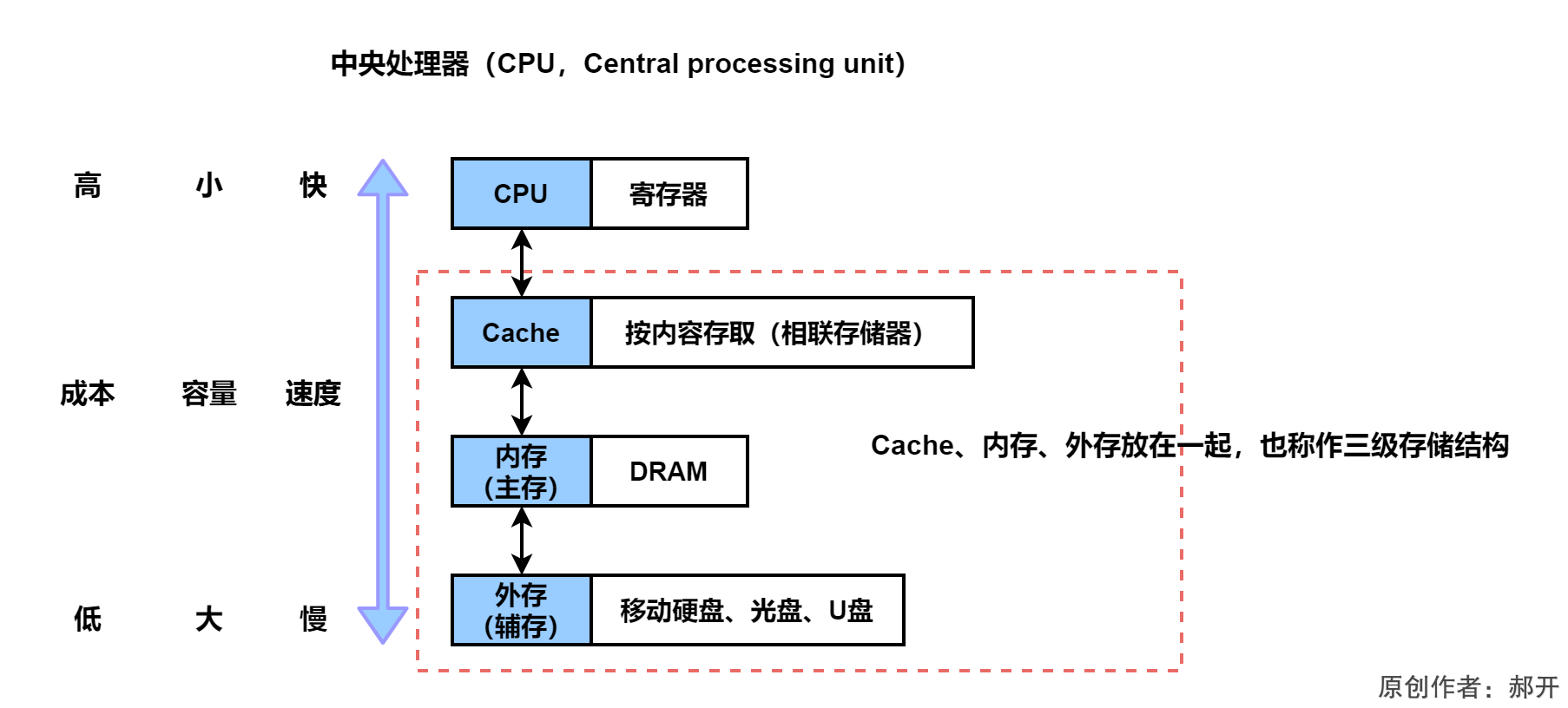

CPU中的寄存器和内存对比的话,其容量和速度差距是非常大的,因此在这种速度容量不匹配的情况下,在二者之间插入了一个折中的存储器,速度和容量是二者折中,从而解决CPU和内存速度容量不匹配的问题,这就是Cache的来源。

Cache也叫做高速缓存,我们目前在软考体系中,缓存只了解CPU和内存之间的缓存。而每一级结构或者每两级及结构都是可以去插入一个缓存的,但是目前考试所涉及的一般指CPU和内存之间的缓存——高速缓存,大小级别和主存不能比,主存目前主流的是16G,而Cache的单位是M。

Cache特点

- Cache的功能:提高CPU数据输入输出的效率,突破冯·诺依曼瓶颈,即CPU与存储系统间数据传送带宽限制。

- 在计算机的存储系统体系中,Cache访问速度最快的层次(是除了寄存器之外最快的,而寄存器划分在CPU里,因此单提到存储系统体系,Cache是最快的)。

- Cache对程序员来说是透明的,Cache相关的一些地址、映射关系都是由硬件直接完成的,与程序员无关。

- 使用Cache改善系统性能的依据是程序的局部性原理,包括时间局部性和空间局部性

Cache改善系统性能局部性原理

- 时间局部性:指程序中的某条指令一旦执行,不久以后该指令可能再次执行,典型原因是由于程序中存在着大量的循环操作

- 空间局部性:指一旦程序访问了某个存储单元,不久以后,其附近的存储单元也将被访问,即程序在一段时间内所访问的地址可能集中在一定的范围内,其典型情况是程序顺序执行。比如读取连续的数组A1,将所有数组读到Cache中,然后你下一步操作可能是读取A2,这样就不需要再次从内存中获取数据,而是直接在Cache中读取,速度会比内存快

- 工作集理论:工作集是进程运行时被频繁访问的页面集合

如果以h代表对Cache的访问命中率,t1表示Cache的周期事件,t2表示主存储器周期时间,以读操作为例,使用“Cache+主存储器”的系统的平均周期为t3,则:

t

3

=

h

×

t

1

+

(

1

−

h

)

×

t

2

t3=h×t1+(1-h)×t2

t3=h×t1+(1−h)×t2

其中,(1-h)又称为失效率(未命中率)。

Cache的访问命中率一般在90%以上,Cache的访问命中率与Cache的替换算法有关系,这里容易误导,

比如说算法的时间复杂度是影响Cache命中率的主要原因,这句话是不对的

时间复杂度最多是影响时间效率,而关键原因是Cache的替换算法,而不是它其中的某一项,可能是很多项。

比如追女生,把你拒绝了,它拒绝的是你这个人,换一个不同身高的可能答应了,换一个不同发型的也可能答应了,所以这个结果不是说身高和发型导致的,是人的问题,不能说是某个因素的问题。

![[JavaWeb]CSS](https://img-blog.csdnimg.cn/88cda11f0b6044f8a343076b8389492a.png?)