数据通路(下)

- 1. PC 寄存器的实现

- 2. 读写数据所需要的译码器

- 3. 数据通路完整实现

- 4. 总结

- 参考

1. PC 寄存器的实现

PC 寄存器又名程序计数器(Program Counter)。

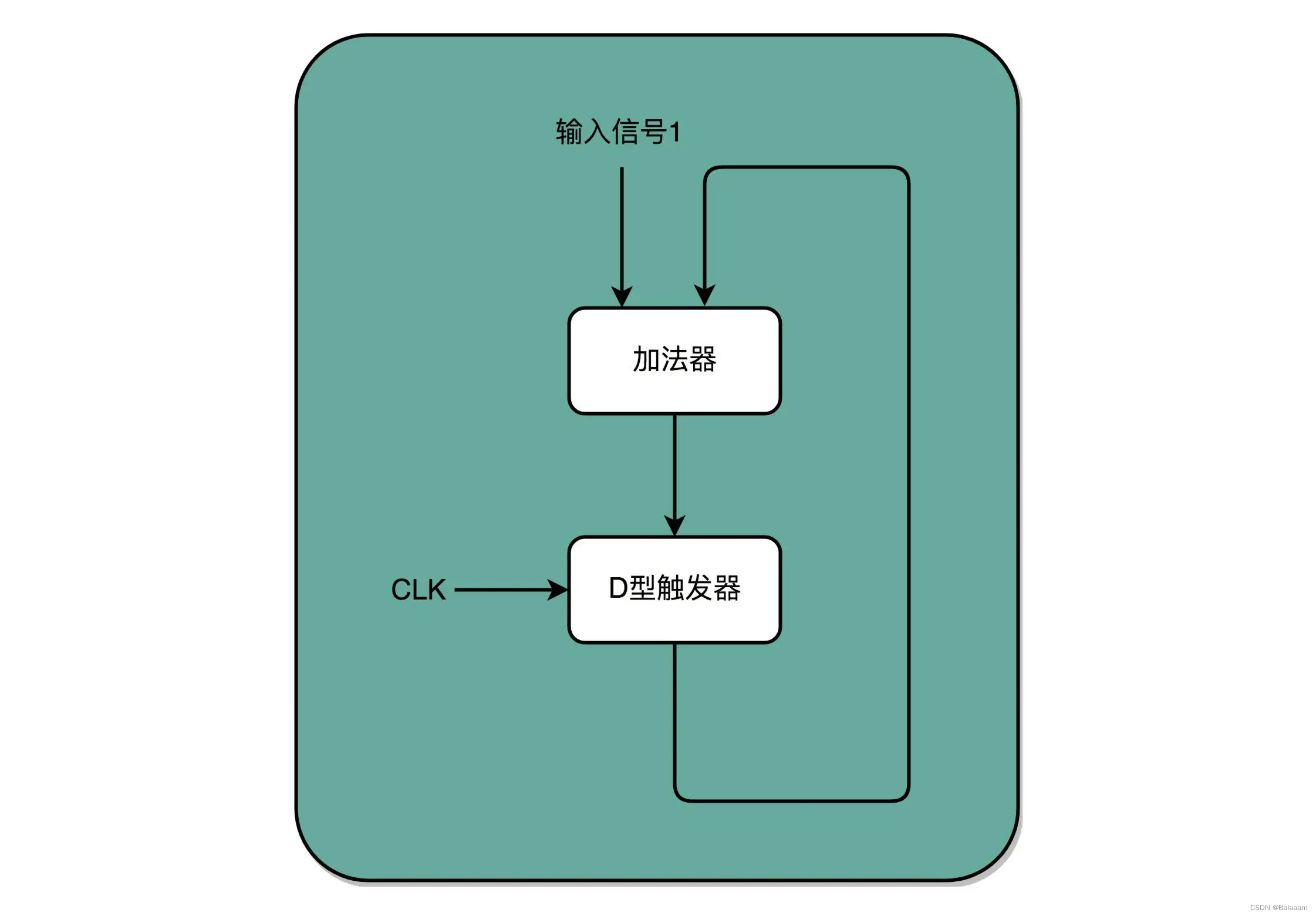

PC 寄存器由两个部分组成:

- 时钟信号。提供定时的输入;

- D 型触发器。我们可以在时钟信号控制的时间点写入数据。

加法器的两个输入,一个始终设置为 1,另外一个来自一个 D 型触发器 A。我们把加法器的输出结果写到这个 D 型触发器 A 里面。于是,D 型触发器里面的数据就会固定的时钟信号为 1 的时候更新一次。

每次自增之后,可以去对应的 D 型触发器里面取值,这也是我们下一条需要运行指令的地址。同一个程序的指令应该要顺序地存放在内存里面。这里就和前面对应上了,顺序地存放指令,就是为了通过程序计数器就能定时地不断执行新指令。

加法计数、内存取值,乃至后面的命令执行,最终其实都是由时钟信号来控制执行时间点和先后顺序的。

在最简单的情况下,我们需要让每一条指令,从程序计数,到获取指令、执行指令,都在一个时钟周期内完成。如果 PC 寄存器自增地太快,程序就会出错。因为前一次的运算结果还没有写回到对应的寄存器里面的时候,后面一条指令已经开始读取里面的数据来做下一次计算了。这个时候,如果我们的指令使用同样的寄存器,前一条指令的计算就会没有效果,计算结果就错了。

在这种设计下,我们需要在一个时钟周期内,确保执行完一条最复杂的 CPU 指令,也就是耗时最长的一条 CPU 指令。这样的 CPU 设计,称之为单指令周期处理器(Single Cycle Processor)。

2. 读写数据所需要的译码器

如果我们把很多个 D 型触发器放在一起,就可以形成一块很大的存储空间,甚至可以当成一块内存来用。

译码器就是来确定在内存中,要写入和读取的数据的位置。

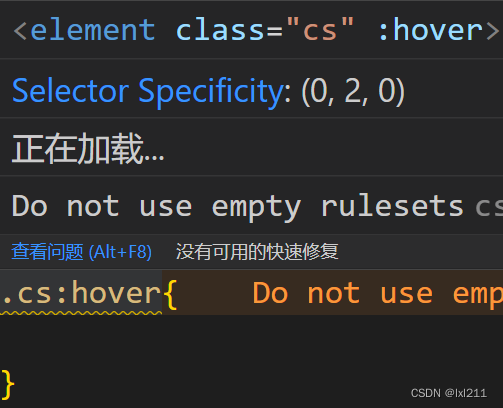

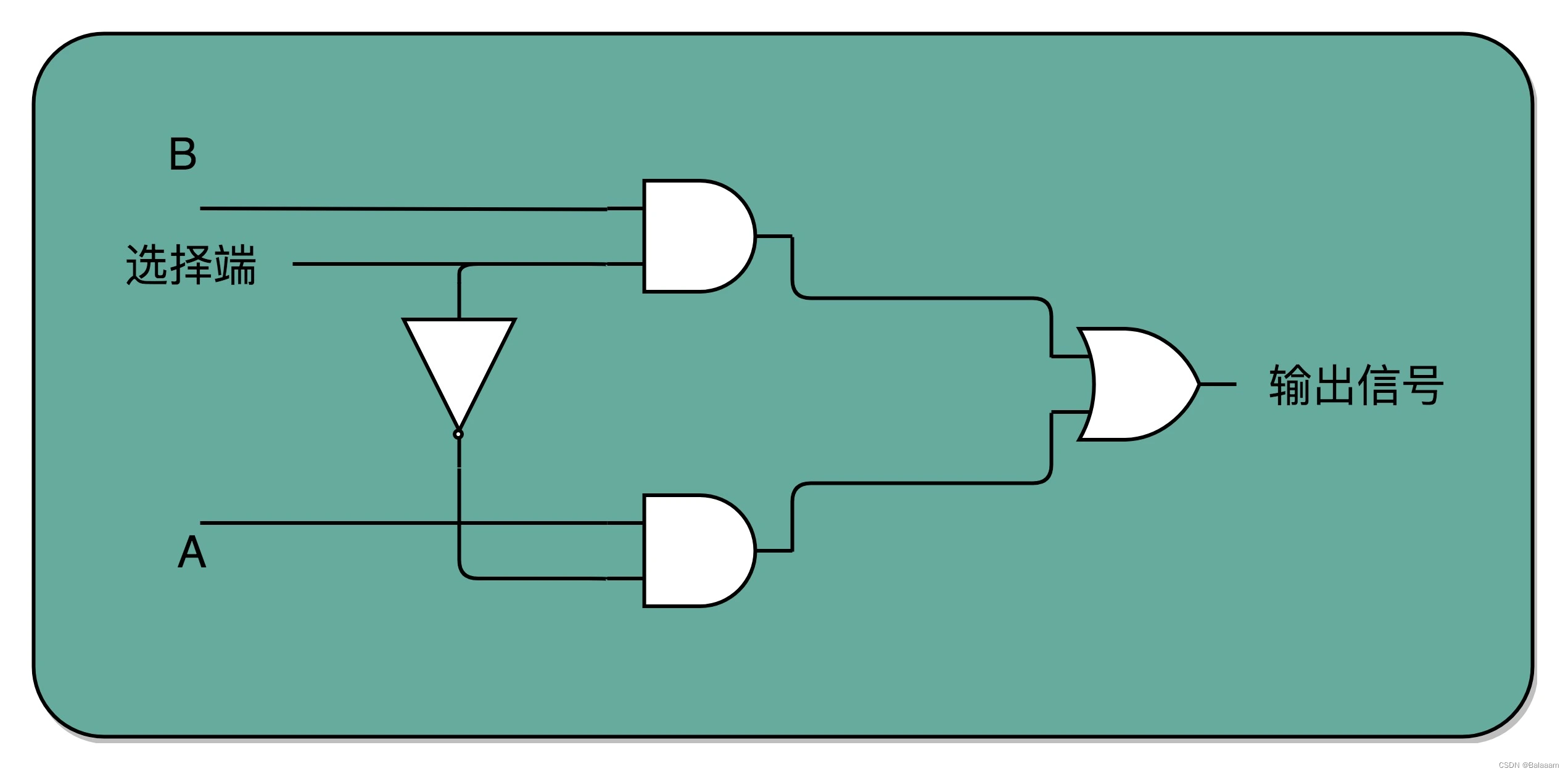

2-1 选择器的实现是由一个反相器、两个与门和一个或门。通过控制反相器的输入是 0 还是 1,能够决定对应的输出信号,就是和地址 A,还是地址 B 的输入信号一致。

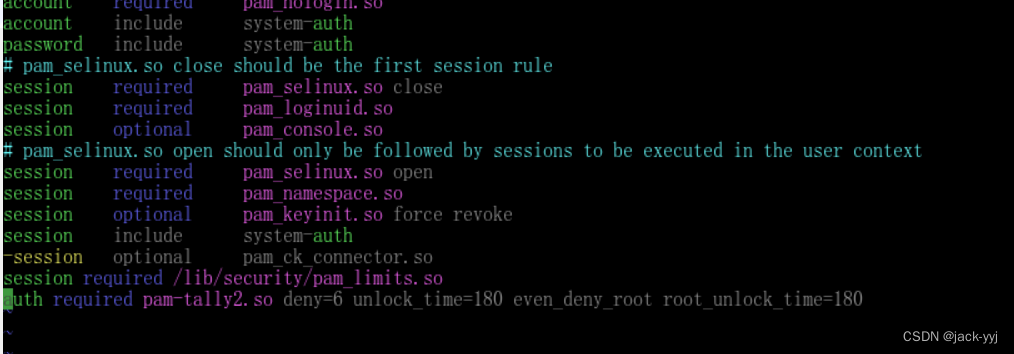

3-8 译码器也就是从 2 3 2^3 23 个地址中选择一个。现代的计算机,如果 CPU 是 64 位的,就意味着寻址空间也是 2 64 2^{64} 264,那么就需要一个有 64 个开关的译码器。

译码器的本质:从输入的多个位的信号中,根据一定的开关和电路组合,选择出自己想要的信号。除了能够进行“寻址”之外,我们还可以把对应的需要运行的指令通过译码器来进行译码,找出我们期望执行的指令(opcode)。

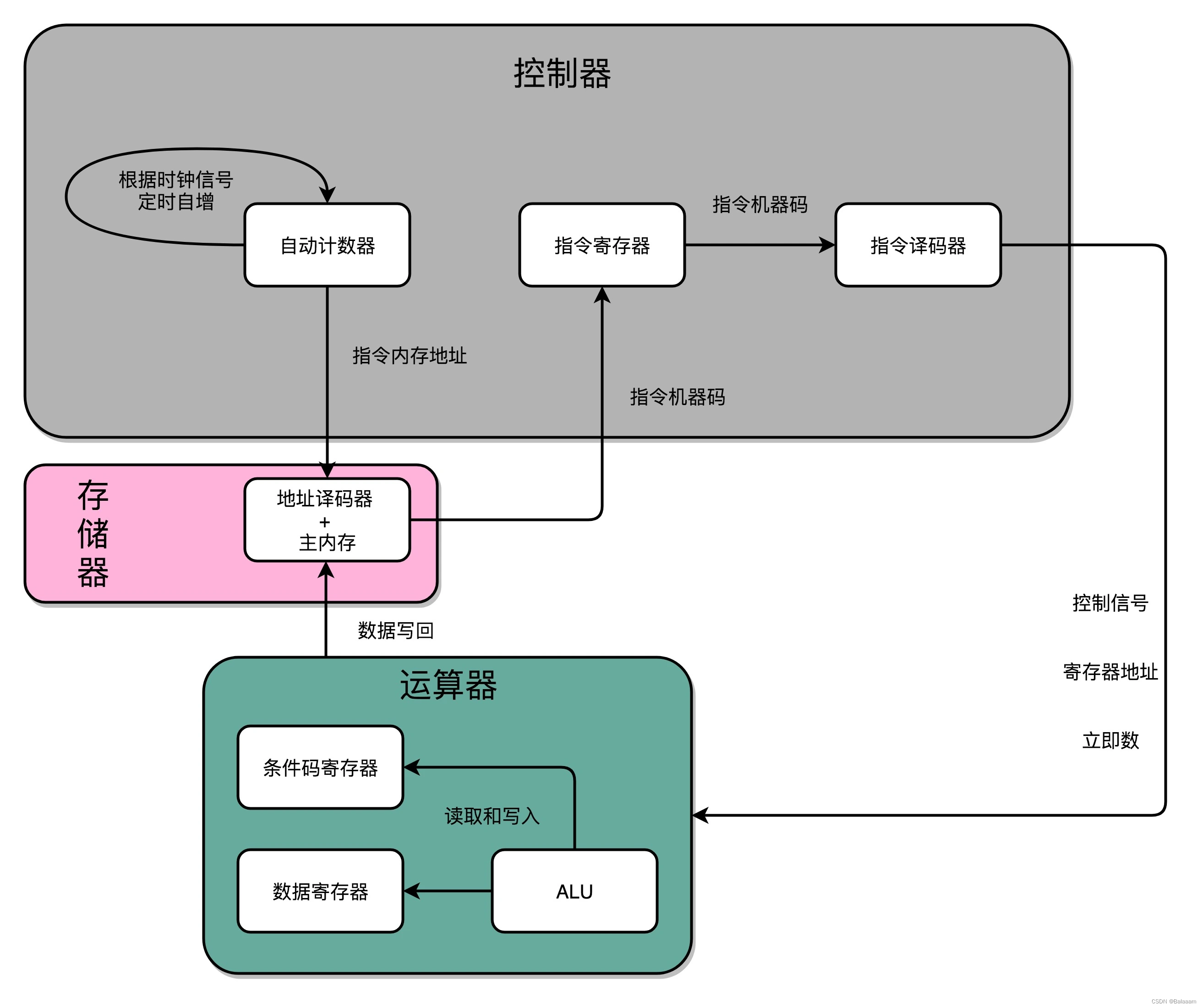

3. 数据通路完整实现

D 触发器、自动计数以及译码器,再加上 ALU,就凑齐了一个拼装一个 CPU 必须要的零件。

- 自动计数器。其会随着时钟主频不断地自增,来作为 PC 寄存器。

- 在自动计数器的后面,连上一个译码器。这个译码器还要同时连着通过大量 D 触发器组成的内存。

- 自动计数器会随着时钟主频不断自增,从译码器当中,找到对应的计数器所表示的内存地址,然后读取出里面的 CPU 指令。

- 读取出来的 CPU 指令会通过我们的 CPU 时钟的控制,写入到一个由 D 触发器组成的寄存器,也就是指令寄存器当中。

- 在指令寄存器后面,可以再跟一个译码器。这个译码器不再是用来寻址的了,而是把我们拿到的指令,解析成 opcode 和对应的操作数。

- 当拿到对应的 opcode 和操作数,对应的输出线路就要连接 ALU,开始进行各种算术和逻辑运算。对应的计算结果,则会再写回到 D 触发器组成的寄存器或者内存当中。

4. 总结

我们可以通过自动计数器的电路,来实现一个 PC 寄存器,不断生成下一条要执行的计算机指令的内存地址。

然后通过译码器,从内存里面读出对应的指令,写入到 D 触发器实现的指令寄存器中。再通过另外一个译码器,把它解析成我们需要执行的指令和操作数的地址。这些电路,组成了我们计算机五大组成部分里面的控制器。

我们把 opcode 和对应的操作数,发送给 ALU 进行计算,得到计算结果,再写回到寄存器以及内存里面来,这个就是我们计算机五大组成部分里面的运算器。

我们的时钟信号,则提供了协调这样一条条指令的执行时间和先后顺序的机制。同样的,这也带来了一个挑战,那就是单指令周期处理器去执行一条指令的时间太长了。

参考

极客时间《深入浅出计算机组成原理》:http://gk.link/a/11UMi