请阅读【ARM Cache 及 MMU/MPU 系列文章专栏导读】

及【嵌入式开发学习必备专栏】

文章目录

- Direct access to internal memory

-

-

- L1 cache encodings

- L1 Cache Data 寄存器

- Cache 数据读取代码实现

-

- 测试结果

-

Direct access to internal memory

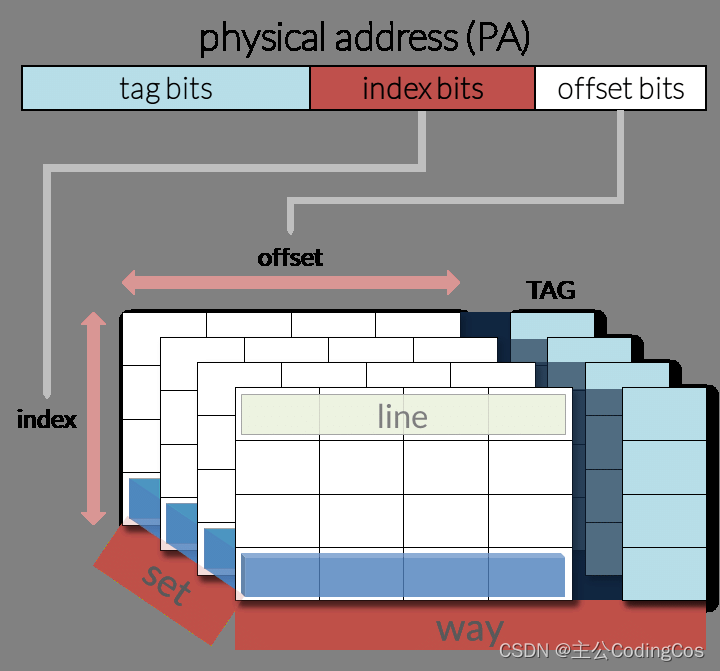

在ARMv8架构中,缓存(Cache)是用来加速数据访问的关键组件,它利用了程序执行中的局部性原理来提高性能。缓存中的每一行(Cache Line)通常包含了两个主要部分:实际的数据和一个标记(Tag)。这个标记用来标识存储在缓存行中的数据在内存中的位置。

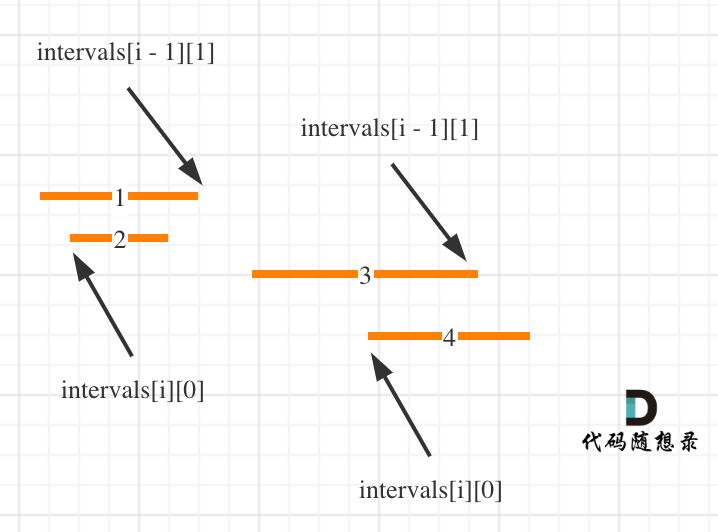

图 1-1 4-way, 4-sets set-associative cache

关于cache 中 set 和 way 的定义见文章:【ARM Cache 系列文章 1 – Cache基础概念学习】

ARMv9架构中,核心提供了一种机制,可以通过实现定义的系统寄存器