请阅读【ARM Cache 及 MMU/MPU 系列文章专栏导读】

及【嵌入式开发学习必备专栏】

文章目录

- MMU 转换控制寄存器 TCR_ELx

- TCR_ELx 概览

- TCR_ELx 寄存器字段详解

- TCR 使用示例

- Normal Memory

- Cacheable

- Shareability

- MMU 内存属性寄存器 MAIR_ELx

- MAIR_ELx 寄存器结构

- 内存属性字段

- Device Memory

- Normal Memory

- 使用实例

- MMU 地址翻译表基址寄存器 TTBR0/1_ELx

- 寄存器结构

- TTBR0_ELx 编程示例

- MMU 使能寄存 SCTLR_EL3

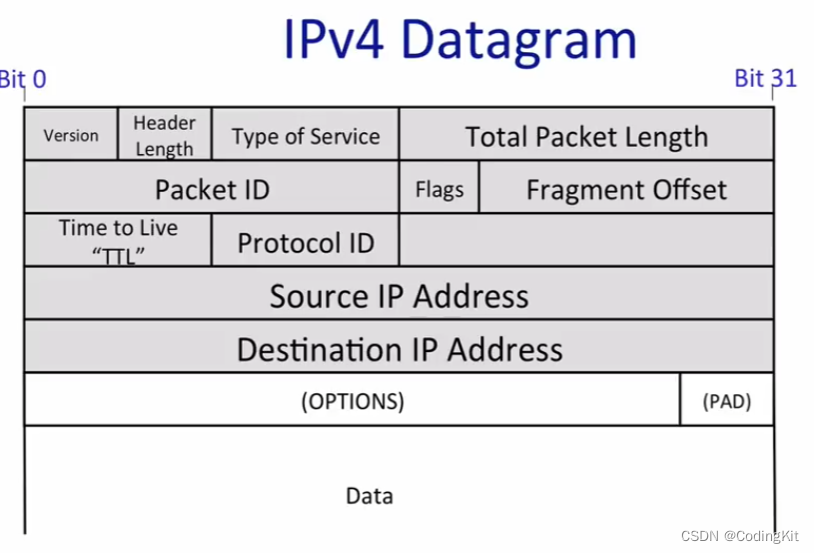

ARM MMU 的配置主要用到了下面4个寄存器

MMU 转换控制寄存器 TCR_ELx

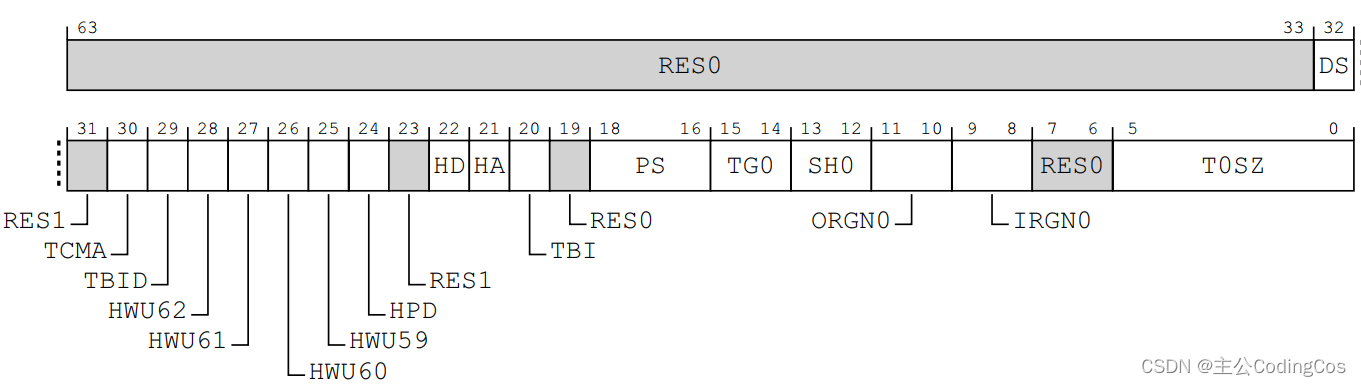

在ARMv8/v架构中,TCR_ELx(Translation Control Register at Exception Level x)寄存器用于控制地址转换的操作。这些控制包括页表的大小、地址空间的大小、以及内存区域的可缓存性和共享性等方面。TCR_ELx寄存器对于配置和优化系统的内存管理至关重要。

bit[5:0]: 用于配置使用多少位地址宽度,比如,要使用40位的地址宽度,那么T0SZ=64-40=24.bits [9:8]Inner cacheability attribute for memory associated with translation table walks0b00Normal memory, Inner Non-cacheable.0b01Normal memory, Inner Write-Back Read-Allocate Write-Allocate Cacheable.0b10Normal memory, Inner Write-Through Read-Allocate No Write-Allocate Cacheable.0b11Normal memory, Inner Write-Back Read-Allocate No Write-Allocate Cacheable.

bits [11:10]:Outer cacheability attribute for memory associated with translation table walks:0b00Normal memory, Outer Non-cacheable.0b01Normal memory, Outer Write-Back Read-Allocate Write-Allocate Cacheable.0b10Normal memory, Outer Write-Through Read-Allocate No Write-Allocate Cacheable.0b11Normal memory, Outer Write-Back Read-Allocate No Write-Allocate Cacheable.

bits [13:12]:由于 translation table 经常被访问且只需要在cluster内部使用所以可以将其配置为 Inner Shareable,cache coherent 可以避免掉对cache的操作。0b00Non-shareable.0b10Outer Shareable.0b11Inner Shareable.

bit[15:14]: 用于配置物理页颗粒(Granule size )的大小,比如要使用4K的页面,就需要将这两位配置为0即可;0b004KB.0b0164KB.0b1016KB.

bit[18:16]: 用于配置物理空间地址大小:0b00032 bits, 4GB.0b00136 bits, 64GB.0b01040 bits, 1TB.0b01142 bits, 4TB.0b10044 bits, 16TB.0b10148 bits, 256TB.0b11052 bits, 4PB.

TCR_ELx 概览

TCR_ELx寄存器中包含多个字段,这些字段影响地址转换和内存访问的不同方面。以下是一些主要字段的简介:

- T0SZ 和 T1SZ: 分别控制第0级和第1级的输入地址空间的大小。它们指定的是地址空间顶部未使用的位数,从而间接地定义了地址空间的大小。

- TG0 和 TG1: 分别设置第0级和第1级页表的粒度(页大小),比如4KB、16KB或64KB。

- IPS: 设置物理地址位宽,例如32位、36位、40位等,影响可访问的物理内存范围。

- SH0 和 SH1: 定义第0级和第1级页表条目的Shareability属性,指示内存区域是否可以在多个处理器核心间共享。

- ORGN0, ORGN1, IRGN0, IRGN1: 分别设置第0级和第1级页表的Outer和Inner缓存策略,包括Non-cacheable、Write-Back、Write-Through等。

TCR_ELx 寄存器字段详解

以下是TCR_ELx中一些关键字段的更详细说明:

- T0SZ 和 T1SZ(Translation Size): 它们确定了两个不同的转换表(页表)覆盖的虚拟地址空间的大小。例如,如果

T0SZ为25,则第0级的地址空间大小是[2^(64-25)]字节。 - TG0 和 TG1(Translation Granule): 这些值确定页表项所描述的页的大小。常见的页大小有4KB、16KB和64KB。页的大小影响页表的总体层级和每个页表项所能覆盖的内存大小。

- IPS(Intermediate Physical Address Size): 这个字段指定系统使用的最大物理地址位数。较大的物理地址允许系统访问更多的物理内存。

- SH0 和 SH1(Shareability): 这些字段决定内存访问是否可以在多个处理器之间共享。共享性设置有助于在多核处理器系统中维护内存的一致性。

- ORGN0, ORGN1, IRGN0, IRGN1(Outer and Inner Cacheability): 这些字段控制缓存策略,包括是否缓存以及使用何种缓存模式(如Write-Back或Write-Through)。

TCR 使用示例

假设需要为一个具有64KB页大小、使用48位虚拟地址和40位物理地址的系统配置TCR_EL1:

TCR_EL1.T0SZ = 16 // 设置虚拟地址空间为48位(64 - 16)

TCR_EL1.TG0 = 2 // 设置第0级页表粒度为64KB

TCR_EL1.IPS = 2 // 设置物理地址大小为40位

TCR_EL1.SH0 = 3 // 设置第0级页表条目为内部共享

TCR_EL1.ORGN0 = 1 // 设置第0级页表条目的外部缓存策略为Write-Back

TCR_EL1.IRGN0 = 1 // 设置第0级页表条目的内部缓存策略为Write-Back

此配置示例中,我们配置了一套页表来覆盖48位的虚拟地址空间,使用64KB的页大小,并且页表条目使用内部共享和Write-Back缓存策略。

Normal Memory

"Normal Memory"是对比于"Device Memory"的一种内存类型。Normal Memory通常用于存储应用数据和代码,而Device Memory则用于映射到设备寄存器。Normal Memory允许缓存和重新排序访问,从而提高效率。

Cacheable

Cacheable属性指示内存访问可以被缓存。这种属性可以进一步细分为以下类型:

- Write-Back (WB) Read-Allocate Write-Allocate Cacheable: 这是最常见的缓存类型,它在读操作时分配缓存行,在写操作时也分配缓存行。在写操作时,数据首先被写入到缓存中,然后在某个时刻异步地被写回到主存储器。这种方式可以减少访问主存储器的次数,提高性能。

- Write-Through (WT) Cacheable: 在这种模式下,数据在写操作时同时写入缓存和主存储器。这确保了主存储器中的数据总是最新的,但可能会牺牲一些写操作的性能。

Shareability

Shareability属性定义了内存区域的共享级别。ARMv8定义了三种共享级别:

- Non-Shareable: 这表示内存区域不被多个处理器核心共享。在单核心系统中,或者在不需要在核心之间共享该内存区域的情况下,可以使用此属性。

- Outer Shareable: 这表示内存区域可以在一组处理器核心之间共享,这组核心共享同一个外部(Level 2 或更高级别)缓存。

- Inner Shareable: 这表示内存区域可以在一组处理器核心之间共享,这组核心共享同一个内部(Level 1)缓存。这对于确保内部缓存中的数据一致性非常重要,特别是在多核处理器系统中。

MMU 内存属性寄存器 MAIR_ELx

在ARMv8架构中,MAIR_ELx寄存器(Memory Attribute Indirection Registers at Exception Level x)用于定义和配置内存属性表。这些寄存器允许软件定义多种内存属性类型,例如缓存策略和访问权限,这对于物理地址的属性定义至关重要。

MAIR_ELx寄存器支持多个异常级别,如MAIR_EL1、MAIR_EL2和MAIR_EL3,分别对应不同的异常级别使用。寄存器中的每个字段与转换表(Translation Table)中的属性字段相关联,这些属性字段用于描述如何访问对应的物理内存。

MAIR_ELx 寄存器结构

MAIR_ELx寄存器包含多个字段,每个字段8位,总共可以配置8种不同的内存属性。这意味着在转换表项(Translation Table Entry, TTE)中可以引用这8种配置中的任意一种来指定对应内存区域的访问特性。

字段格式如下:

Attr0[7:0]Attr1[15:8]Attr2[23:16]Attr3[31:24]Attr4[39:32]Attr5[47:40]Attr6[55:48]Attr7[63:56]

每一对Attrn字段定义了一种内存类型,包括其缓存策略和访问权限。每个Attrn字段内部分为两个子字段,高四位和低四位,分别代表不同的属性。

内存属性字段

Armv8-A和Armv9-A中有两种内存类型:普通内存(Normal Memory)和设备内存(Device Memory)。普通内存类似于RAM,Flash或者ROM这类的内存,代码只能放在普通内存中。设备内存类型用于描述外设。外设寄存器通常称为内存映射 I/O (MMIO)。

| Attr | Meaning |

|---|---|

| 0b0000dd00 | Device memory. See encoding of ‘dd’ for the type of Device memory. |

| 0b0000dd01 | If FEAT_XS is implemented: Device memory with the XS attribute set to 0.See encoding of ‘dd’ for the type of Device memory. |

| 0b0000dd1x | UNPREDICTABLE |

| 0booooiiii, (oooo != 0000 and iiii != 0000) | Normal memory. See encoding of ‘oooo’ and ‘iiii’ for the type of Normal Memory. |

| 0b01000000 | If FEAT_XS is implemented: Normal Inner Non-cacheable, Outer Non-cacheable memory with the XS attribute set to 0. |

| 0b10100000 | If FEAT_XS is implemented: Normal Inner Write-through Cacheable, Outer Write-through Cacheable, Read-Allocate, No-Write Allocate, Non-transient memory with the XS attribute set to 0. |

| 0b11110000 | If FEAT_MTE2 is implemented: Tagged Normal Inner Write-Back, Outer Write-Back, Read-Allocate, Write-Allocate Non-transient memory. Otherwise, UNPREDICTABLE. |

| 0bxxxx0000, (xxxx != 0000, xxxx != 0100, xxxx != 1010,xxxx != 1111 | UNPREDICTABLE |

-

当

attr的值为0b0000dd01时

这表示设备内存,具体行为取决于dd位的编码,该设备内存的XS属性被设置为 0。- 如果支持

FEAT_XS特性,则表示带有XS属性设置为0的设备内存。 - 根据

dd的编码,类型的设备内存不同,可能是nGnRnE、nGnRE、GRE或nGRE(这些是ARM定义的设备内存类型,分别对应于不同的访问和共享属性)。 - 如果不支持

FEAT_XS特性,则结果是不可预测的。

- 如果支持

-

当

attr的值为0b01000000时- 如果支持

FEAT_XS特性,则表示内部(inner)非缓存、外部(outer)非缓存的正常内存,且XS属性被设置为0。 - 这种配置通常用于需要绕过缓存直接访问内存的情况,确保数据的实时性。

- 如果不支持

FEAT_XS特性,则结果是不可预测的。

- 如果支持

-

当

attr的值为0b10100000时- 如果支持

FEAT_XS特性,则表示内部(inner)和外部(outer)都设置为写通(write-through)缓存策略的正常内存。这种配置支持读取分配(read-allocate),但不支持写入分配(no-write allocate),且被视为非瞬态内存。 - 这种配置有助于实现一定程度的缓存,同时保持一定的数据一致性,因为所有的写操作都会即时反映到主存中。

- 如果不支持

FEAT_XS特性,则结果是不可预测的。

- 如果支持

- 当

attr的值为0b11110000时- 如果支持

FEAT_MTE2特性,则表示带有标签的正常内存,其中内部(inner)和外部(outer)都设置为写回(write-back)缓存策略。这种配置支持读取分配和写入分配(read-allocate, write-allocate),被视为非瞬态内存。 - 这种配置提供了最高级别的缓存性能,适用于对性能敏感的应用场景。

- 如果不支持

FEAT_MTE2特性,则结果是不可预测的。

- 如果支持

关于 FEAT_MTE2 及 FEAT_XS 介绍见:【ARM Cache 与 MMU 系列文章 7.6.1 – ARMv8/v9 MMU FEAT_XS(XS Attribute)与 FEAT_MTE2 介绍】

Device Memory

设备有四种子类型,具有不同的限制等级。下面的子类型限制比较宽松:

- Device-GRE

- Device-nGRE

- Device-nGnRE

- Device-nGnRnE: 这个子类型限制最为严格。

4种类型的编码如下表所示:

dd 编码原则:

| dd | Meaning |

|---|---|

| 0b00 | Device-nGnRnE memory |

| 0b01 | Device-nGnRE memory |

| 0b10 | Device-nGRE memory |

| 0b11 | Device-GRE memory |

Device后面的字母具有不同的含义:

- 聚合(G,nG):访问可以聚合(G)或者不聚合(nG),聚合意味着可以对同一位置的多次访问合并为一次访问,或者将多次较小的访问合并为一次较大的访问。

- 重排(R,nR):这指定对于同一外设可进行重排(R)或者不重排(nR)访问。当允许重排访问时,限制同普通内存一样。

- 提前写应答(E,nE):这决定了何时被认为写完成。如果允许提前写应答,一旦其他观察者可见,在到达实际目的地之前,访问可以视为写完成。例如,一旦数据写到写缓冲区,其他PE就可以看到这些数据。当不允许提前写应答时,数据必须到达最终目的地。

有两个示例:

Device-GRE:允许聚合、重排和提前写应答访问;Device-nGnRnE:不允许聚合、重排和提前写应答访问。

聚合允许对相似位置的内存访问合并到单个总线事务中,从而优化访问。提前写应答意味着当数据发送到缓冲区后,总线是否可以发送写完成确认标志。这样即使外设还未收到写动作,所有PE均已能观察到此次写入。

Normal Memory

‘oooo’ 编码原则:

| ‘oooo’ | Meaning |

|---|---|

| 0b0000 | See encoding of Attr |

| 0b00RW, RW not 0b00 | Normal memory, Outer Write-Through Transient |

| 0b0100 | Normal memory, Outer Non-cacheable |

| 0b01RW, RW not 0b00 | Normal memory, Outer Write-Back Transient |

| 0b10RW | Normal memory, Outer Write-Through Non-transient |

| 0b11RW | Normal memory, Outer Write-Back Non-transient |

R = Outer Read-Allocate policy, W = Outer Write-Allocate policy.

‘iiii’ 编码原则:

| ‘iiii’ | Meaning |

|---|---|

| 0b0000 | See encoding of Attr |

| 0b00RW, RW not 0b00 | Normal memory, Inner Write-Through Transient |

| 0b0100 | Normal memory, Inner Non-cacheable |

| 0b01RW, RW not 0b00 | Normal memory, Inner Write-Back Transient |

| 0b10RW | Normal memory, Inner Write-Through Non-transient |

| 0b11RW | Normal memory, Inner Write-Back Non-transient |

R = Inner Read-Allocate policy, W = Inner Write-Allocate policy.

在’oooo’ 和 ‘iiii’ 中 R 和 W 含义如下:

| R or W | Meaning |

|---|---|

| 0b0 | No Allocate |

| 0b1 | Allocate |

-

Read Allocate: 当缓存因读操作而缺失(即所需的数据不在缓存中)时,将从更低层次的存储(比如主存)加载数据到缓存中。这种策略意味着缓存会尝试在读操作时加载所需的数据块。

-

Write Allocate (也称为Write-Read Allocate): 当缓存因写操作而缺失时,缓存行首先被加载到缓存中,然后再执行写操作。这种策略用于优化那些后续可能对同一地址进行读操作的情形,因为数据已经被加载到缓存中了。

-

No Read Allocate: 当缓存因读操作而缺失时,数据直接从更低层次的存储读取,但不加载到缓存中。这意呼着缓存不会因为这样的读操作而更新。这种策略可能适用于那些一次性读取或不重复读取的数据,以避免缓存中有用数据的替换。

-

No Write Allocate: 当缓存因写操作而缺失时,修改直接写入到更低层次的存储,而不是首先加载缓存行然后执行写操作。这种策略减少了因为写操作引起的不必要的缓存行加载,特别是对于那些不再被读取的数据。

使用实例

配置MAIR_EL1为最常见的例子,下面是一个典型的配置过程:

- 配置非缓存访问(设备内存):

// Attr0设为0x00:设备内存,非缓存,非缓冲

- 配置写回缓存(正常内存):

// Attr1设为0xFF:正常内存,Write-Back, Read & Write Allocate

配置完成后,转换表项可以通过指定的属性索引(Attrn)来使用这些定义。

MMU 地址翻译表基址寄存器 TTBR0/1_ELx

TTBR0_EL3寄存器负责存储阶段1(Stage 1)地址翻译表(页表)的基地址。页表用于将虚拟地址映射到物理地址。这个寄存器包含了页表基地址(BADDR)的大部分位,但是实际使用的位数和页表的对齐要求取决于多个因素。

TTBR0_ELx(Translation Table Base Register 0 at Exception Level x)用于存储页表的物理基址,其中x可以是1、2或3,表示不同的异常级别。在多级页表结构中,这个寄存器指向页表的第一级。

寄存器结构

在ARMv8架构中,TTBR0_ELx拥有以下关键组成部分:

-

BADDR[47:x]: 这些位表示阶段1翻译表基地址的高位部分。

x的具体值由TCR_EL3.T0SZ、翻译阶段和翻译粒度大小共同决定。这些位直接存储页表基地址的相应部分。 -

BADDR[x-1:0]: 这些位用于确保页表基地址的适当对齐。对于页表基地址来说,

x是最小的地址位,要求页表根据表的大小进行对齐。最小允许的x值是6,这意味着最小的页表对齐是64字节(2^6)。x的值基于TCR_EL3.T0SZ的设置来计算。T0SZ指定了虚拟地址空间顶部未使用的位数,决定了地址空间的大小和页表的层级。根据T0SZ的值和选定的翻译粒度(如4KB、16KB或64KB),可以计算出页表的大小和对应的对齐要求。-

页表必须对齐到其自身的大小。例如,如果一个页表包含256个条目(对于4KB粒度的页表来说),它必须至少对齐到1KB(256条目 * 4字节/条目)的边界。

-

如果页表包含少于8个条目,则必须对齐到64字节的边界,即使表的计算大小小于64字节。

-

如果

TCR_EL3.PS的值不是0b110,则BADDR的[x-1:1]位被保留为0(RES0)。这有助于确保兼容不同的物理地址大小设置。 -

如果处理器支持52位物理地址和内部物理地址(PA和IPAS),并且在启用这些扩展时,

BADDR的[51:48]位应设置为0b0000,以确保地址的高位不会被错误地使用。

-

-

CnP[0]: 用于控制页表条目的共享模式,特别是当实现了

FEAT_TTCNP特性时。这个位提供了一种机制,允许处理器指示页表条目是否为内部可共享域中所有处理器元素(PE)的共同集合的一部分。具体地说,这与页表的私有性或共享性有关。-

0b0:当CNP位为0时,表明由TTBR0_EL3指向的转换表条目,对于当前的转换体制,可以与内部可共享域中其他PE的对应条目有所不同。也就是说,这些条目不需要在所有PE之间共享,允许存在差异。这种配置的共享性不受其他PE上TTBR0_EL3.CNP位值的影响。 -

0b1:当CNP位为1时,表示所有设置了CnP位且在同一内部可共享域中的PE使用的,由TTBR0_EL3指向的转换表条目是相同的。这意味着,这些页表条目构成了一个公共集合,应该被域内所有配置为CnP=1的PE共用。这个设置有利于减少不同处理器之间的页表不一致性,从而提高系统的协同工作效率。 -

TLB缓存:

CnP位的值被允许缓存在TLB(Translation Lookaside Buffer)中,这有助于加速地址转换过程,因为处理器可以快速地从TLB获取转换结果,而不是每次都从页表中读取。 -

如果在同一内部可共享域中,多个PE的

TTBR0_EL3.CNP位都设置为1,但它们并不指向同一组转换表条目,那么使用TTBR0_EL3进行的转换结果是受限的不可预测的。换句话说,如果配置了CNP=1但未能确保共同集合的一致性,系统的行为将会变得无法预测,可能导致问题。

-

ARMv8支持使用两个TTBR寄存器(TTBR0_ELx和TTBR1_ELx)来支持不同范围的地址空间,通常:

TTBR0_ELx用于较低范围的虚拟地址。TTBR1_ELx用于较高范围的虚拟地址。

这种分割允许操作系统将用户空间和内核空间的映射分开管理,提高了安全性和效率。

TTBR0_ELx 编程示例

配置TTBR0_EL1通常涉及到计算页表基址,然后将其加载到寄存器中。以下是设置TTBR0_EL1的一个示例代码片段:

// 假设x0寄存器包含页表的物理基址

msr TTBR0_EL1, x0 // 将x0寄存器的值写入TTBR0_EL1

// 其中,必须确保基址符合对齐要求

MMU 使能寄存 SCTLR_EL3

SCTLR寄存器是系统顶层的寄存器,可以控制内存系统,其中包括Cache和MMU等。对于MMU 的使能是通过 系统控制寄存器 SCTLR bit[0] 来控制的,包括SCTLR_EL1、SCTLR_EL2和SCTLR_EL3,但并不是所有bit在EL1都可用。

这里简单介绍下 I,C以及M bit:

- I 位,bit[12]:I-cache的enable,这是个全局的指令缓存使能位:

0表示I-Cache被禁止1表示I-Cache被使能

- C 位,bit[2]: 缓存使能位,针对数据缓存(data cache)和统一缓存(unified cache,L2 cache):

0表示Data-Cache和Unified Cache(L2 Cache)被禁止- 1 表示I-Cache被使能

- M 位,bit[0] : MMU使能位

关于SCTLR 寄存器的其它域值含义见:【ARMv8 异常模型入门及渐进 2 – ARMv8/v9 寄存器 (SCR_ELn | ELR_ELn | ESR_ELn | CTR | HCR_ELn … 详细介绍】

判断当前 MMU是否打开:

func Arm_MmuEnabled

EL1_OR_EL2_OR_EL3 x1

1: mrs x0, sctlr_el1 // Get control register EL1

b 4f

2: mrs x0, sctlr_el2 // Get control register EL2

b 4f

3: mrs x0, sctlr_el3 // Get control register EL3

4: and x0, x0, #CTRL_M_BIT

ret

endfunc Arm_MmuEnabled

打开MMU 函数:

func Arm_EnableMmu

EL1_OR_EL2_OR_EL3 x1

1: mrs x0, sctlr_el1 // Read System control register EL1

b 4f

2: mrs x0, sctlr_el2 // Read System control register EL2

b 4f

3: mrs x0, sctlr_el3 // Read System control register EL3

4: orr x0, x0, #CTRL_M_BIT // Set MMU enable bit

bic x0, x0, #(0x1 << 19) // WXN bit (writeable execute never)

EL1_OR_EL2_OR_EL3 x1

1: tlbi vmalle1

dsb nsh

isb

msr sctlr_el1, x0 // Write back

b 4f

2: tlbi alle2

dsb nsh

isb

msr sctlr_el2, x0 // Write back

b 4f

3: tlbi alle3

dsb nsh

isb

msr sctlr_el3, x0 // Write back

4: isb

ret

endfunc Arm_EnableMmu