前文讲解了Aurora8B10B协议原理及xilinx相关IP,本文讲解如何设置该IP,并且通过示例工程完成该IP的仿真和上板。

1、生成Aurora8B10B IP

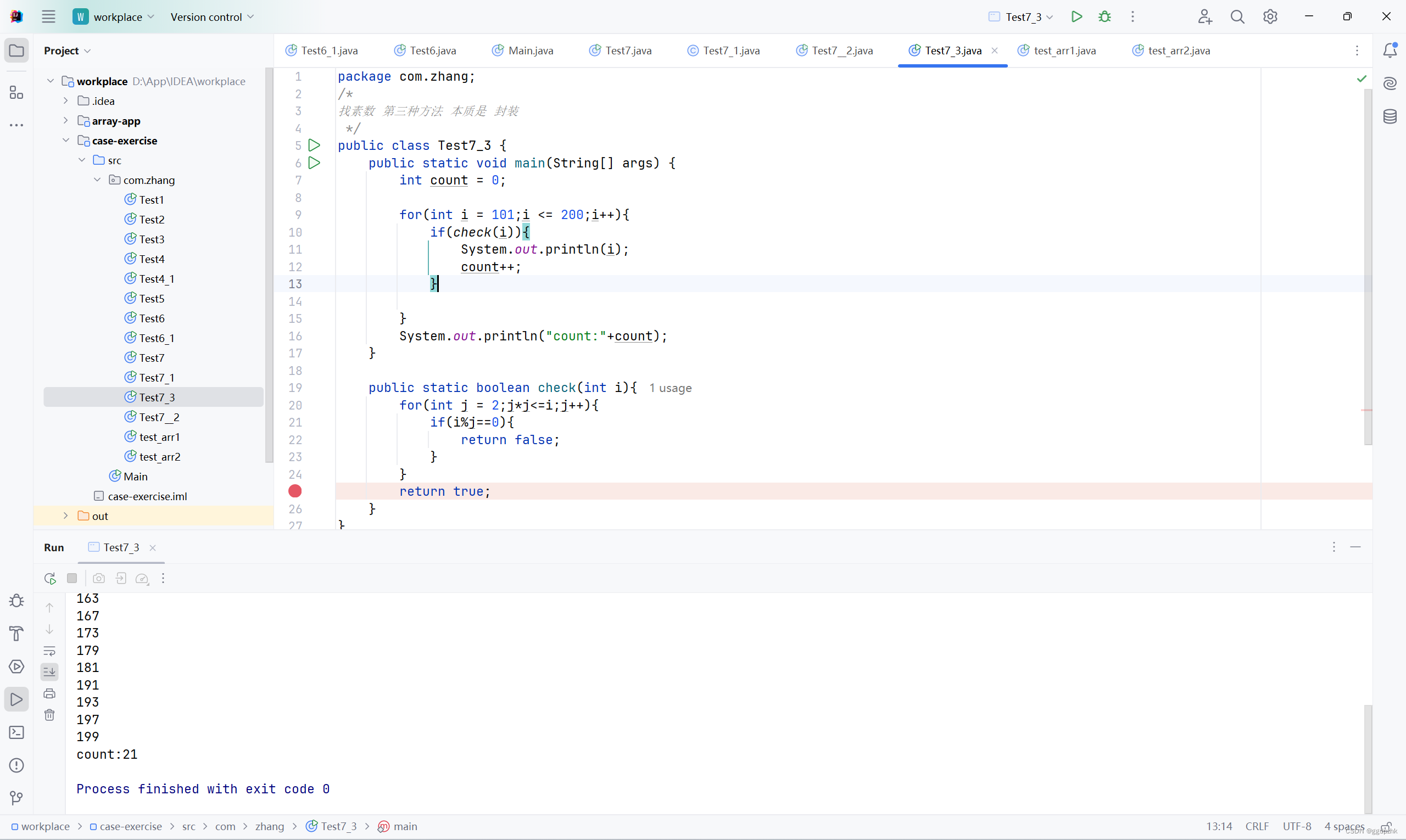

如下图所示,首先在vivado的IP catalog中输入Aurora 8B10B,双击该IP。

Aurora 8B10B相对GTX的配置相对简单,主要配置如下界面,下面分别对各个选项含义进行讲解。

1、Lane width:设置用户发送和接收数据位宽,可以设置为4字节或2字节,本文设置为4字节。

2、Line Rate:设置高速收发器线速率,最大不超过6.6Gbps,意味着高速收发器使用CPLL的输出作为参考时钟信号。

3、GT Refclk:高速收发器参考时钟频率,该时钟必须来源于GT bank的差分时钟引脚,选择自己开发板的差分时钟频率即可。

4、INT clk:初始化时钟,对时钟来源没有要求,可以和DRP共用同一时钟。

5、DRP Clk:动态重配置的参考时钟信号,对时钟来源没有要求。

6、Dataflow Mode:选择该IP工作模式,可选有仅发送、仅接收、全双工,本文选择全双工模式。

7、Interface:用户接口类型,前文分析过该IP支持两种用户接口,本文选择使用标准的axi-stream格式,更加适用于一般情况。

8、Flow Control:流控设置,前文讲解过该IP支持两种流控模式,用户可以在此处选择使用其中一种或两种流控,本文不使用流控传输。

9、back channel:是一个不可设置的选项,与初始化相关。

10、Scrambler/Descrambler:启用加扰和解扰模块,该IP可以对发送数据加扰,对接收数据解扰,加扰和解扰表达式为X16+X5+X4+X3+1,一般勾选即可,可以增加数据的抗干扰能力。

11、Little Endian Support:小端对齐。不勾选该选项时,图中数据信号的最高位是0,表示先传输高字节数据,采用大端对齐。勾选该选项后,数据位会颠倒,变成小端对齐,FPGA内部一般使用大端对齐,保持默认即可。

12、Additional Transceiver Control and Status Ports:勾选后会多一些debug的端口信号,默认不勾选。

然后配置GT Selections界面,该界面主要配置高速收发器的通道数,以及通道和参考时钟来源的位置,这些保持默认即可,用户可以在后续的XDC文件中更改引脚来达到相同目的。

最后这个界面用于选择将共享逻辑放在IP内部还是外部,一般都会选择外部,方便之后例化多个收发器,如果以后使用其余高速IP,均会出现这个界面。

IP的配置就完成了,如果配置过GTX、看过前面两篇原理相关文章,IP相关配置的含义应该会比较清晰。

2、仿真Aurora8B10B IP

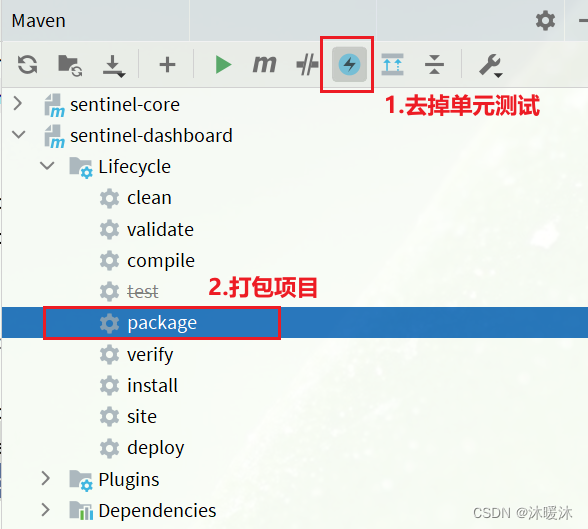

在IP成功生成IP之后,鼠标右击IP,然后选择生成示例工程,如下图所示,之后全部点击OK即可。

Xilinx官方的IP除了有配套手册外,还都提供了示例工程。后续很多IP的学习思路均是如此,首先通过手册得知IP的工作方式,通过示例工程去验证这些功能,然后在写自己的代码。

示例工程的顶层RTL框图如下所示,中间的模块是对IP封装后的顶层模块,左边两个模块用于产生发送数据,右边两个模块用于对接收的数据转换和校验。

我们应该需要注意的是中间模块是怎么对IP进行封装的,发送数据和接收数据部分不用太关心,按照axi_stram生成相关数据即可,示例工程这两部分写的比较复杂。

打开上图中间模块,得到以下内容,与前面GTX的示例工程比较相似。注意即使高速收发器没有使用QPLL输出时钟,但是在设计的时候,依旧需要例化GT_COMMON,这个在GTX手册中好像也可以找到有相关描述。

注意上图的用户时钟USER_CLK信号依旧是tx_out_clk经过MMCM后生成的,与GTX一致。

关于IP的端口信号,重要的状态信号和控制信号在前文讲解Aurora8B10B IP原理的时候已经详细讲述,如同DRP、QPLL相关信号与GT收发器是一致的,就不再赘述了。

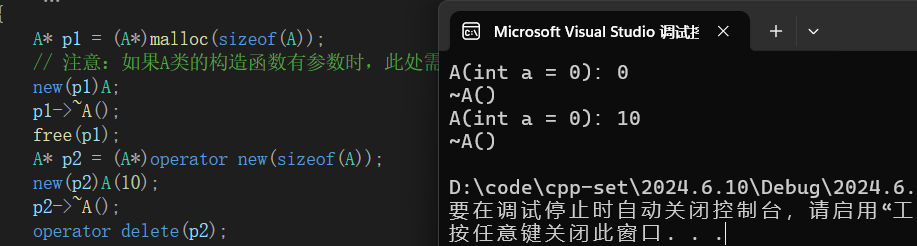

如果不使用动态重配置功能,则DRP相关信号可以参考示例工程的连接,输入信号接地,输出信号悬空,如下图所示。

QPLL相关信号如下图所示,首先高速收发器的差分时钟信号通过IBUFDS_GTE2转换为单端时钟输入GT_COMMON和IP。本工程的初始化时钟是差分输入,后续在整理时可以直接使用单端时钟信号。

下图是时钟和复位信号相关连接,复位同步模块需要将外部输入的两个异步复位信号分别同步到对应时钟域下。TXOUTCLK通过BUFG作为用户时钟信号,此处没有使用MMCM的原因应该是TXOUTCLK的频率与USER_CLK相同。

下图是状态信号和控制信号的连接,如果不使用回环模式和掉电模式,需要接地处理。需要把一些状态信号引出,方便后续上板调试时排查问题。

IP的相关信号就讲解完毕了,至于axi_stream输入和输出相关信号,应该也很熟悉了,前文讲解原理时也讲解了时序,不再赘述。

示例工程在TestBench中例化了两次该模块,即使用了两个高速收发器进行仿真,把高速收发器1的发送通道与高速收发器2的接收通道连接,从而形成数据闭环。

由于两个模块产生相同数据,在仿真时可以只关注一个收发器的接收和发送通道数据,就能够观察接收和发送数据是否正确。直接运行仿真,添加下图所示模块的信号进行仿真,只需要观察axi_stream信号和部分状态信号即可。

仿真结果如下所示,两个复位信号的设计与手册中有点区别,gt_reset应该要在reset拉低之前拉低,还是以手册为准比较好,毕竟示例工程也是有坑的,在后面的设计中会看到有些示例工程也存在考虑问题不充分,导致无法正确接收数据的情况。

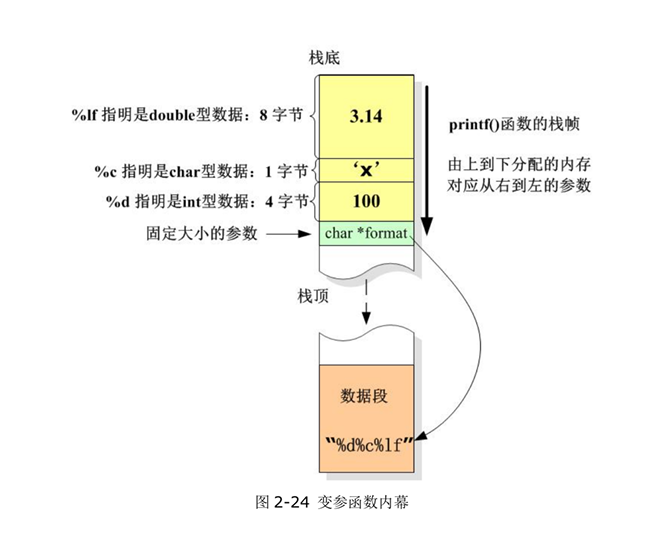

等待通道初始化完成之后开始收发数据,放大收发数据部分,如下图所示。粉色信号是发送通道需要发送的数据,而白色信号是接收通道接收到的数据。

需要注意数据掩码信号s_axi_tx_keep只有在s_axi_tx_last为高电平时才是有效的,其余时间均当成4’hf处理。因此发送的八个数据的所有位都是有效的,与接受到的数据保持一致,证明该IP能够正常收发数据。

关于模块仿真和IP信号连接的相关内容就讲解完毕了,也体现了RTL视图的重要性,通过RTL视图可以清晰知道模块信号连接,不需要看官方繁杂的代码。

3、Aurora8B10B IP上板测试

接下来是上板环节,由于板子上普通bank并没有差分时钟,而初始化时钟与drp时钟频率相同,则可以将示例工程的两个时钟合并,都使用100MHz单端时钟。

因为该工程只有单个收发器,如果要上板测试,需要把高速收发器设置为PMA回环模式。由于开发板的复位按键均为低电平,因此需要将两个复位信号取反。

然后综合工程,添加调ILA调试信号,其中tx_data与s_axi_tx_data对应,如下图所示。

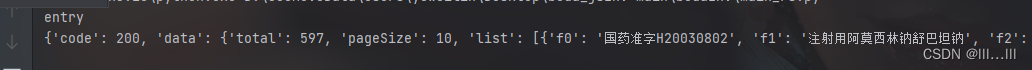

对工程布局布线,之后下载到开发板进行调试,ILA抓取发送数据通道的时序如下所示。tx_keep只有在tx_last为高电平的时候才有效,其余时间可以忽视,发送的前两个数据分别为32’h7cdc7cdc和32’hbe6ebe6e。

下图是这帧数据的结束时序,当tx_last为高电平时,tx_keep的值为4’d8,表示最后一个数据只有最高位有效。因此发送的最后两个数据为32’h3ba43ba4和8’h1d。

下图是接收通道接收到图18、19发送的数据,接收到的起始两个数据与图18起始发送的2个数据相同。

下图是接收这一帧数据的结束时序,注意rx_keep图中只有低3位信号,因为最高位始终为高电平,在生成ILA时被忽略了。因此接收到最后两个数据为32’h3ba43ba4和8’h1d,与图19发送数据保持一致,证明IP收发数据时序没有问题。

由于上板的时候修改了复位的极性和回环模式,所以在使用仿真时需要修改回去,不然无法运行仿真。

该工程可以通过官方直接获取,也可以在公众号(数字站)回台回复“Aurora8B10B 仿真及上板验证”(不包括引号)直接获取。

如果对文章内容理解有疑惑或者对代码不理解,可以在评论区或者后台留言,看到后均会回复!

如果本文对您有帮助,还请多多点赞👍、评论💬和收藏⭐!您的支持是我更新的最大动力!将持续更新工程!

![【已解决】FileNotFoundError: [Errno 3] No such file or directory: ‘xxx‘](https://img-blog.csdnimg.cn/direct/6782c1b287b449b6b9ef1fb273ac7e34.png)