目录

一、了解GPIO

二、时钟

三、引脚复用

四、引脚属性

五、控制GPIO总结

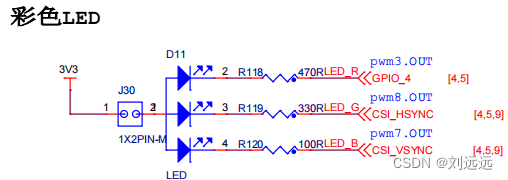

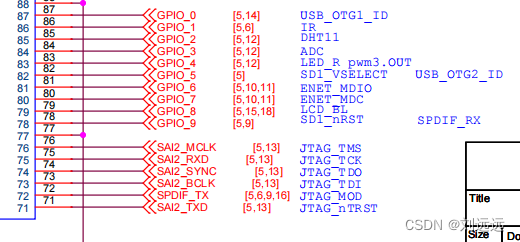

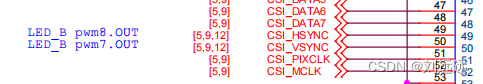

六、硬件原理图

一、了解GPIO

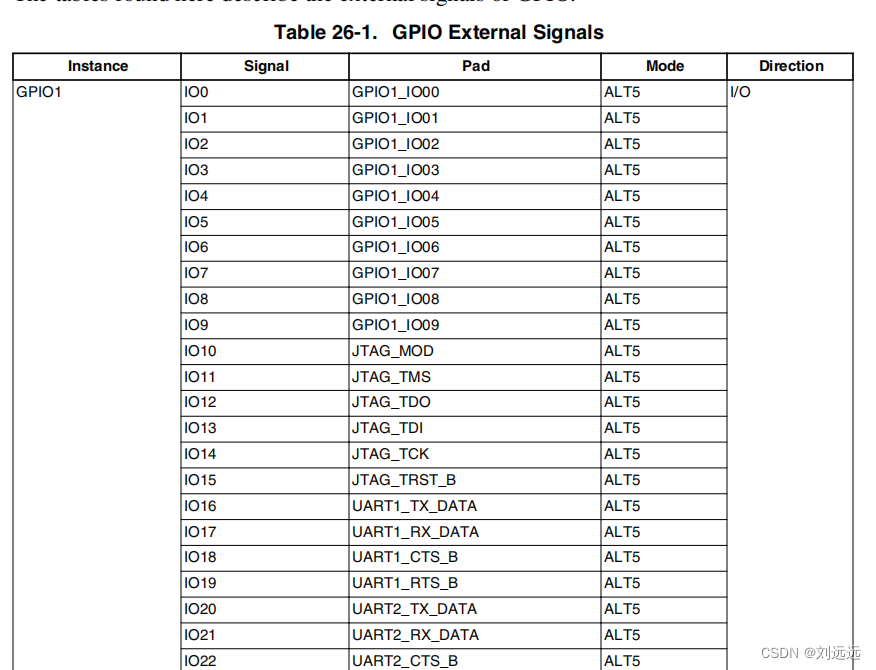

数量

5组GPIO(GPIO1~GPIO5),每组最多32个,共124个

- GPIO1_IO0——GPIO1_IO31

- GPIO2_IO0——GPIO2_IO21

- GPIO3_IO0——GPIO3_IO28

- GPIO4_IO0——GPIO4_IO28

- GPIO5_IO0——GPIO5_IO11

数据手册描述

26.2 External Signals

二、时钟

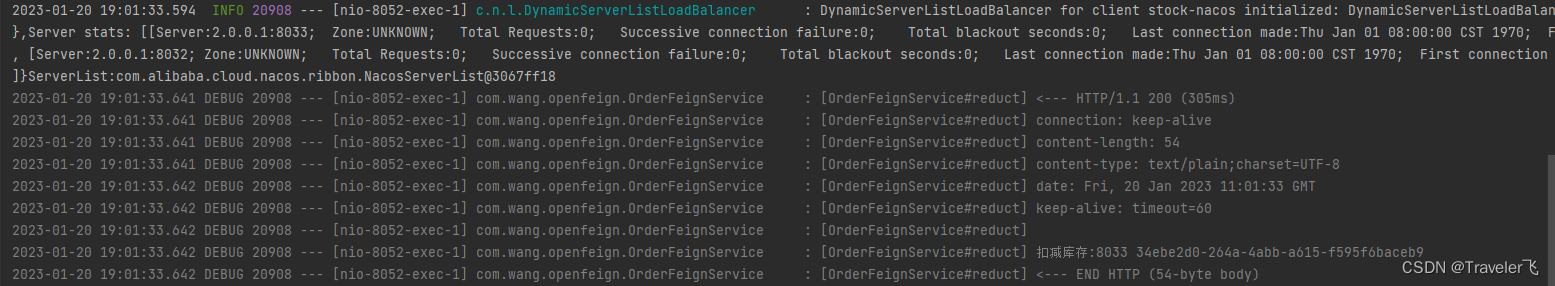

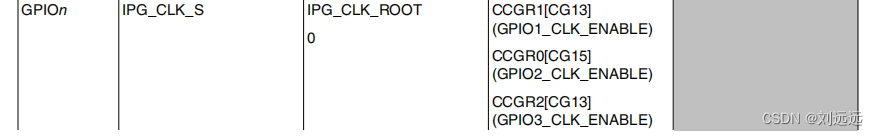

clock_controller module(CCM模块)用于配置芯片的各种外设时钟。跟GPIO相关的时钟主要有CCM_CCGR(0~3)寄存器。

数据手册描述

18.4 System Clocks

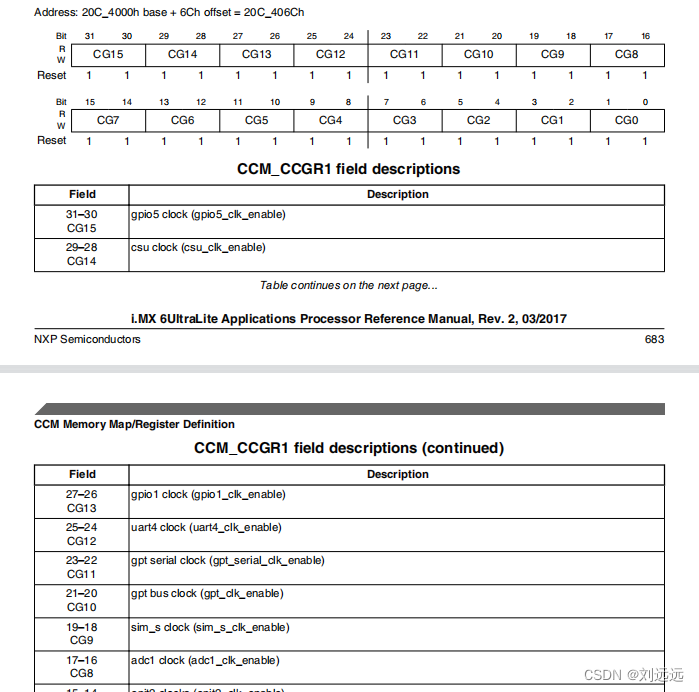

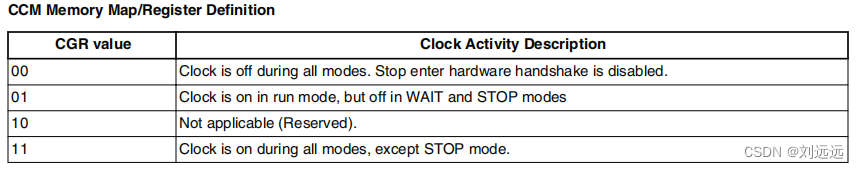

18.6.24 CCM Clock Gating Resgister 1(CCM_CCGR1)

上图中,第一个address表示的该时钟外设在内存中的位置;外设与内核不同,其中的寄存器位数设置需要从手册中具体去查看;

- 00:所有模式下都关闭外设时钟

- 01:只有在运行模式下打开外设时钟

- 10:保留

- 11:除了停止模式以外,该外设时钟全程使能

数据手册描述

18.6.23 CCM Clock Gating Register 0(CCM_CCGR0)

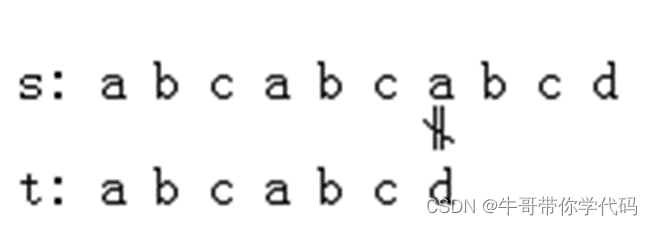

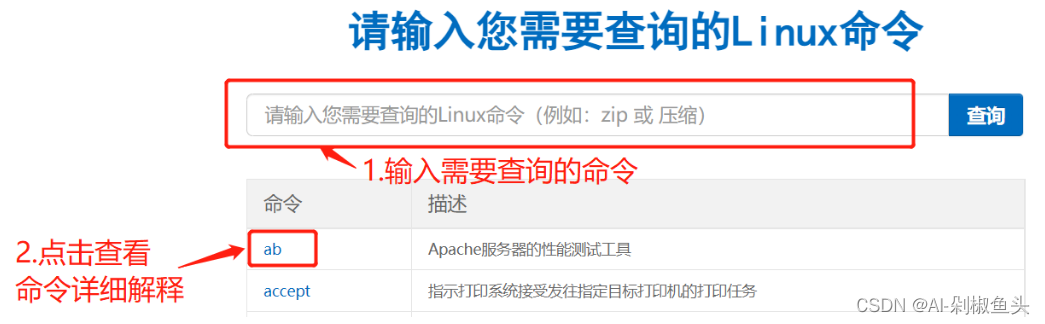

三、引脚复用

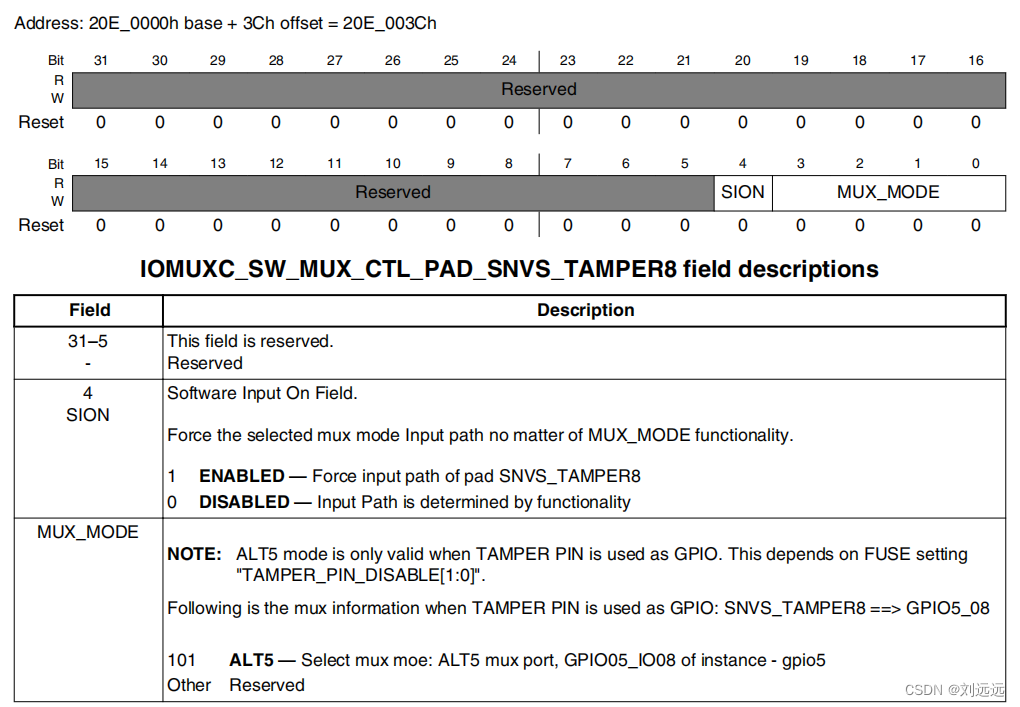

相关寄存器:IOMUXC_SW_MUX_CTL_PAD_XXX

数据手册:

注意:数据手册上对GPIO引脚的命令,不是严格按照顺序命名的,而是根据Table 28来命名的

32.6.157 SW_MUX_CTL_PAD_GPIO1_IO4 SW MUX Control

Register(IOMUXC_SW_MUX_CTL_PAD_GPIO1_IO04)

可与看出,设置成0101:ALT5->普通GPIO模式

四、引脚属性

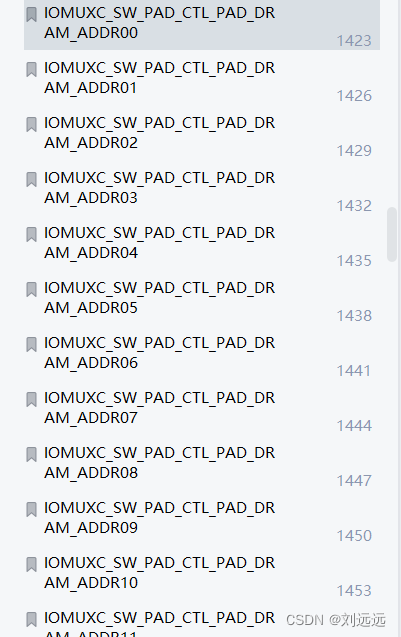

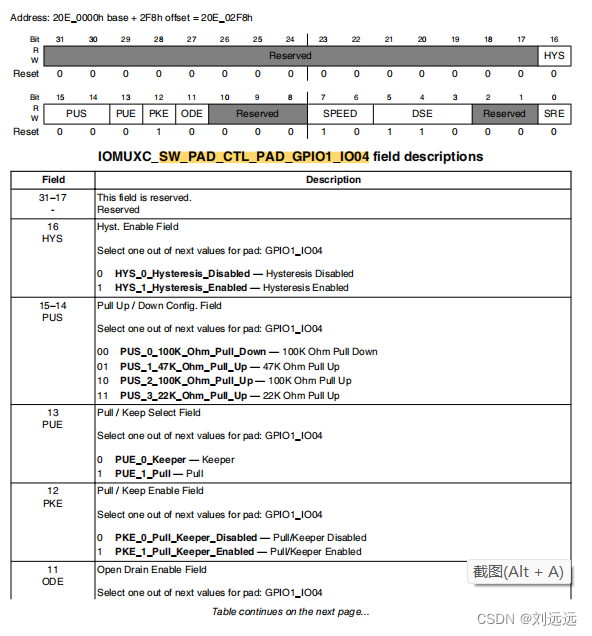

相关寄存器:IOMUXC_SW_PAD_CTL_PAD_XXX

数据手册:

注意:数据手册上对GPIO引脚的命令,不是严格按照顺序命名的,而是根据Table 28来命名

32.5.186 SW_PAD_CTL_PAD_GPIO1_IO04 SW PAD Control Register(IOMUXC_SW_PAD_CTL_PAD_GPIO1_IO04)

-HYS(bit16):

-PUS(bit15-bit14):用来设置上下拉电阻的大小

-PUE(bit13):当IO作为输入的时候,这个位用来设置IO使用上下拉还是状态保持器

-PKE(bit12):用来使能或者禁止上下拉/状态保持器功能

-ODE(bit11):IO作为输出的时候,此位用来禁止或者使能开漏输出

-SPEED(bit7-bit6):当IO用作输出的时候,此位用来设置IO速度

-DSE(bit5-bit3):当IO用作输出的时候用来设置IO的驱动能力

-SRE(bit0):设置压摆率

控制GPIO引脚

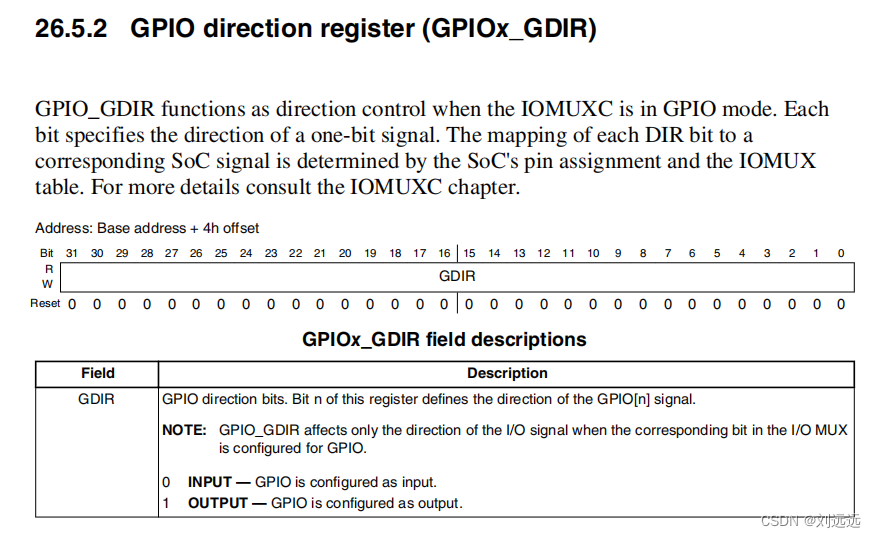

5组GPIO,每组GPIO有8个相关寄存器

- GPIOx_GDIR:设置引脚方向

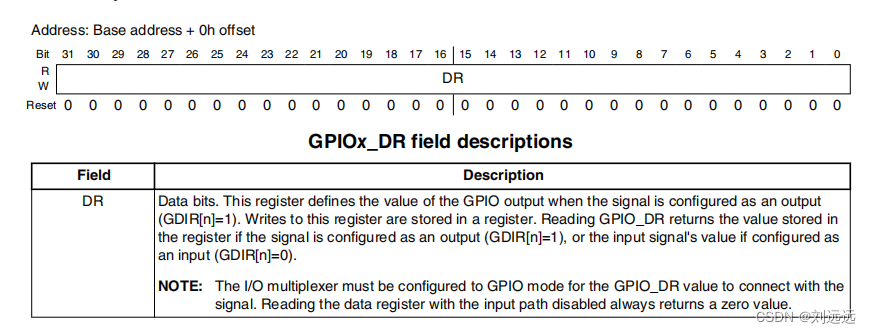

- GPIO_DR:设置输出引脚的电平

- ...

每个寄存器有32位,分别控制每位的gpio

26.5.2 GPIO direction register(GPIOx_GDIR)

-0:输入

-1:输出

26.5.1 GPIO data register (GPIO x _DR)

五、控制GPIO总结

- 使能GPIO时钟

- 设置引脚复用GPIO

- 设置引脚属性(上下拉、速率、驱动能力)

- 控制GPIO引脚输出高低电平

六、硬件原理图