今天中午午休我刚要打开手机的准备刷抖音看无忧传媒的学生们的“学习资料”的时候,看到CSDN -APP上有提醒,一看原来是一位道友发的一个问题:

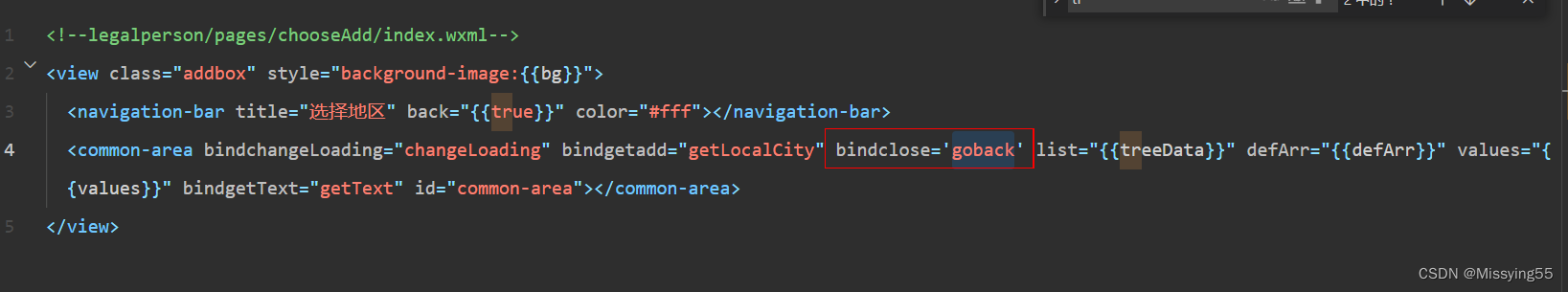

本来小编最近由于刚刚从国外回来,手上的项目都已经结束了,这周开始学习仿真测试验证呢,而且今天本来是准备开始写上次遗漏的一个问题点:下图红色标记的地方。

这个文章是之前发布的关于POC电感的,感兴趣或是忘记了的铁子们可以点击下面的链接去查阅之前的文章。

Marin说PCB之POC电路layout设计仿真案例---02

好了,既然氛围都已经衬托到这了,那小编就开始了今天的POC电感案例仿真验证了:

步骤:

一,在仿真软件中导入我们单板的层叠信息:

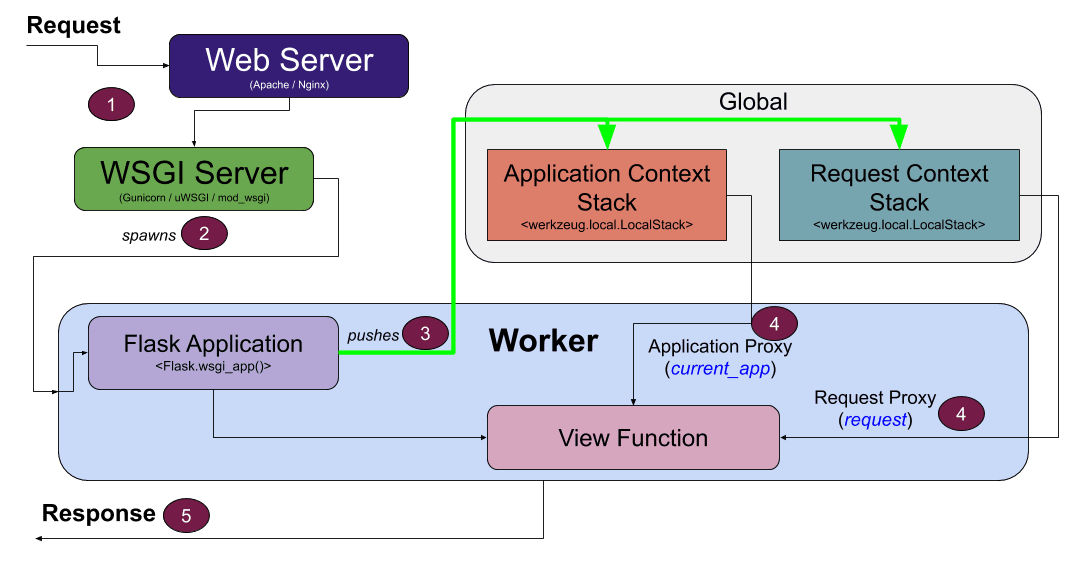

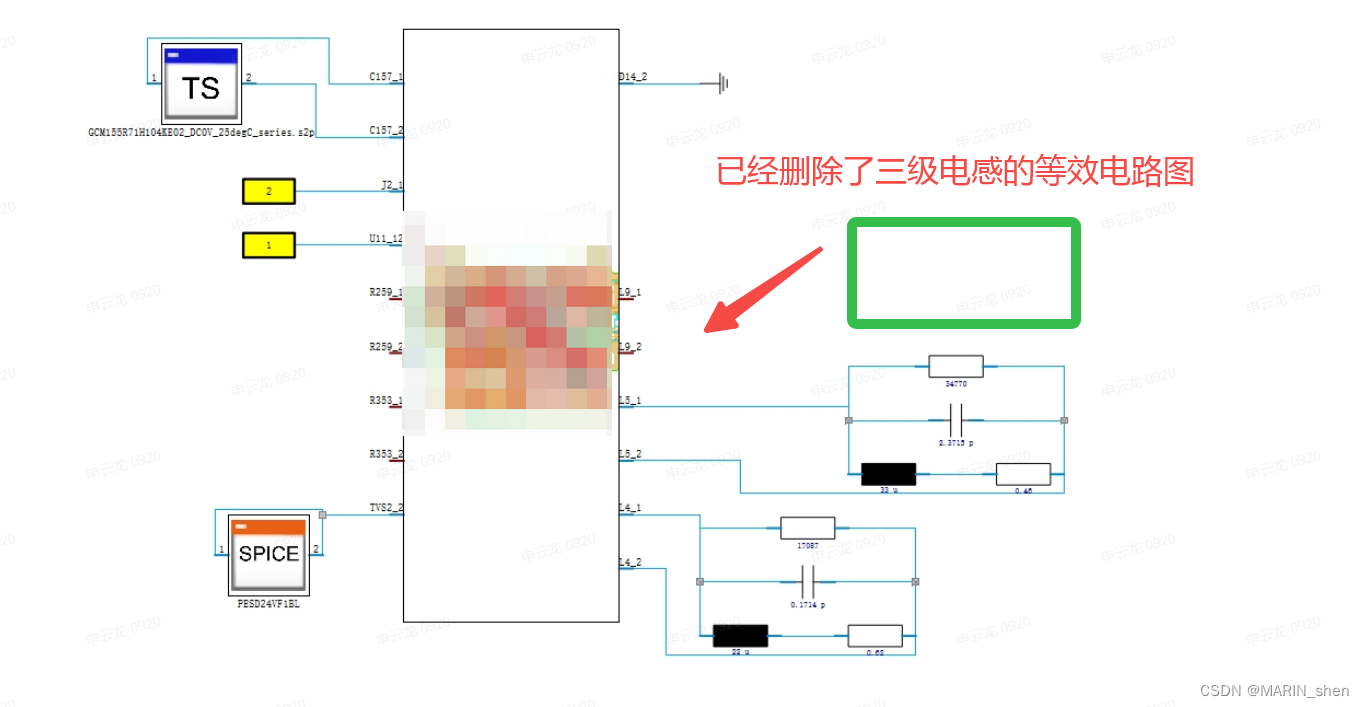

二,仿真原理的搭建,添加了电感的等效电路后的仿真电路图如下图,目前是已经把三级电感的等效电路图删除了,其设计中采用了GMSL 1 _3.125GBPS的速率配置。

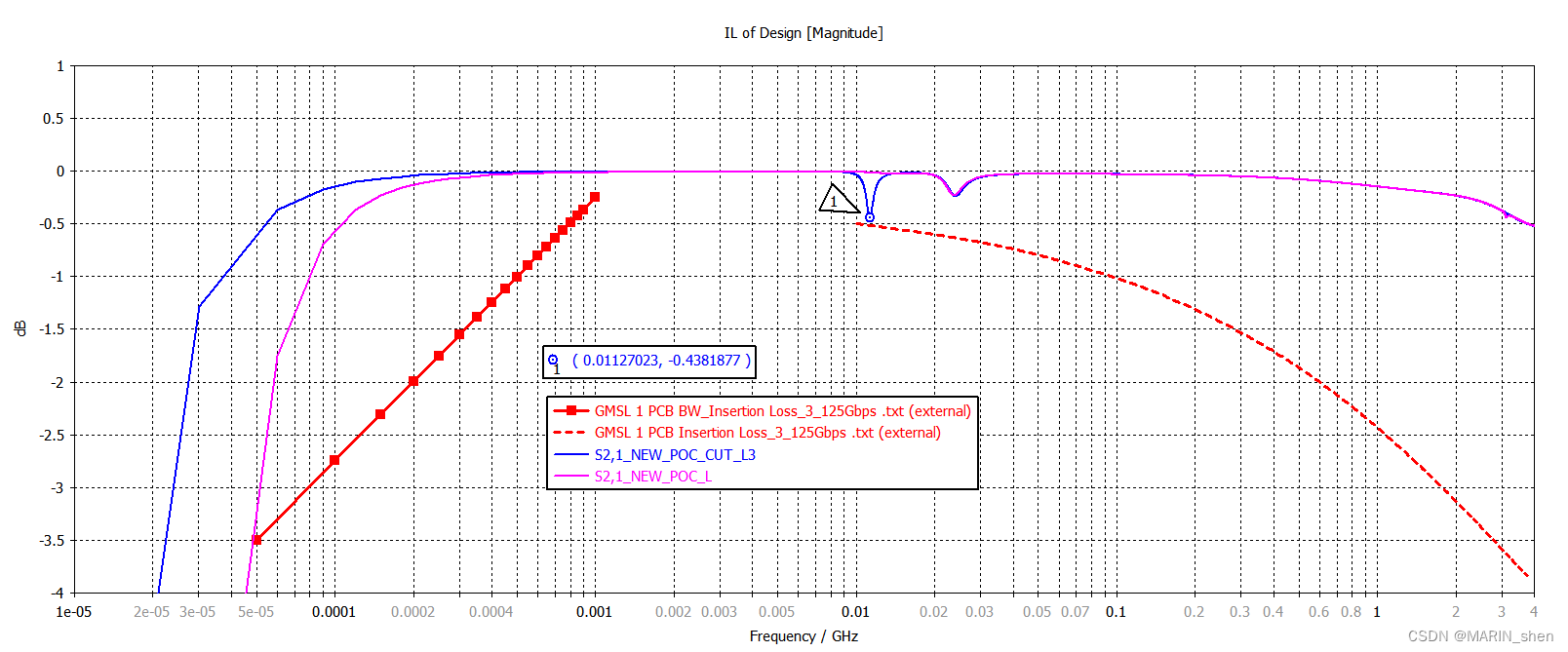

三,IL的仿真结果如下图所示:

四,RL的仿真结果如下图所示:

五,导入之前的完整的POC三级电感方案的IL的比对仿真结果如下图所示:

六,导入之前的完整的POC三级电感方案的RL的比对仿真结果如下图所示:

七,结论:从上面的两幅仿真结果显示POC三级电感的引入确实会改善其插损和回损的性能,在11.2MHz的时候串联一个相同型号的三级电感会把这个掉坑给优化好,其主要原因是我们串联一个型号相同电感相当于把其等效阻抗值抬升了。下面我们可以通过做一个仿真去验证这个理论。

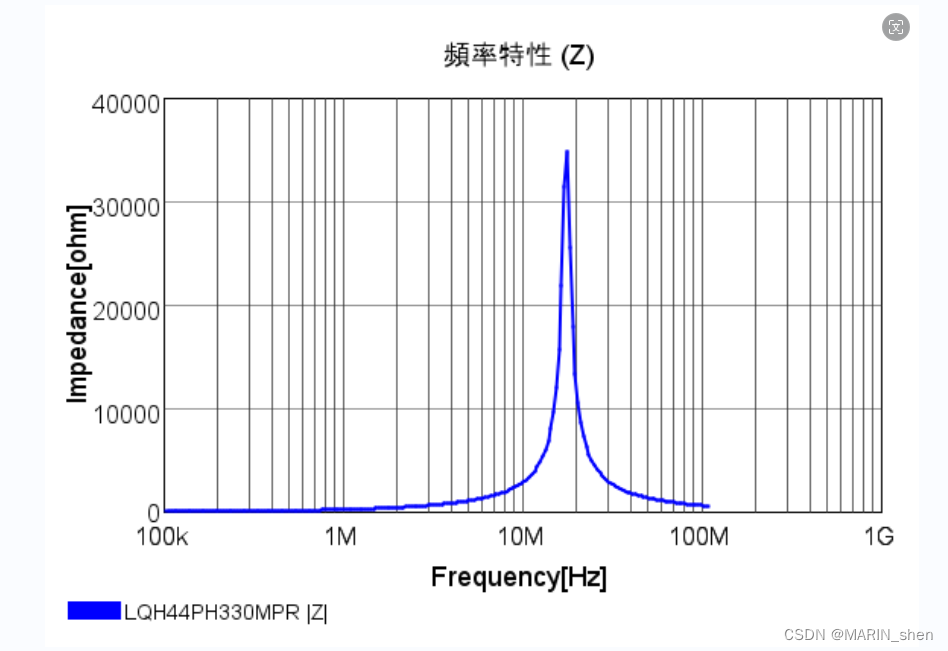

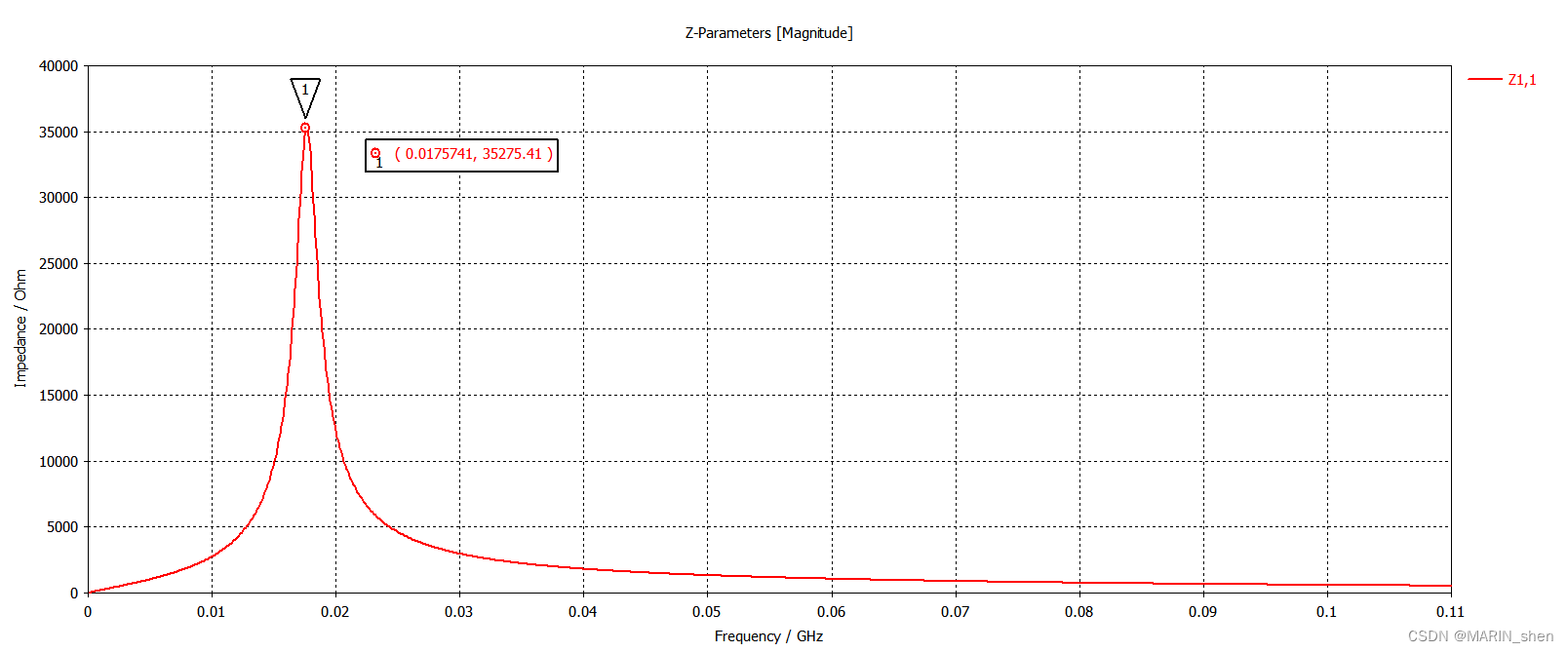

八,首先我们在官网上找到这颗电感的频率特性阻抗曲线图,然后我们在仿真软件中导入其S参数去比对是否和官网上的频率特性曲线一致,目前通过仿真比对来看整体是一致的。

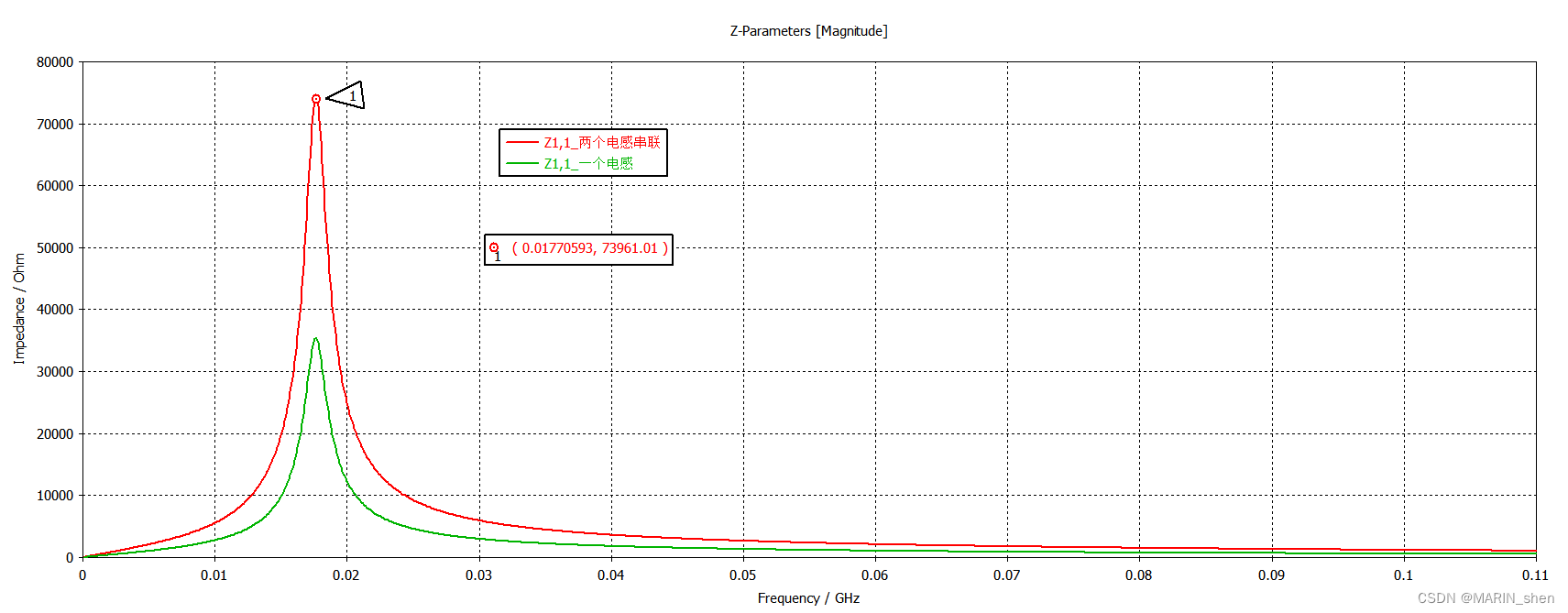

九,在仿真软中把这两个电感串联起来去观察其频率特性阻抗曲线图,如下图所示:

十,在仿真软中把这两个电感并联联起来去观察其频率特性阻抗曲线图,如下图所示:

十一,结论:从上面的两幅仿真结果显示POC三级电感的引入确实会改善其插损和回损的性能的主要原因是:两个型号相同的电感串联后,其总的等效阻抗Z是变大了很多了,从之前的Z=35275欧姆变成了73961欧姆,这样其总Q值变小了,POC电感的隔离度就变得很好了,最终体现在其插损和回损上就变小了。当然有人该说了你这个Q值是嘛意思啊?我听不懂啊,这个Q值我之前 文章中也是有提到这的知识点的,既然有人提问了,我这就在多啰嗦一句吧:

电感的Q值:电感的Q值也叫作品质因数,其为无功功率除以有功功率。简单理解的话,就是在一个信号周期内,无功功率为电感存储的能量,有功功率为电感消耗的能量。

Q=无功功率/有功功率

电感一般使用频率远小于其自谐振频率,因此寄生电容可以忽略,此时无功功率主要由电感产生,所以Q等于wL除以Rs

Q=无功功率/有功功率=JWL/Rs

这里有一点需要大家注意的是,这里的Rs并不是电感的直流导通电阻Rdc,它包含了电感的所有损耗,我们可以称之为等效串联总电阻。

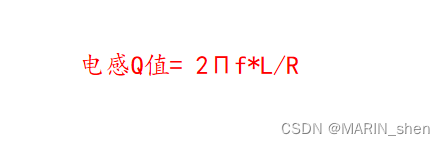

对电感来说,在某一频率的交流电压下工作时,所呈现的感抗与其等效损耗电阻之比。要计算线圈的Q值,请使用以下公式:

Q=2πFL/R

其中Q表示的是线圈的质量数值也就是我们常说的品质因子,F为频率,R则表示的是高频率的直接电阻的分量。

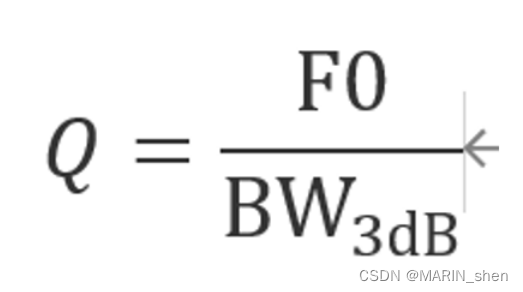

Q还有一个公式定义:

实线的曲线是高Q电感的曲线,虚线的是低Q的曲线;如之前有列过Q和Bw的公式,Q越大,Bw越窄,过了谐振点后的阻抗曲线下落明显,是否就意味着电容分量越大;Q越小,Bw越宽;是否也就意味着过了谐振点后电容分量更小;这样,降低Q值了,电路的反谐振的概率就低了。同样的道理,几个容值相差很多电容并联,也会产生反谐振,也是在当中串(注,电容的情况时串阻尼电阻)来破坏其反谐振点(其实也是降低了电容的ESL分量).

总的来说就是我们POC电路中的电感的阻抗增加了,其Q值是降低了,其隔离度就越好了,插损及回损就变的越小,对应的其S参数的插损和回损的曲线就很平滑了,不会出现掉坑的情况了。至于电感的Q值和其阻抗的关系为啥是反比的,感兴趣的铁子们可以自己课下推算一下,我也给大家补充说明一下吧:

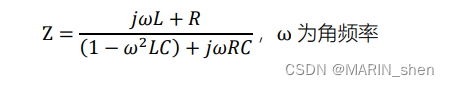

首先我们电感实际生产出来并不是理想电感,线圈匝数之间也会存在寄生电电容,线圈也不是超导体,会存在 直流电阻,所以,电感等效模型如下图。

电感模型由电感和电阻串联,然后和电容并联构成,很容易列出去复阻抗表达式:

这个R和我们上面的Q=2πFL/R中的R都是电感线圈的直流电阻DCR,(Q值的公示中R我们可以近视看做是其电感的直流电阻DCR,其他的一些磁芯材料磁滞损耗和涡流损耗;趋肤效应造成的损耗这些我们先忽略不计),最终经过推到我们可以得出结论就是:电感的Q值和其阻抗的关系是成反比的。

好了,以上就是本期的所有内容了,我们下期文章不见不散。看完记得点赞加关注,谢谢。