文章作者团队来自中国科学院苏州纳米技术与纳米仿生研究所(SINANO)的关键实验室、中国科学技术大学的纳米技术与纳米仿生学院,以及广东省(佛山)苏州纳米技术与纳米仿生研究所的分支机构。研究结果发表在IEEE Journal of Emerging and Selected Topics in Power Electronics ( Volume: 9, Issue: 3, June 2021)上。

本文研究了具有再生长p-GaN栅极和AlN/SiNx堆叠钝化的常关型高电子迁移率晶体管(HEMTs)的栅极可靠性及其退化机制。通过比较两种设计结构下的正向漏电流,确定了传导机制为Fowler-Nordheim(F-N)隧穿,该机制下电流与温度无关,当Pd/p-GaN肖特基结在高电场下时。即使对于再生长的p-GaN栅极,首先出现的是肖特基结的失效,导致栅极电流急剧增加。通过采用幂律和指数律作为外推拟合,分别估计了在室温下10年寿命内故障率为1%时的最大栅极操作电压约为6.87 V和6.07 V。退化过程监测显示,通过C-V拟合提取的净受主浓度NA呈现出从3.8×10^19到1.1×10^19 cm^-3的明显下降趋势,随着应力时间的增加。这被认为是与在高隧穿电流和高电场下肖特基耗尽区下缺陷的生成有关。这些分析表明,具有再生长p-GaN栅极和AlN/SiNx堆叠钝化的常关型HEMTs对于实际应用是可行的,并为进一步提高栅极击穿电压和寿命提供了方向。

I.引言

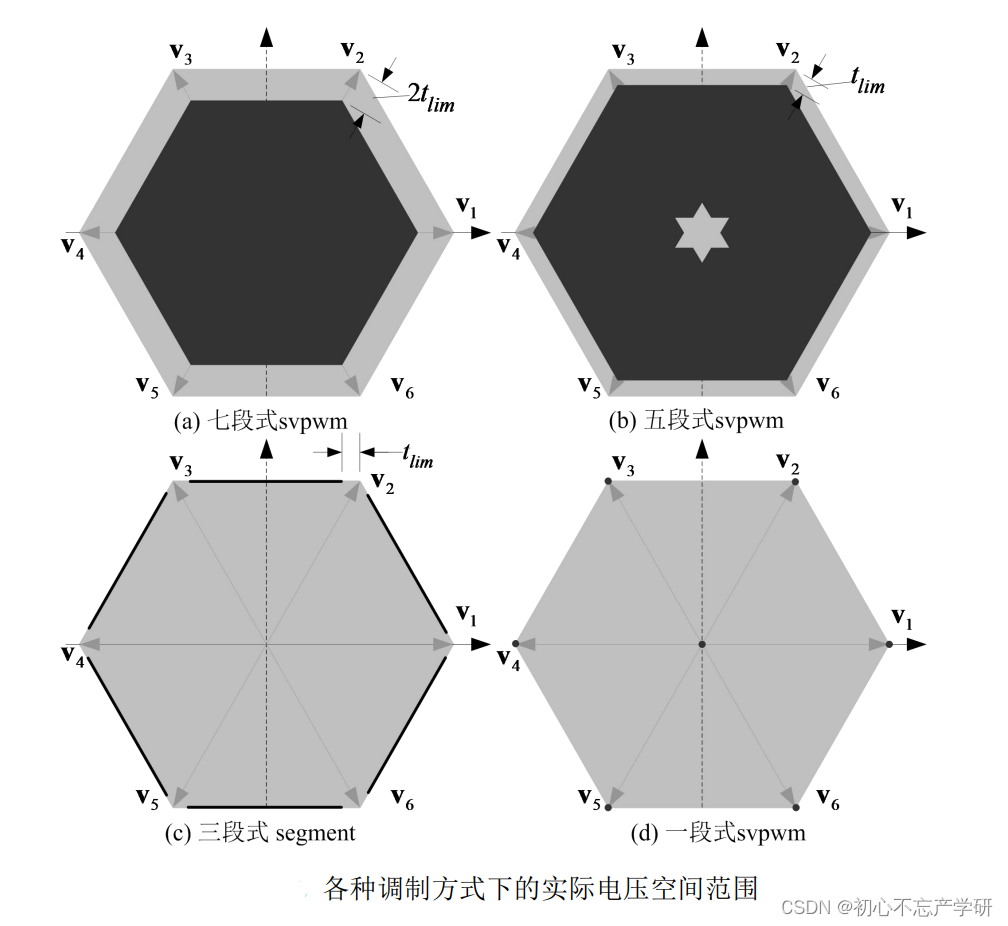

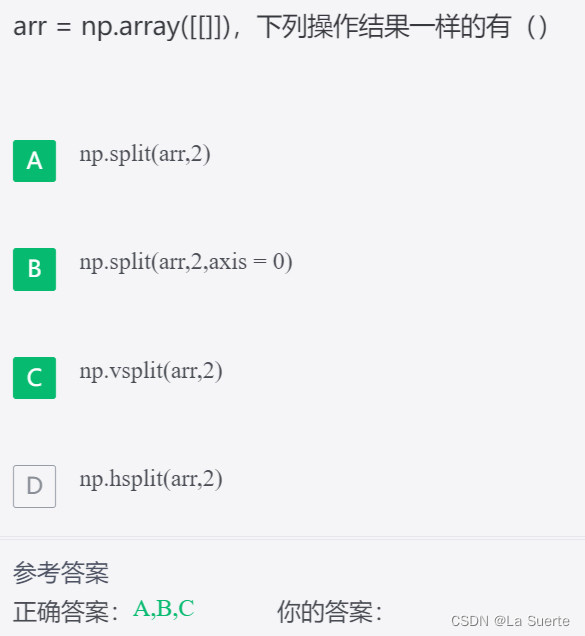

文章的引言部分详细介绍了氮化镓(GaN)基高电子迁移率晶体管(HEMTs)的背景、重要性、以及它们在功率开关设备中的应用前景。特别关注了常关型HEMTs,这是因为它们在操作安全性和驱动器设计简便性方面的优势而受到越来越多的关注。在多种常关型HEMTs技术中,p-GaN栅极解决方案(p-GaN E-HEMTs)因其在性能、可靠性、成本和市场方面的优势而成为商业应用的先驱。 为了解决高阈值电压和低导通态电阻之间的传统权衡问题,研究者提出了一种带有再生长p-GaN栅极的更厚的AlGaN势垒结构,并已成功制造。此外,为了实现可靠的开关性能,商业上采用了具有欧姆接触型或肖特基接触型的p-GaN栅极,并对其进行了研究。欧姆型栅极接触通常显示出更好的稳定性和可靠性,但代价是较大的栅极漏电流(IG),因此对低栅极偏压的容忍度较低;而具有肖特基接触的p-GaN栅极可以减少IG并增加栅极摆幅,但牺牲了栅极控制性和可靠性。 为了提高p-GaN栅极的性能,研究者在栅极导电机制、阈值电压(Vth)不稳定性、栅极失效时间(tBD)和机制等方面做了大量的工作。提出了一个双结模型来理解肖特基接触p-GaN栅极的电流泄漏和电容性能,这些性能主要由肖特基结(JS)和p-GaN/AlGaN/GaN异质结(JP)控制。Vth不稳定性归因于在快速开关过程中,p-GaN栅极内深陷阱捕获的电荷(空穴和电子),特别是在JS和JP中。此外,JS耗尽区在高电场下形成一条渗透路径被认为是栅极击穿的原因。 尽管这些研究大多基于传统的p-GaN E-HEMTs,但对于具有再生长p-GaN栅极的常关型HEMTs的栅极退化及其机制却鲜有报道。在这种HEMTs中,存在一个再生界面,当器件通过低压化学气相沉积(LPCVD)SiNx钝化时,还会引入另一个金属/p-GaN界面。在本工作中,讨论了这两个结的电流传导,并在退化过程中监测了栅极性能。通过分析图1中显示的两种不同结构,确认了在栅极应力下,常关型HEMTs与再生长p-GaN栅极和AlN/SiNx堆叠钝化的第一个退化的是JS。这种退化应归因于在高正栅极偏压下,肖特基耗尽区中缺陷的生成对Mg受主的补偿。通过本研究进一步改善栅极可靠性,具有再生长p-GaN栅极和AlN/SiNx堆叠钝化的常关型HEMTs对实际应用具有重要意义。 引言部分还概述了GaN基HEMTs在高频、高效率功率开关设备中的潜力,尤其是常关型HEMTs因其操作安全性和驱动器设计的简便性而受到重视。文中提到了p-GaN门解决方案(p-GaN E-HEMTs)在商业应用中的领先地位,以及为了克服高阈值电压和低导通态电阻之间的权衡问题,提出的更厚的AlGaN势垒结构和再生长p-GaN栅极的解决方案。此外,还讨论了栅极接触类型对器件性能的影响,包括欧姆型和肖特基型栅极接触的优缺点。文中还提到了对栅极性能影响的研究工作,包括栅极导电机制、阈值电压不稳定性、栅极失效时间和机制等。最后,引言指出了本研究的目的,即通过分析两种不同结构的器件,来确认在栅极应力下哪种结构最先退化,并探讨退化机制,以便为进一步提高栅极可靠性提供方向。

图1 具有 (a) 栅极金属/p-GaN/AlGaN/GaN/S&D 结构(结构 A)和 (b) 栅极金属/p-GaN/栅极金属结构(结构 B)的器件示意图。它们的简化等效电路如(c)和(d)所示。

II.器件制造核表征

-

异质结构生长:使用金属有机化学气相沉积(MOCVD)技术在硅(111)衬底上生长了Al0.2Ga0.8N/GaN异质结构。这包括一个无故意掺杂的GaN沟道层,一个C掺杂的Al0.07Ga0.93N缓冲层,以及AlGaN/AlN应力工程层。

-

p-GaN栅极的再生长:在栅极区域,约40纳米厚的Al0.2Ga0.8N势垒层被蚀刻掉大约25纳米,以便重新生长一层大约100纳米厚的p-GaN,该p-GaN具有大约3×10^19 cm^-3的Mg掺杂水平。通过在850°C下进行30分钟的氮气氛围原位退火来激活Mg掺杂。

-

栅极形成:使用慢速率感应耦合等离子体(ICP)刻蚀技术有选择性地移除p-GaN以形成栅极。之后,通过低压化学气相沉积(LPCVD)沉积SiNx层,并对其进行图案化,以形成源(S)、漏(D)和栅(G)金属接触。

-

退火处理:为了恢复p-GaN,进行了950°C下的快速热退火处理,持续3分钟。

-

欧姆接触形成:在栅极势垒上沉积了Ti/Al/Ti/Au(6/120/20/30 nm)的金属堆叠,用于形成S/D低温欧姆接触,其接触电阻在550°C退火3分钟后约为1.0 mΩ·mm。

-

栅极金属沉积:最后,沉积了Pd作为栅极金属。

-

器件结构:在同一个晶片上制备了两种不同结构的器件(结构A和结构B)。结构A是典型的常关型HEMT,具有再生长的p-GaN栅极。而结构B的Al0.2Ga0.8N势垒被减薄至约15 nm,并且保留了再生长的p-GaN。

-

后金属退火(PMA):在栅极金属沉积后,对两种结构的样品进行了350°C、400°C和500°C下氮气氛围中的1分钟PMA处理。

-

电流-电压(I-V)特性测量:测量了经过和未经过PMA处理的样品的温度依赖性I-V特性,温度范围从303 K到423 K,以20 K为步长。

-

栅极失效行为和寿命研究:对经过500°C PMA处理的结构A进行了研究,通过在VGS = 10.5、11.0和11.5 V下的应力测试,直到IGS急剧增加,测试了超过十个器件以获取统计数据。

-

步进应力测试:对结构A和结构B进行了步进应力测试,以分析栅极击穿过程。对于结构A,栅极电压(VGS)以1 V为步长从5增加到12 V。对于结构B,施加的电压(VB)以-5 V为步长从-10增加到-50 V。

-

高频特性监测:在VGS = 10.5 V的高电压应力测试下,对经过500°C PMA处理的结构A进行了高频特性监测,测试了应力30、100、200、600、1000、1400、1800、2200和2600秒后的转移特性和频率依赖性C-V特性。

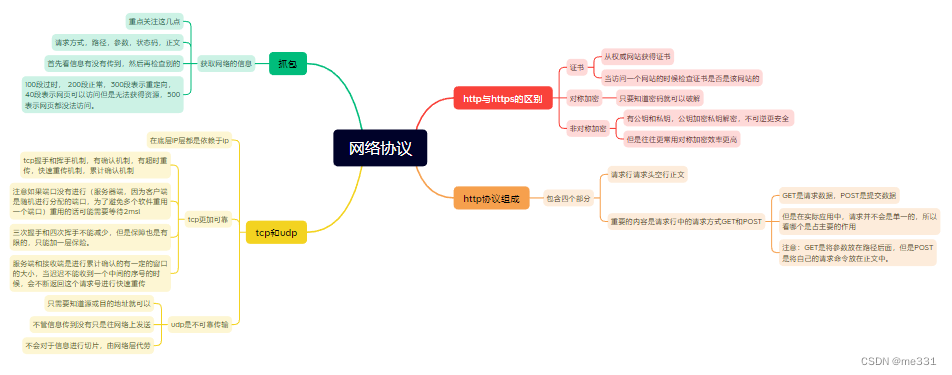

III.栅极传导及其漏电机制

A. 等效电路和电流分量

-

结构A和结构B的等效电路:

- 文章首先介绍了两种不同结构的HEMTs,分别是结构A(具有栅金属/p-GaN/AlGaN/GaN/源的结构)和结构B(具有门金属/p-GaN/栅金属的结构)。对于这两种结构,文章提出了它们的等效电路模型。

- 结构A的等效电路中,包含了并联的Pd/p-GaN肖特基结(JS)和p-n结(由p-GaN/AlGaN/GaN结构形成,记为JP),以及相应的电容(CS和CP)。

- 结构B的等效电路则展示了Pd/p-GaN肖特基结的并联(记为C1和D1,C2和D2),以及与p-GaN层相关的电阻器R。

-

电流分量的表示:

- 在结构A中,当测量电学特性时,源极接地,栅极施加偏压。因此,通过JS和JP的电流(IS和IP)在两个结点上是相等的,因为它们是串联的。

- 当栅极偏压VGS施加时,将导致通过JS和JP的共同栅极电流IGS流过,对应于各自的电压降VS和VP。因此,VGS等于VS和VP的总和。

-

电压和电流的关系:

- 文章进一步解释了IGS与VGS之间的关系,指出IGS由反向偏置的结决定,因此结构A的IGS-VGS曲线可以通过图2(a)中的粗绿色线表示。

- 对于结构B,当测量时,p-Ct_1接地,而p-Ct_2施加偏压。基于图1(d)的等效电路,D1在负电压下占主导,而D2在正电压下占主导。因此,当特定的IB流过时,p-Ct_1和p-Ct_2之间的施加电压(VB)由VD(反向偏置二极管上的电压降)和VR(与p-GaN层相关的电阻器上的电压降)之和给出。

-

等效电路的简化:

- 文章通过简化的等效电路图(图1(c)和1(d))来表示两种结构的电流分量,其中结构A和结构B的电流分量分别在图2(a)和2(b)中进行了图解。

-

PMA对肖特基势垒高度的影响:

- 文章还讨论了后金属退火(PMA)处理对肖特基势垒高度的影响,指出在没有PMA时,肖特基势垒高度为1.82 eV,而经过PMA处理后,势垒高度会降低。

-

电阻器R的考虑:

- 对于结构B,文章指出由于p-GaN层电阻器的电阻较大,不能忽略,因为它会导致显著的偏压降。

通过上述分析,文章建立了两种不同结构HEMTs的电流传导模型,并解释了在不同偏压条件下,电流是如何在肖特基结和p-n结之间分配的。

B. 与温度相关的 I-V 特性

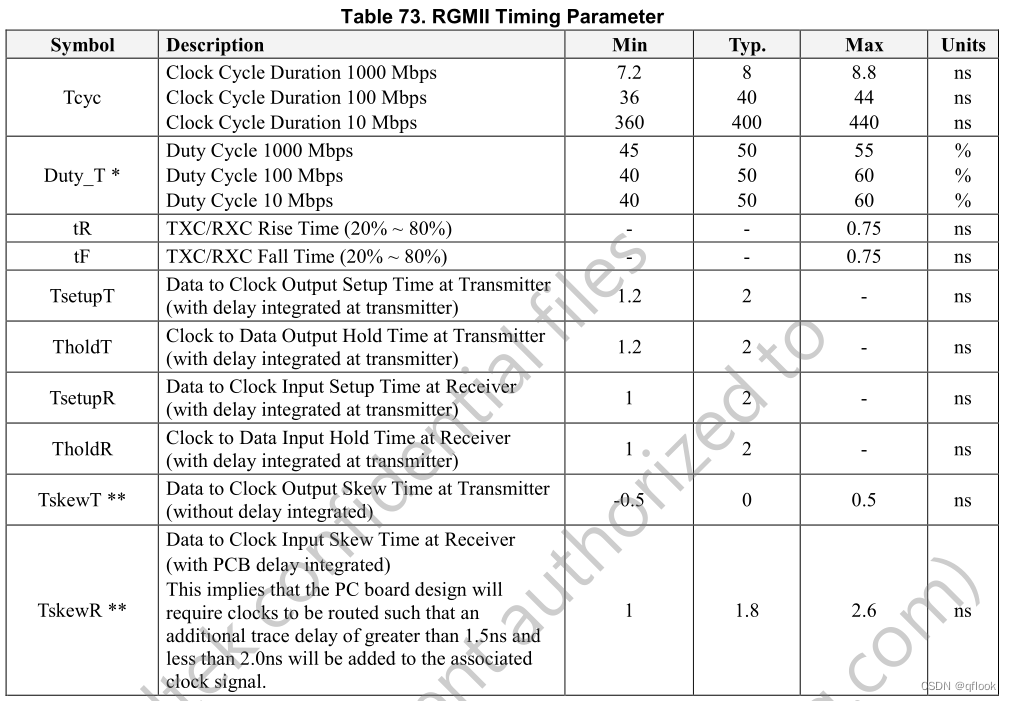

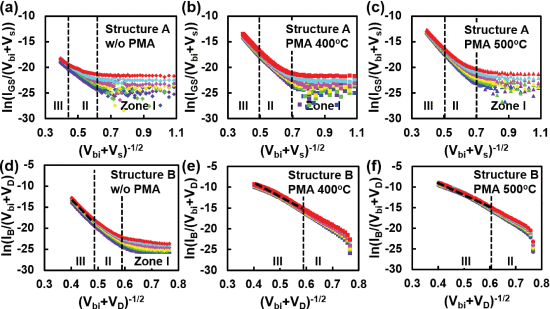

图3 (a)–(c) 无 PMA 和有 PMA 的结构 A 在 400 °C 和 500 °C 时的栅极电流以及 (d)–(f) 不带 PMA 和带 PMA 的结构 B 在 400 °C 和 500 °C 时随温度变化的栅极电流。

-

温度依赖性测试:

- 文章测量了在不同温度下,结构A和结构B的栅极电流(IGS和IB)随温度变化的特性。测试温度范围从303 K到423 K,以20 K为步长。

-

结构A的I-V曲线分区:

- 对于结构A,I-V曲线根据电流随温度的依赖性被划分为三个区域:

- 区域I:由p-n结(JP)主导,漏电流与温度强烈相关,表明可能是由热发射引起的。

- 区域II:显示了肖特基结(JS)处的热场发射(TFE)机制,与空穴的行为有关。

- 区域III:在该区域,温度对栅极电流的影响很小,表明载流子可能在没有热帮助的情况下通过隧穿过程穿过势垒。

- 对于结构A,I-V曲线根据电流随温度的依赖性被划分为三个区域:

-

结构B的I-V曲线特点:

- 对于结构B,由于没有p-n结(JP),理论上在IB与VB曲线中找不到类似区域I的特性。然而,在未进行PMA处理的设备中,类似的区域I出现了,这可能归因于栅金属和p-GaN之间的界面态。

-

PMA对I-V特性的影响:

- 文章观察到,随着PMA处理温度的提高,区域III的最小电压降低,且在VGS = 6 V时,IGS在PMA处理后的值比未处理前增加了超过两个数量级,这表明JS上的隧穿势垒由于PMA处理而降低。

-

隧穿电流的观察:

- 文章指出,在结构A和结构B中,Pd/p-GaN肖特基结在相对较高的正偏压下可能发生隧穿电流,且隧穿势垒会随着PMA处理和退火温度的提高而降低。

-

Fowler-Nordheim (F-N) 隧穿:

- 文章通过分析结构A和结构B的I-V曲线,确认了在Pd/p-GaN肖特基结中确实发生了F-N隧穿,这在区域III的曲线中表现为线性关系。

-

温度对隧穿电流的影响:

- 文章还分析了温度变化对隧穿电流的影响,发现在结构B中,随着PMA处理温度的提高,IGS增大,并且随着PMA处理温度的增加而增大。

-

隧穿势垒高度的变化:

- 文章通过分析不同PMA处理温度下的I-V曲线,发现在结构B中,线性部分的斜率随着PMA处理温度的增加而减小,表明肖特基势垒高度随着退火温度的增加而降低。

通过详细的温度依赖性测试和分析,揭示了在不同结构的HEMTs中,栅极电流的传导机制,特别是隧穿电流在栅极失效中的作用,以及PMA处理如何影响栅极电流的温度依赖性。

C.反偏置肖特基结中的 Fowler-Nordheim 隧穿效应

-

肖特基结的耗尽区宽度:

- 文章首先讨论了在高正栅极偏压下,Pd/p-GaN肖特基结的耗尽区宽度(W)的计算。由于高掺杂浓度,耗尽区宽度非常窄,大约为10纳米。

-

平均电场强度:

- 由于耗尽区非常窄,文章采用了平均电场强度(E)来进行定量分析。计算得到的平均电场强度超过3 MV/cm,这是一个足够大的值,可以预期产生隧穿电流。

-

Fowler-Nordheim(F-N)隧穿电流密度:

- 文章利用F-N隧穿理论计算了隧穿电流密度(J),其中包括了隧穿有效质量(m*T)、肖特基势垒高度(∅B)和普朗克常数(h)等参数。

-

隧穿电流与电压的关系:

- 通过F-N隧穿理论,建立了电流密度(J)与电压(Vbi + VS/D)之间的关系,并引入了系数k和b来描述这种关系。

-

肖特基势垒高度的计算:

- 文章进一步讨论了如何计算肖特基势垒高度(Vbi),并考虑了p-GaN的工作函数、电子亲和力、带隙、价带态密度和金属工作函数等因素。

-

隧穿电流的温度独立性:

- 通过实验数据,文章证实了在高正栅极偏压下,IGS主要由JS的F-N隧穿电流决定,并且这种隧穿电流与温度无关。

-

PMA对隧穿势垒高度的影响:

- 文章通过对比不同PMA处理温度下的I-V曲线,发现PMA处理可以降低肖特基势垒高度,并且随着退火温度的增加,势垒高度进一步降低。

-

隧穿电流的实验验证:

- 文章通过测量不同PMA处理温度下结构B的I-V曲线,验证了F-N隧穿在Pd/p-GaN肖特基结中的发生,并通过提取的数据分析了肖特基势垒高度的变化。

-

隧穿机制的总结:

- 文章总结了在反向偏置的Pd/p-GaN肖特基结中,高电场导致了F-N隧穿机制的发生,这一机制对于理解栅极电流的增加和栅极退化过程至关重要。

这部分的研究揭示了在高正栅极偏压下,Pd/p-GaN肖特基结中隧穿电流的物理机制,并展示了制造过程中的热处理步骤如何影响隧穿势垒和栅极电流的特性。

图4 (a)–(c) 有无 PMA 结构 A 在 400 °C 和 500 °C 下的 ln(J/Vbi+VS/D) 和 1/(Vbi+VS/D)1/2 之间的温度依赖性关系以及 (d)–(f ) 分别在 400 °C 和 500 °C 下不含 PMA 和含 PMA 的结构 B。

图5 (a) I – V 结构 B 在不同 PMA 条件下的特性以及 (b) ln(IB/Vbi+VD) 和 1/(Vbi+VD)1/2 之间的转换关系。 (c) 结构 A 负偏压下的温度相关 IGS∼VGS 曲线,以及 (d) 提取的 ln(J/T2) 和 −(q/kT) 之间的关系。

IV.栅极击穿特性及分析

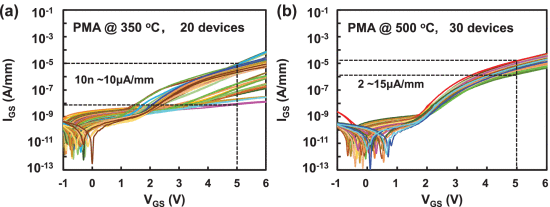

正向 IGS 与栅极击穿特性 [28] 、 [34] 有很强的关系。在 350 °C 和 500 °C 下测量具有 PMA 的器件的 IGS 均匀性,测量范围为 -1 至 6 V,分别如 Fig. 6(a) and (b) 所示。对于 350 °C 时采用 PMA 的器件, IGS 在 VGS=5 V 时变化 3 个数量级,从 10 nA/mm 到 10 μA /mm,而仅从 2对于具有 PMA 的器件,温度为 500 °C 时为 15 μA /mm。由于均匀性良好,这部分的栅极击穿特性都是在 PMA 器件上在 500 °C 下测量的。

图6 使用 PMA 的器件在 (a) 350 °C 和 (b) 500 °C 时的 IGS 均匀性。对于 350 °C 时采用 PMA 的器件, IGS 在 VGS=5 V 时变化 3 个数量级,从 10 nA/mm 到 10 μA /mm,而从 2 到 15 μA /mm 适用于 500 °C 下具有 PMA 的器件。

A. 栅极击穿和失效时间(Time-to-Failure, TTF)

-

栅极退化测试:

- 通过施加恒定的正栅极电压(10.5V、11.0V或11.5V),测量了栅极电流(IGS)随时间的增加情况。测试中,源极和漏极接地。

-

栅极击穿特性:

- 观察到IGS在数秒内随着应力时间的增加而增加,随后在栅极突然击穿前有所下降。

-

失效时间(TTF)的统计分析:

- 栅极击穿时间(tBD)或TTF遵循Weibull分布。通过拟合数据点,得到了分布函数(F)与tBD之间的关系,并提取了形状因子(β)。

-

栅极电压的寿命预测:

- 使用幂律和指数律作为外推拟合方法,预测了在室温下,对于10年寿命和1%的失败率,栅极电压的最大值分别为6.87V和6.07V。

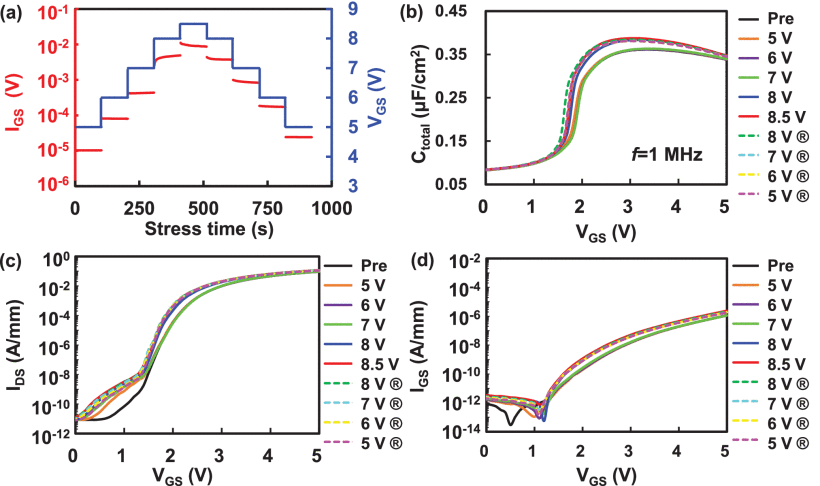

B. 步进应力电压测量(Step Stress Voltage Measurement)

-

应力电压应用:

- 对结构A和结构B分别从5V到12V和从-10V到-50V,以1V和5V的步长施加步进应力电压,每个步骤持续100秒。

-

栅极电流和击穿电压:

- 结构A的栅极击穿电压相对较低(12V),这表明大部分电压在JS上掉下,导致击穿。而结构B的反向电流在电压增加时仅增加了约一个数量级。

-

栅极电流的增加现象:

- 在结构A中,IGS在7V和8V的应力下随时间增加,但在更高的电压应力下则有所下降。而在结构B中,未观察到IGS随应力时间增加的现象。

-

栅极击穿机制:

- 结构A的IGS-VGS特性表明,JS首先失效,表现为p-n结的特性。进一步增加应力电压至13V,导致反向栅极电流大幅增加,表明JP的阻断能力因JP的失效而丧失。

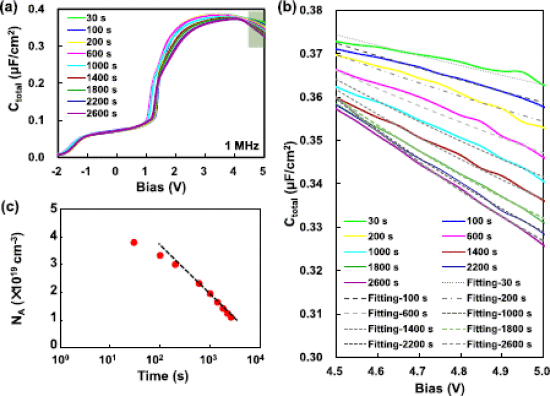

C. 栅极应力过程中的退化过程监测

-

时间依赖的栅极电流:

- 在10.5V的恒定正向偏压下,监测了结构A的时间依赖性栅极电流。

-

转移特性和阈值电压的变化:

- 测量了不同应力时间点的转移特性,发现亚阈值电流在应力后增加并随后稳定,而栅极漏电流(IG)在应力时间增加后趋于更高并相对稳定。

-

阈值电压的负向漂移:

- 阈值电压(Vth)在应力初期呈现负向漂移,随后随着应力时间的增加而略有恢复。

-

C-V特性的监测:

- 在栅极应力过程中监测了频率依赖的C-V特性,发现C-V曲线的峰值随着应力时间的增加而增加,表明CS(由p-GaN肖特基结决定的电容)随着应力时间的增加而退化。

D. C-V拟合和NA的减少

-

C-V特性的拟合:

- 使用C-V特性数据,通过拟合计算提取了净受主浓度(NA),发现NA从3.8×10^19 cm^-3下降到1.1×10^19 cm^-3。

-

退化机制的假设:

- 假设在高隧穿电流和高电场下,JS的耗尽区中缺陷的生成可能是退化的原因。

E. 可能的退化机制

-

高电场下的退化过程:

- 在高正栅极偏压下,形成高电场,导致F-N隧穿,以及由2DEG注入的电子和由碰撞电离产生的电子-空穴对在耗尽区的加速。

-

缺陷的生成和补偿:

- 高能量的载流子与晶格碰撞,生成缺陷或激活现有缺陷,这些缺陷可以捕获空穴或释放电子,从而补偿有效的Mg受主,导致NA显著下降。

-

肖特基结的失效:

- 随着应力时间的增加,p-GaN层中缺陷的不断生成,导致空穴和电子能够通过缺陷路径流动,而无需克服肖特基势垒,最终导致JS的失效。

V.结论

研究表明,通过比较不同结构,确定了Fowler-Nordheim(F-N)隧穿是栅极电流增加的主要机制,且该机制在高正栅极偏压下独立于温度。

进一步,文章预测了在室温下,对于10年寿命和1%的失效率,通过幂律和指数律外推拟合得出栅极工作电压的最大值分别约为6.87V和6.07V。

退化过程的监测揭示了随着应力时间的增加,通过C-V拟合得到的净受主浓度NA显著下降,表明在高隧穿电流和高电场下,肖特基耗尽区中的缺陷生成可能是导致退化的原因。

这些发现为进一步提高栅极可靠性提供了方向,并确认了采用再生长p-GaN栅极和AlN/SiNx堆叠钝化的常关型HEMTs在实际应用中具有巨大的潜力。