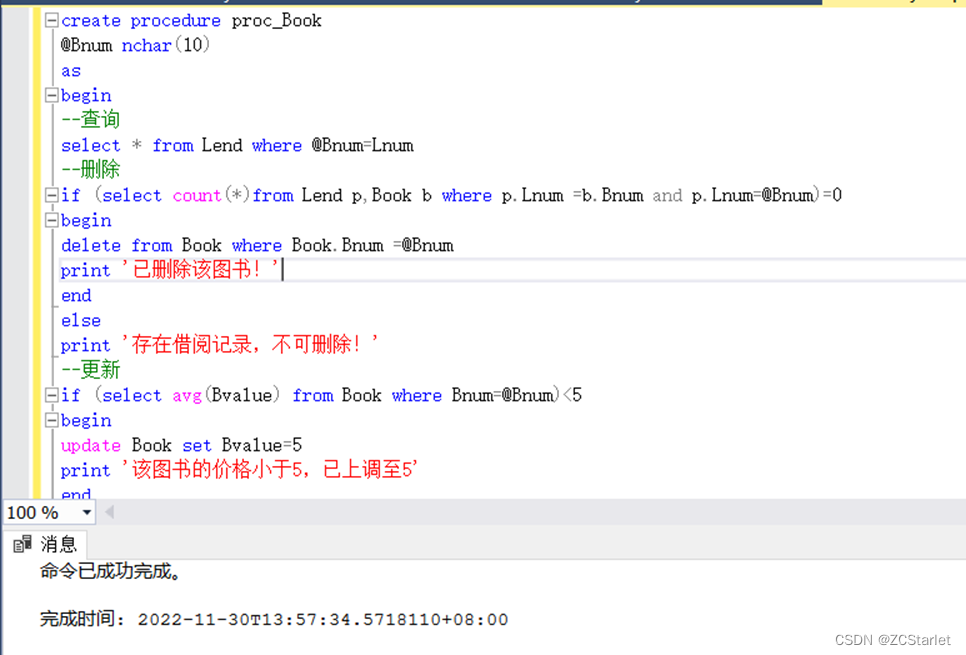

一、说明

RGMII(Reduced Gigabit Media Independent Interface)是Reduced GMII(吉比特介质独立接口),旨在替代IEEE802.3u MII、IEEE802.3z GMII和TBI。主要目标是将MAC和PHY互连所需的引脚数量从最大28个引脚(TBI)减少到12个引脚,为了实现这一目标,将减少数据路径和所有相关的控制信号,并且将控制信号多路复用在一起,并且将使用时钟的两个边沿。RGMII支持传输速率:10M/100M/1000Mb/s ,其对应CLK信号分别是2.5MHz、25MHz和125MHz。

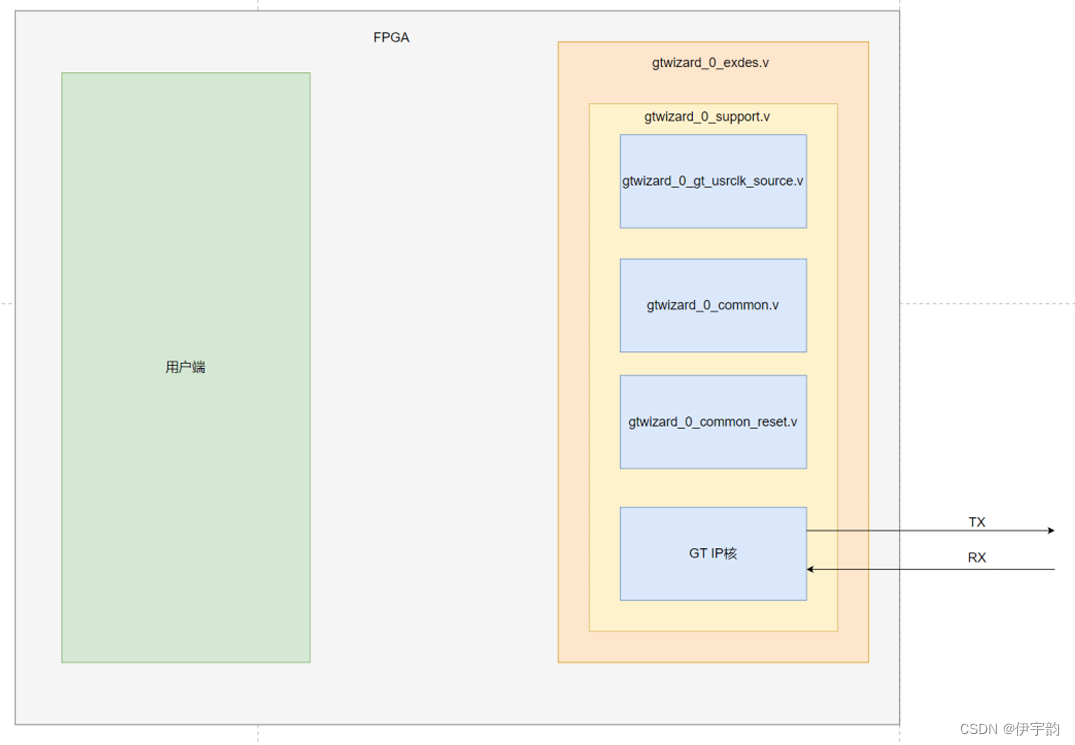

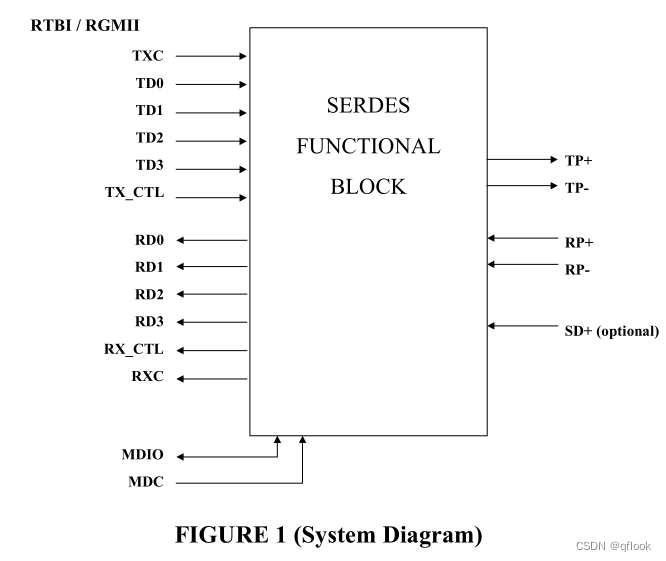

系统框图如下:

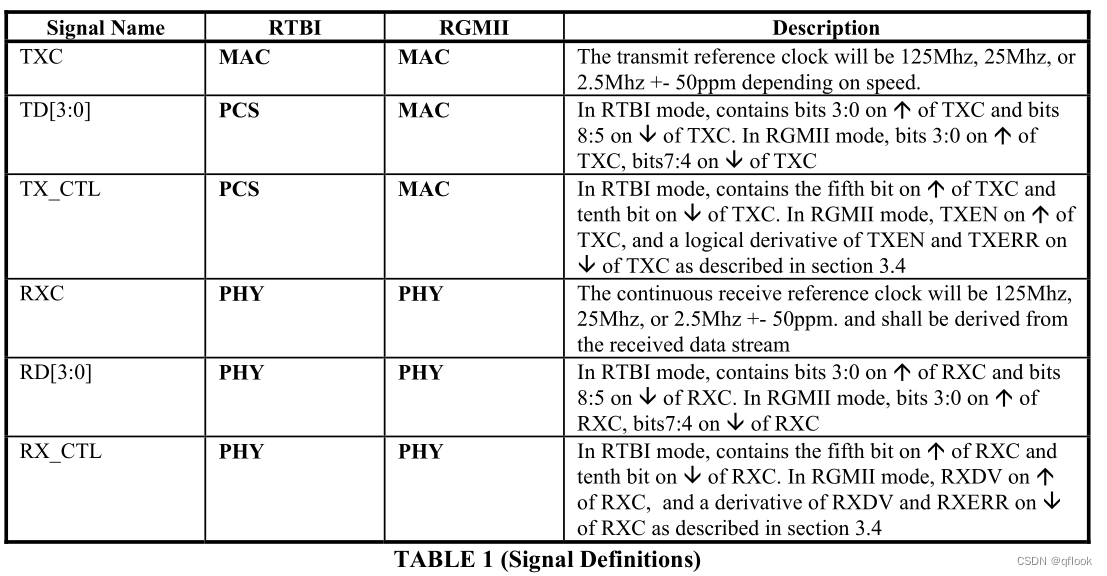

二、信号定义

二、信号定义

RGMII将与简化十位接口(RTBI)共享四个数据路径信号,并与第五个数据信号共享控制功能。通过包MDIO/MDC串行管理信号,RTBI将不需要独立的控制信号,如LK_REF、BYTE_EN等。SERDES控制位的寄存器分配留给设计者。

从上表可以看的,TXC/RXC是时钟信号,TD【3:0】/RD【3:0】在时钟上升沿时是RGMII的低4位,时钟下降沿是RGMII的高4位;对于RTBI模式的话,时钟上升沿是低4位,时钟下降沿是第9~6位(bits8:5);TX_CTL/RX_CTL对于RGMII模式,在时钟上升沿是使能信号,在时钟下降沿是使能信号和错误信号的异或后的结果;对于RTBI模式,在时钟上升沿是第5位数据,在时钟下降沿是第10位数据。

从上表可以看的,TXC/RXC是时钟信号,TD【3:0】/RD【3:0】在时钟上升沿时是RGMII的低4位,时钟下降沿是RGMII的高4位;对于RTBI模式的话,时钟上升沿是低4位,时钟下降沿是第9~6位(bits8:5);TX_CTL/RX_CTL对于RGMII模式,在时钟上升沿是使能信号,在时钟下降沿是使能信号和错误信号的异或后的结果;对于RTBI模式,在时钟上升沿是第5位数据,在时钟下降沿是第10位数据。

总结下来就是,RGMII模式(TX举例)下,TXC是时钟,TD【3:0】是4个数据信号,TX_CTL传输使能和错误信号;RTBI模式,TXC是时钟,TD【3:0】和TX_CTL都是传输数据。

三、时序要求

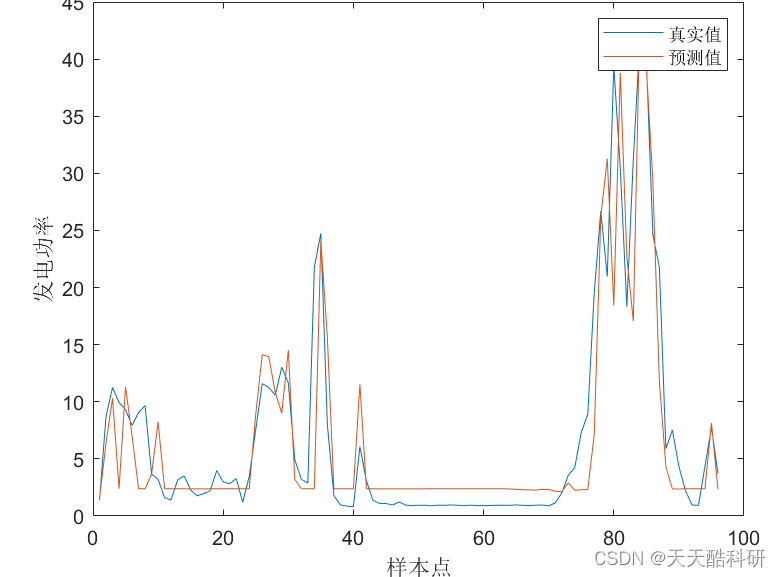

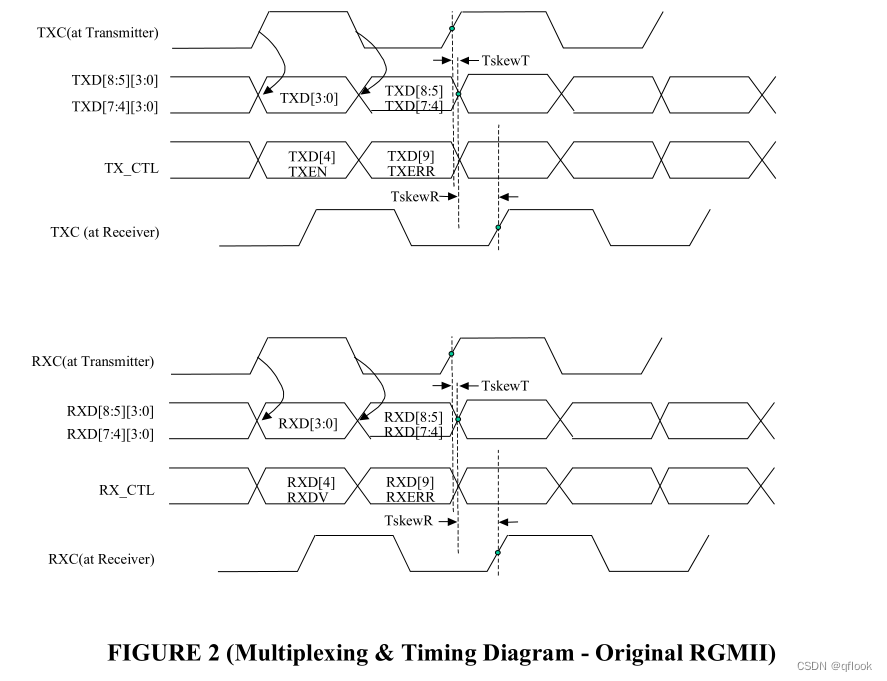

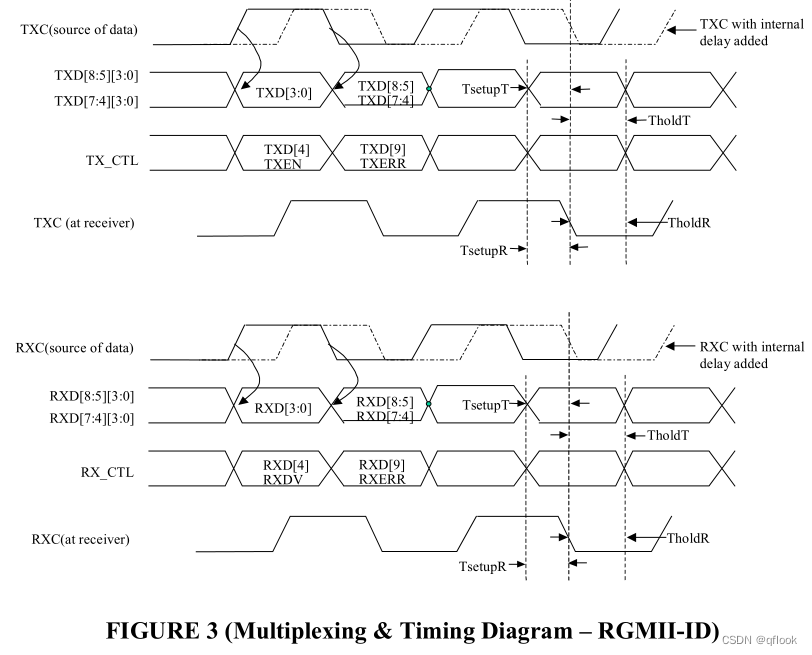

RGMII是双边沿采样(DDR),具体时序图如下:

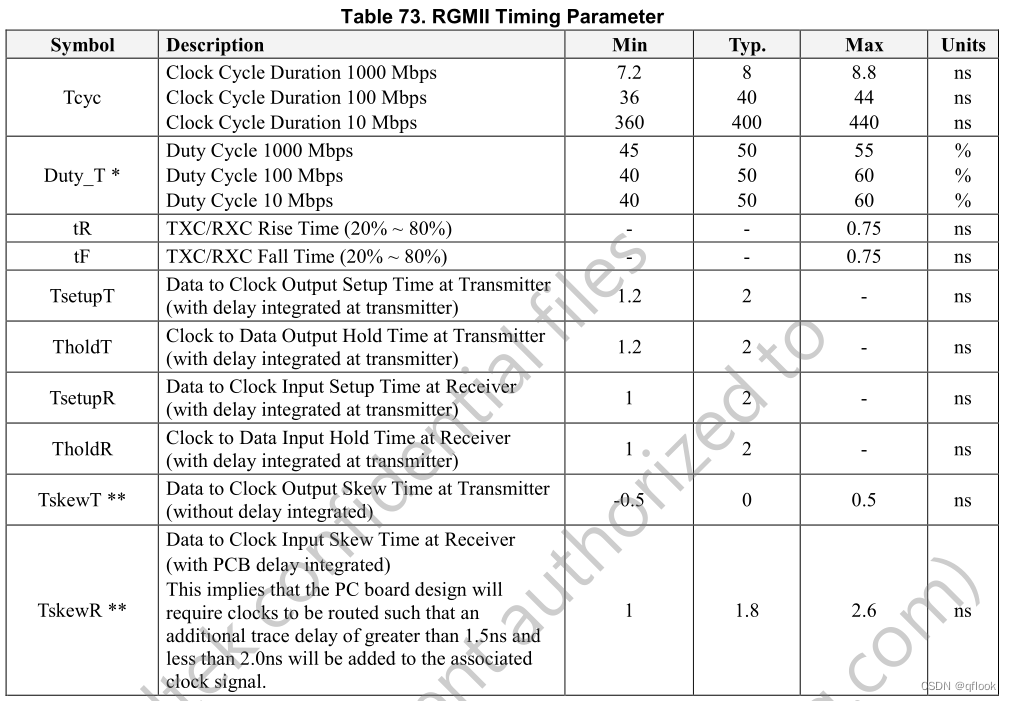

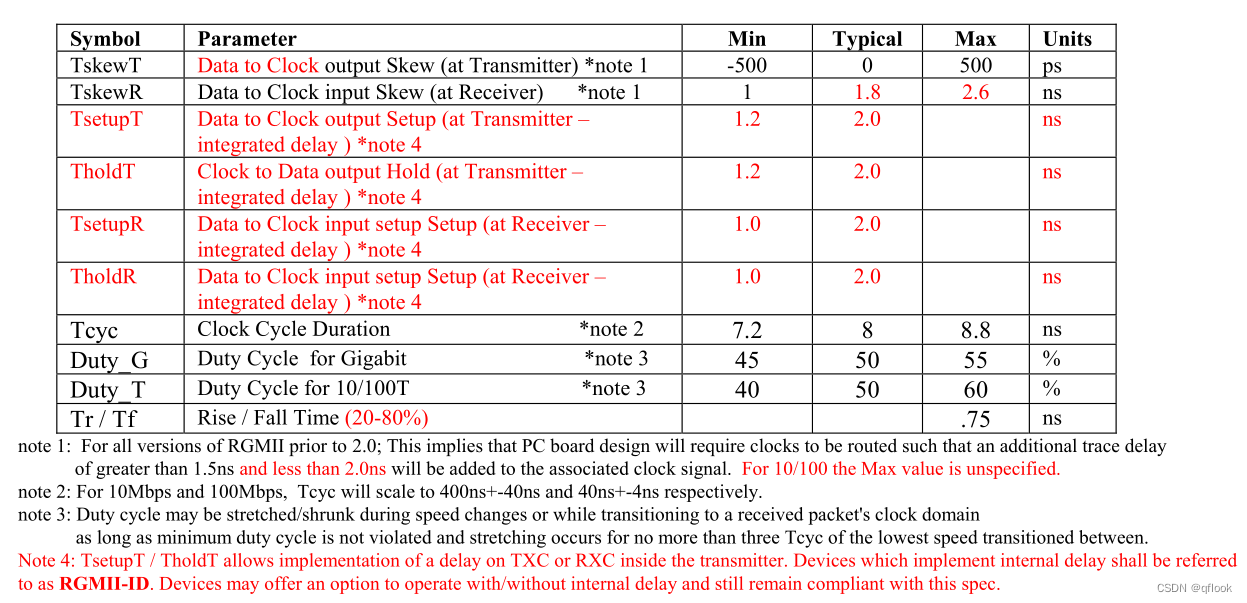

RGMII的时钟和数据由信号源同时生成,因此时钟和数据之间的偏斜对于正确操作至关重要。具体参数要求如下:

RGMII的时钟和数据由信号源同时生成,因此时钟和数据之间的偏斜对于正确操作至关重要。具体参数要求如下:

表格主要以1000M模式举例,备注中有10M/100M的要求。另外特别需要大家了解的是,实测建立保持时间很可能不满足规格要求,原因是芯片内部寄存器可以配置延时,因此实际的建立保持时间需要综合上软件配置的延迟时间,才是实际的建立保持时间。表格中Tr和Tf测试时需保证足够的有效带宽(示波器+探头+正确的测试方法)。

表格主要以1000M模式举例,备注中有10M/100M的要求。另外特别需要大家了解的是,实测建立保持时间很可能不满足规格要求,原因是芯片内部寄存器可以配置延时,因此实际的建立保持时间需要综合上软件配置的延迟时间,才是实际的建立保持时间。表格中Tr和Tf测试时需保证足够的有效带宽(示波器+探头+正确的测试方法)。

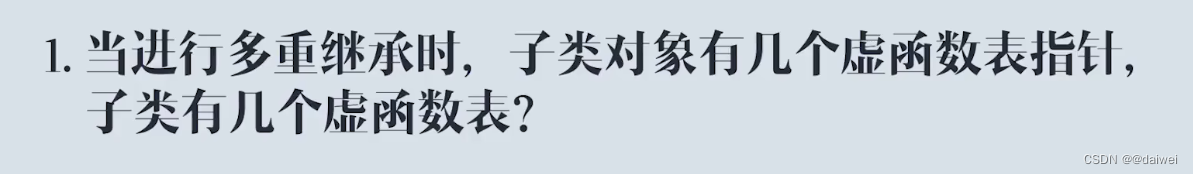

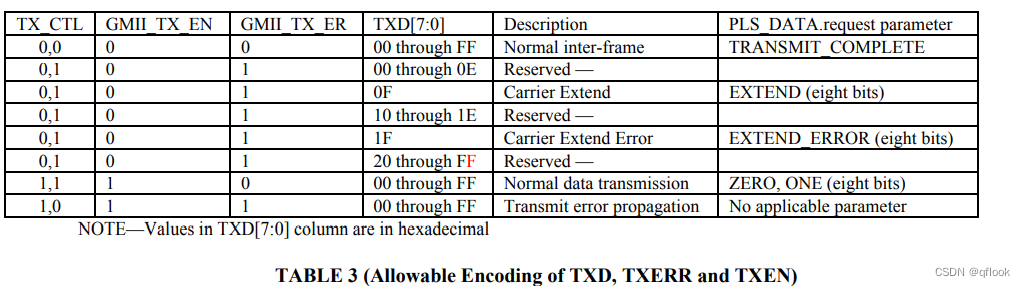

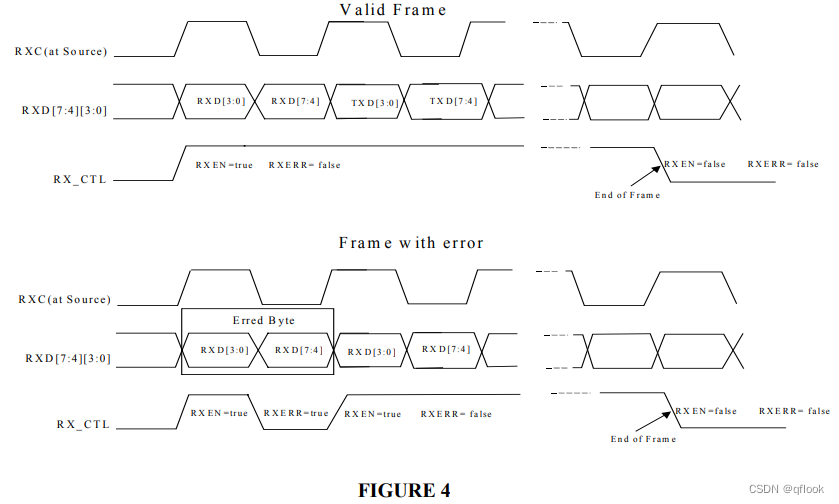

四、TX_CTL的编码

为了减少功率消耗,ERR信号将以在正常网络操作期间最小化转换的方式进行编码。ERR和EN信号异或后的值做为实际信号电平传输,然后在接收端通过已知的EN电平和异或后的电平解码出ERR信号。

当接收到一个无错的有效帧,EN=True(在时钟上升沿产生一个高电平),ERR=False(在时钟下降沿产生一个高电平,EN和ERR值不同,异或后为1);当没有帧被接收,EN=False(在时钟上升沿产生一个低电平),ERR=False(在时钟下降沿产生一个低电平,EN和ERR值想同,异或后为0),这也就是正常的帧间时间。

当接收到一个带错误bit的帧时,EN=True(在时钟上升沿产生一个高电平),ERR=True(在时钟下降沿产生一个低电平,EN和ERR值相同,异或后为0);

各种情况的组合如下表,其中正常遇到一般是第一行和最后2行,分别代表帧间时间,无错传输和有错传输:

对应的时序如下:

对应的时序如下:

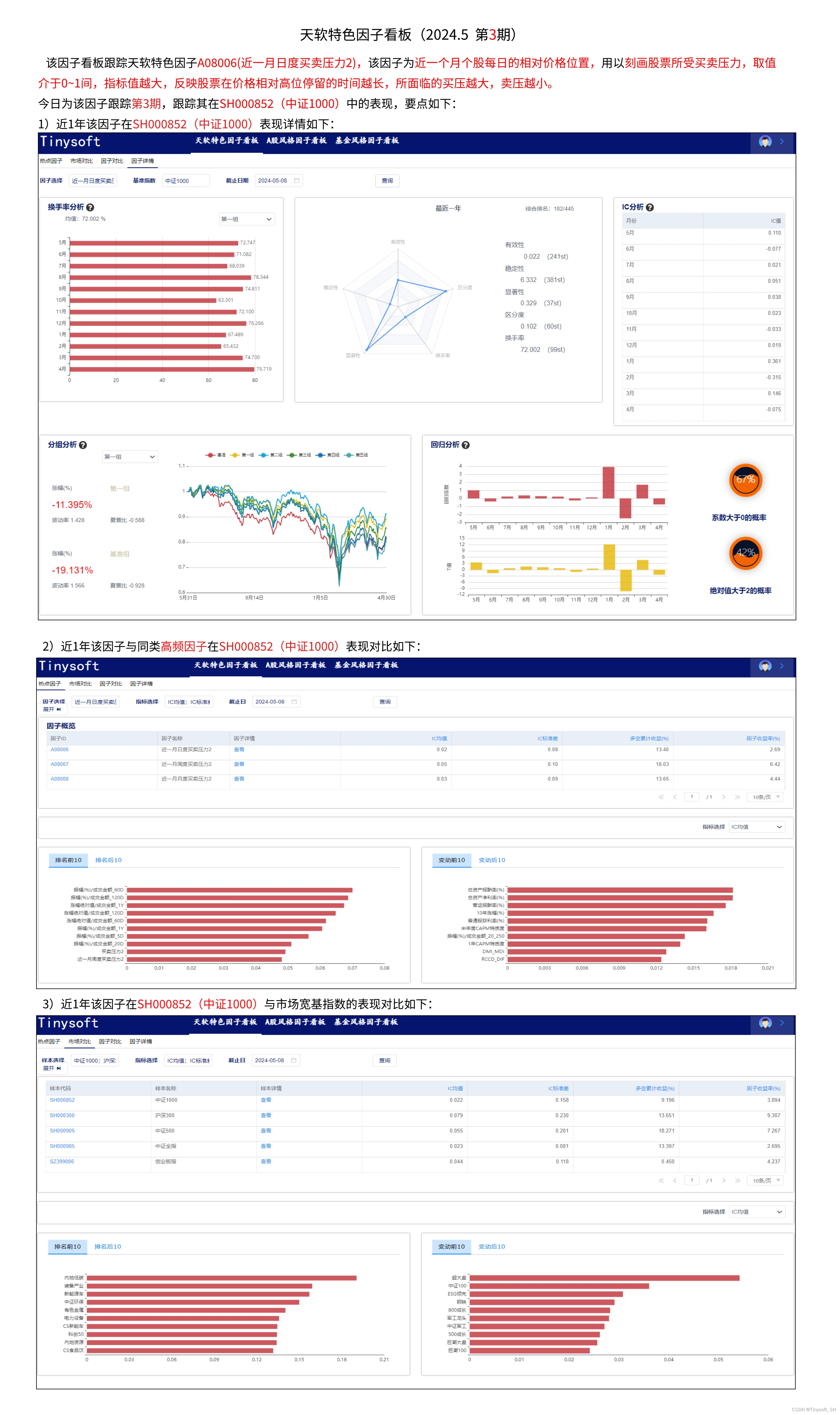

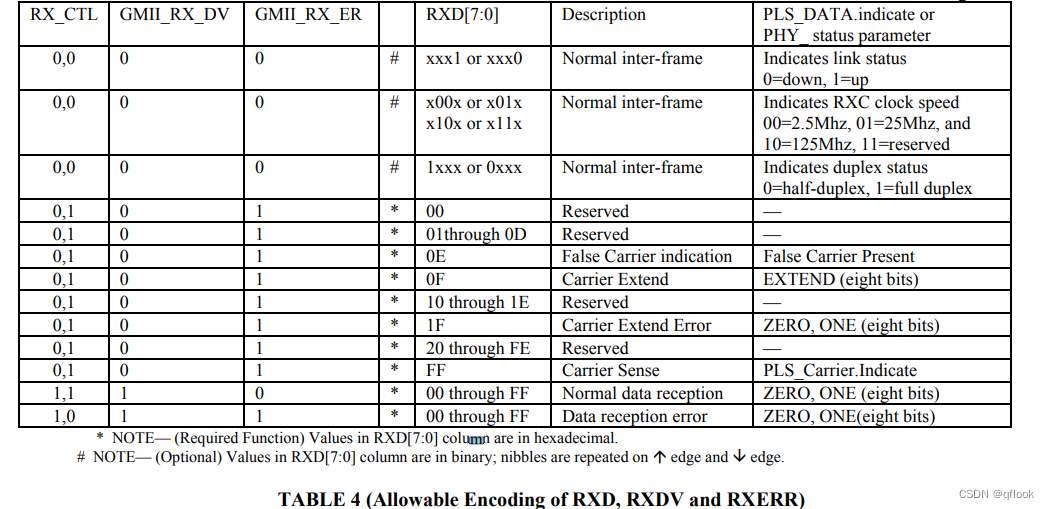

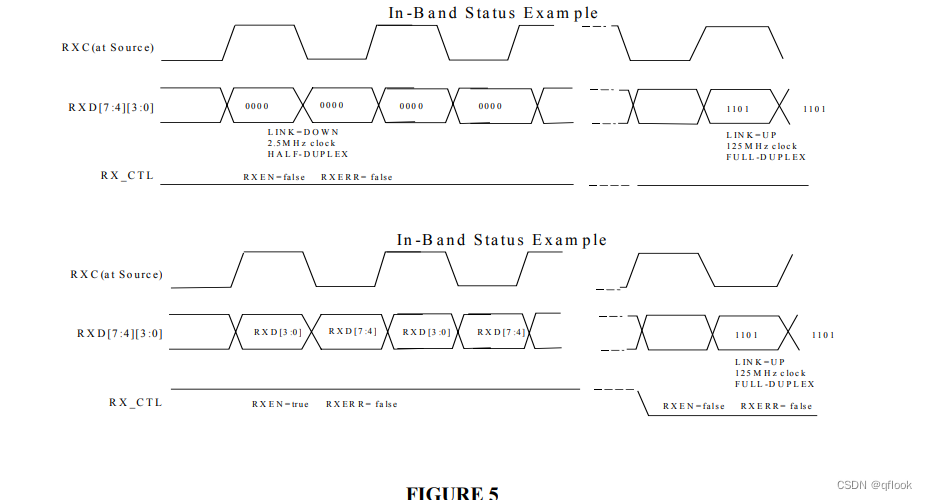

五、带内状态

五、带内状态

为了便于检测PHY的链路状态、速度和双工模式,帧间信号将被放置在RXD[3:0]信号上,如下表4所示。当不存在正常数据、数据错误、载波扩展、载波检测或假载波时,应指示PHY的状态。当链路状态关闭时,PHY的速度和双工由PHY的内部设置定义。根据个人工作经验,大部分都是寄存器内部设置。

时序波形如下:

六、其他说明

1.电气参数

根据协议描述让参考JEDEC EIA/JESD8-6(https://www.doc88.com/p-1436934939315.html),我查看了一下基本不太适用,大家还是参考具体芯片规格书即可。

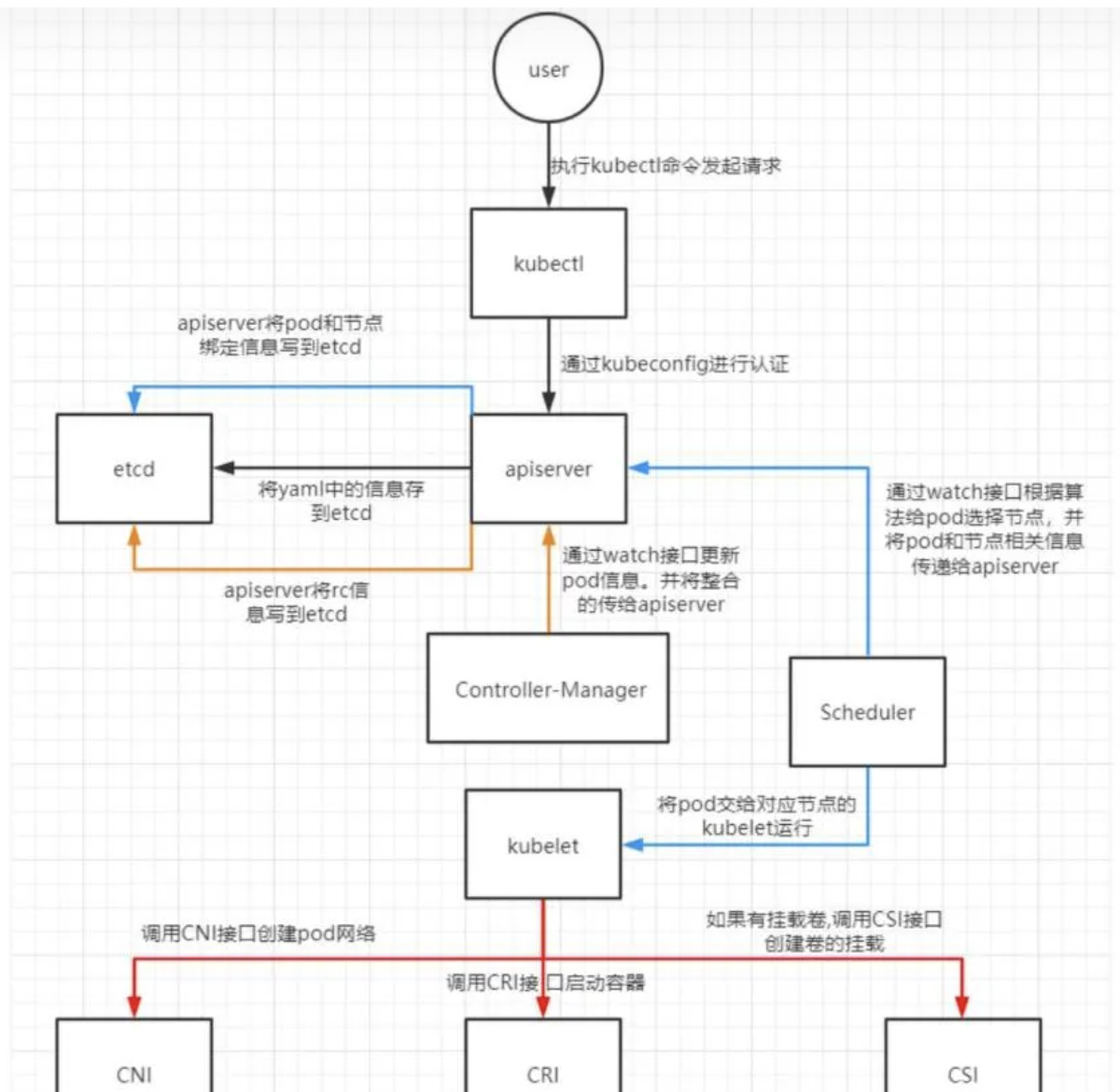

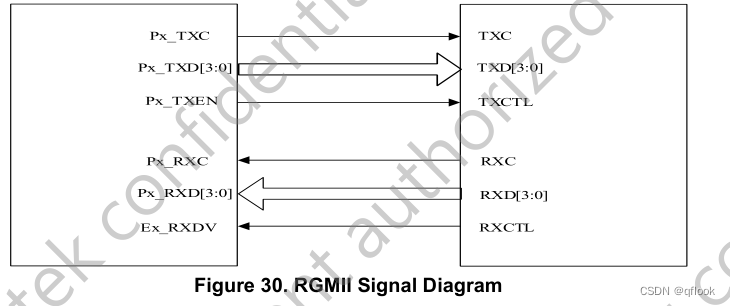

2.某芯片规格书

RGMII框图如下:

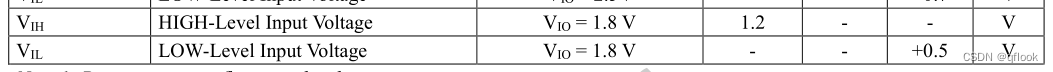

信号电平:

信号电平:

时序要求,基本和协议要求一致: