一、概述

对于复杂的片上系统,在进行RTL编码前,需进行深入的系统级仿真,以确认设计的体系结构是否恰当、总线是否能满足吞吐量和实现性要求以及存储器是否浪费,所进行的这些仿真要求在芯片的仿真模型上运行大量的软件,以覆盖所需的功能1。

SystemC的开发流程

sc源代码可以使用任何标准C++编译环境进行编译,生成可执行文件

运行可执行文件可以生成VCD格式的波形文件

使用综合工具(如Cynthesizer)可以将sc的RTL级描述综合为Verilog代码,也可以使用体系结构综合工具(如ESLFlex)总和为包括软件和硬件的片上系统。

建模精度

周期精确模型

仿真速度很慢,什么功能都可以模拟,但一般适合做硬件RTL验证。

非定时模型

仿真速度很快,但是包含信息较少,适合定义设计规范,也可以结合先进的综合工作用来做软件开发。

松散定时模型

既可以做软软件开发和软件性能评估,也可以做体系结构分析和硬件验证

系统级建模:C++和SystemC

SystemC首先是C++,任何C++的语法和库都可以用在SystemC中。

为什么使用SystemC而不是C++

原始的C++模型程序必须手工转换为Verilog/VHDL,而SystemC可以用于描述不同的抽象级别(系统级、寄存器传输级等)

二、语法

模块定义

SC_MODULE

SystemC库种定义的一个宏,用来定义一个新的C++结构体,类似硬件模块

SC_MODULE(sram8x256)

{

.....

}

SC_CTOR

构造函数,除了完成C++种所要求的基本功能外,构造函数还用于初始化进程的类型并创建进程的敏感表。

SC_CTOR(sram8x256)

{

......

}

端口和信号

SystemC专有数据类型

sc_int/sc_uint/sc_bigint/sc_biguint/

sc_bit:2值单bit数据类型

sc_logic:4值单bit数据类型

用户自定义数据结构类型

typedef struct _frame{

......

} frane;

抽象端口

class direct_if

:public virtual sc_interface

{

.....

}

sc_in/sc_out/sc_inout/sc_signal

端口类型,端口使用的数据类型可以时C++的数据类型,也可以是SystemC专用数据类型。

sc_in_clk clk; //端口定义,特殊情况,时钟定义

sc_in<sc_uint<8>> wr_data; //端口定义

sc_signal<sc_logic> addr[16]; // 信号定义

信号赋值

通过read()和write()函数对信号读取和赋值

addr_o.write(addr_i.read()); //将addr_i的值赋给addr_o的值

敏感表

sensitive

sensitive为SC_METHOD和SC_THREAD进程设置敏感表

SC_METHOD(main);

sensitive<<clk_i.pos()<<rst_i.pos();

进程调用

SystemC中进程是一个基本执行单位,被调用来仿真目标系统的行为。

在SystemC中,进程不是层次化的,一个进程中不能包含或者直接调用其他进程,但进程可以调用非进程的函数和方法。

SC_METHOD

使用该进程调用方法,当敏感表有事件发生,该进程就会被调用。只有该类进程返回后仿真系统的事件才有可能前进,因此该类进程中不能使用wait()这样的语句。

SC_METHOD进程的敏感表在模块的构造函数内设定。

SC_THREAD

线程进程,该调用方式下线程能够被挂起和重新激活。线程进程使用wait()挂起,当敏感表中有时间发生,线程进程被重新激活运行到遇到新的wait()语句再重新挂起。当该进程一旦推出,将不能再次进入。

可以用来描述testbench的输入激励和输出捕获

SC_CTHREAD

钟控线程进程,继承于线程进程,只能再时钟的posedge或negaedge被触发或者激活,更接近于实际硬件的行为。

时序控制

wait()

用于SC_THREAD和SC_CTHREAD。用于将进程挂起等待下一个事件发生重新激活被挂起的进程。

wait(); //等待敏感表中有事件发生

wait(const sc_event& ); // 等待事件发生

wait(100, SC_NS); // 进程将被挂起100ns后激活

wait(100, SC_NS, e1); // 如果100ns内有事件e1发生,或者时间超过了100ns,进程将被激活

三、常用用法

仿真流程

顶层函数sc_main()

sc_main将设计中所有模块连接在一起,并引入时钟和波形跟踪。

int sc_main(int argc, char * argv[])

{

......

}

sc_start()

控制所有时钟的产生并在适当的时刻激活SystemC调度器。调度器控制整个仿真过程中的调度工作,包括激活进程,产生延迟、计算和更新变量和信号的值。

sc_start()只在sc_main()中调用。

sc_start(); // 没有参数,表示仿真一直进行直到遇到sc_stop()函数。

sc_start(1000); // 仿真持续1000个时间单位停止或者期间遇到sc_stop()停止

波形跟踪

SystemC可以将仿真结果保存为VCD格式

- 只有在整个仿真期间都存在的信号和变量才能被追踪,及模块中的信号和数据成员能被跟踪,函数的本地变量只有在被调用是才存在,所以不能跟踪

- 任何类型的信号和变量都可以被跟踪

int sc_main(int, char **)

{

sc_in<int> datain;

sc_trace_file * my_trace_file;

my_trace_file = sc_create_vcd_trace_file("Wave"); // 产生一个Wave.vcd文件

......

sc_trace(my_trace_file, datain, "DataIn"); // 跟踪信号datain,datain在波形文件中被保存为DataIn

......

sc_close_vcd_trace_file(my_trace_file); // 关闭打开的波形文件

......

return 0;

}

信息打印

SystemC定义了几种打印等级,INFO和WARNING可直接打开,ERROR类型由SystemC仿真器抛出异常,用户定义的异常处理代码去处理,对于FATAL,则停止仿真。

SC_REPORT_INFO( msg_type, msg);

SC_REPORT_WARNING( msg_type, msg);

SC_REPORT_ERROR( msg_type, msg);

SC_REPORT_FATAL( msg_type, msg);

sc_asserrt( expr ); // 打印的等级严重程度为FATAL

set_actions

修改打印等级

时钟相位关系

sc_set_time_resolution()

sc_set_default_time_unit()

四、事务处理级建模(TLM)

事务指两个时间点内发生的不可分割的活动。可以是一次总线读或写事务

基本通道

基本通道不包含任何进程,也不对外展现任何可见结构,也不能调用其他基本通道。

sc_mutex

互斥通道

sc_mutex protect;

......

protect.lock();

......

protect.unlock();

sc_fifo < T >

已实现好的FIFO通道,T指存储的数据类型。

sc_fifo<packet> fifo2(4);

sc_semaphore

信号量,限制同时使用某共享资源的进程的数量。

分层通道

相比基本通道,分层通道包含进程,可以直接操作其他通道。

五、TLM2.0

TLM2.0是专门为建模存储器映射的片上总线而设计的SystemC模型库

事务对象是一个C++类,TLM2.0预定义了一个通用净核类和相应的基础协议,以进一步保障不同提供商提供的模型互联互通。

核心接口

事务发起者和目标模块必须遵守的接口标准,包含四种:阻塞、非阻塞传送接口、DMI和调试传送接口

阻塞传送接口

支持松散时间模型。发起者通过调用一个函数就可以完成一个非阻塞事务处理。

class ...

{

public:

virtual void b_transport(TRANS& trans, sc_core::sc_time& t)=0

}

b_transport(TRANS& trans, sc_core::sc_time& t)是欸阻塞事务处理接口的方法。trans是事务,t是双向时间参数。当发起者通过b_transport访问目标时,t为事务处理发起的时间;当目标返回时,t为事务处理结束时间。

非阻塞传送接口

非阻塞传送接口用于支持建模近似时间模型,该模型用于描述发起者和目标之间的事务处理过程的多相位的细节,每个相位都有一个明确的定时点。非阻塞接口有

tlm_phase是非阻塞传送接口模板类的缺省相位类型。tlm_phase的值有5个:UNINITIALIZED_PHASE=0, BEGIN_REQ=1, EDN_REQ, BEGIN_RESP, END_RESP。

事务定义

可以使用C++类来表示事务

class bus_payload // 定义

{

public:

unsigned int address;

......

};

bus_payload bp; // 例化

开源项目

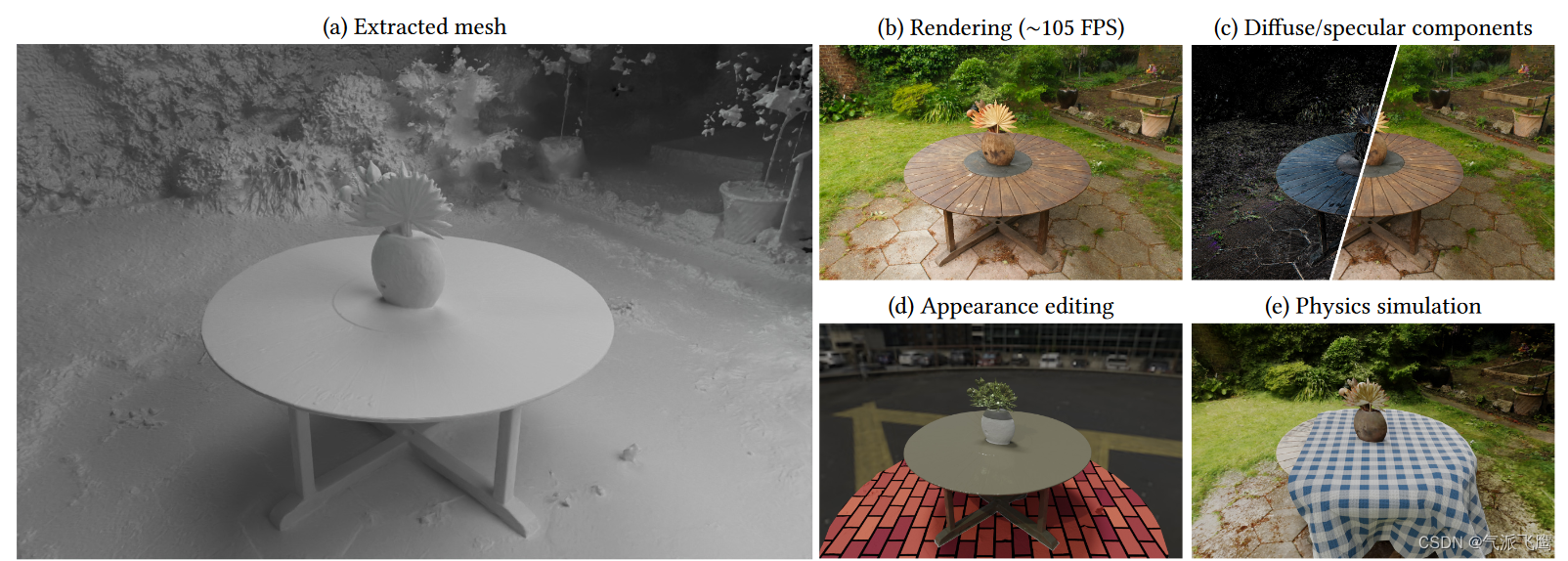

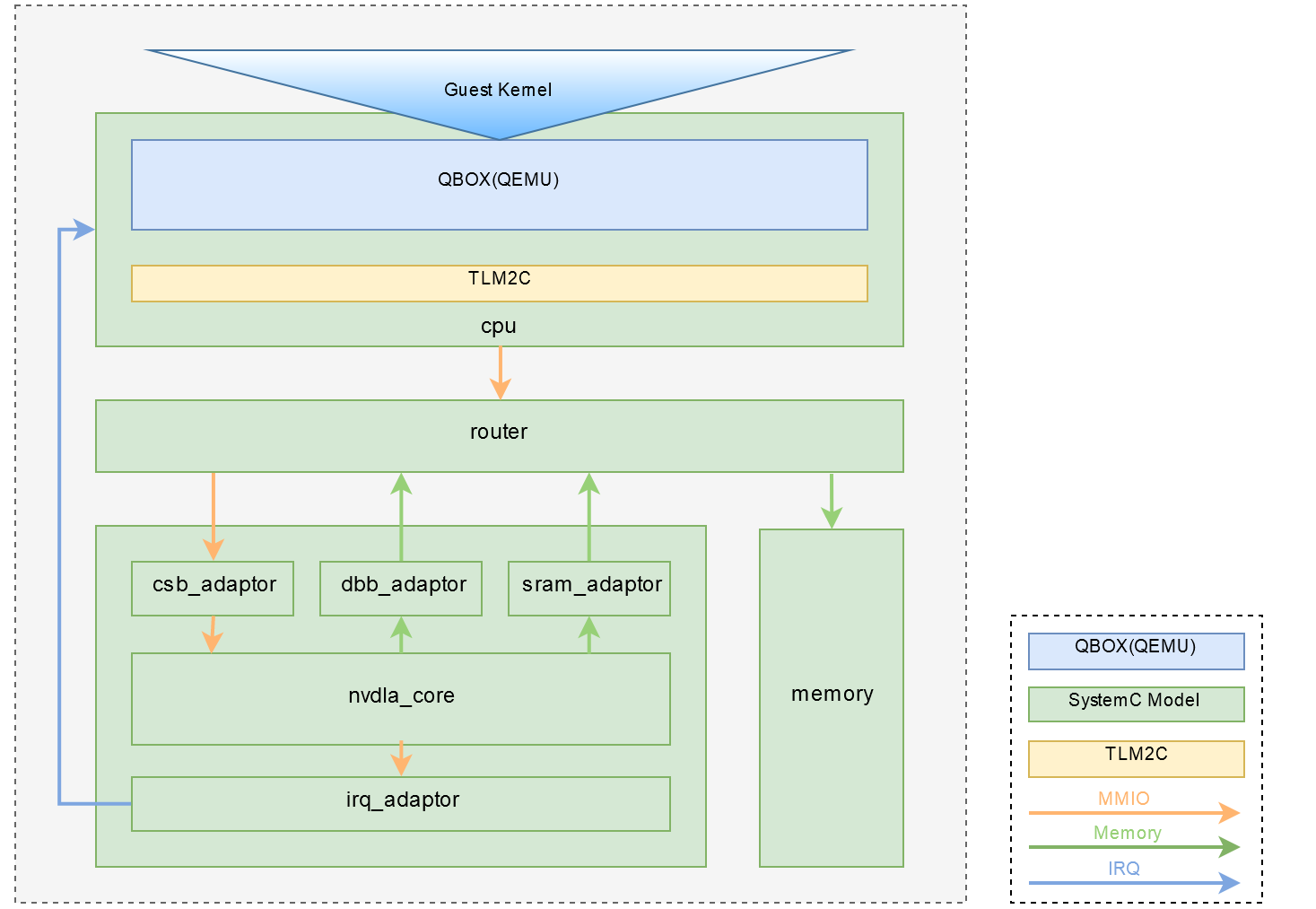

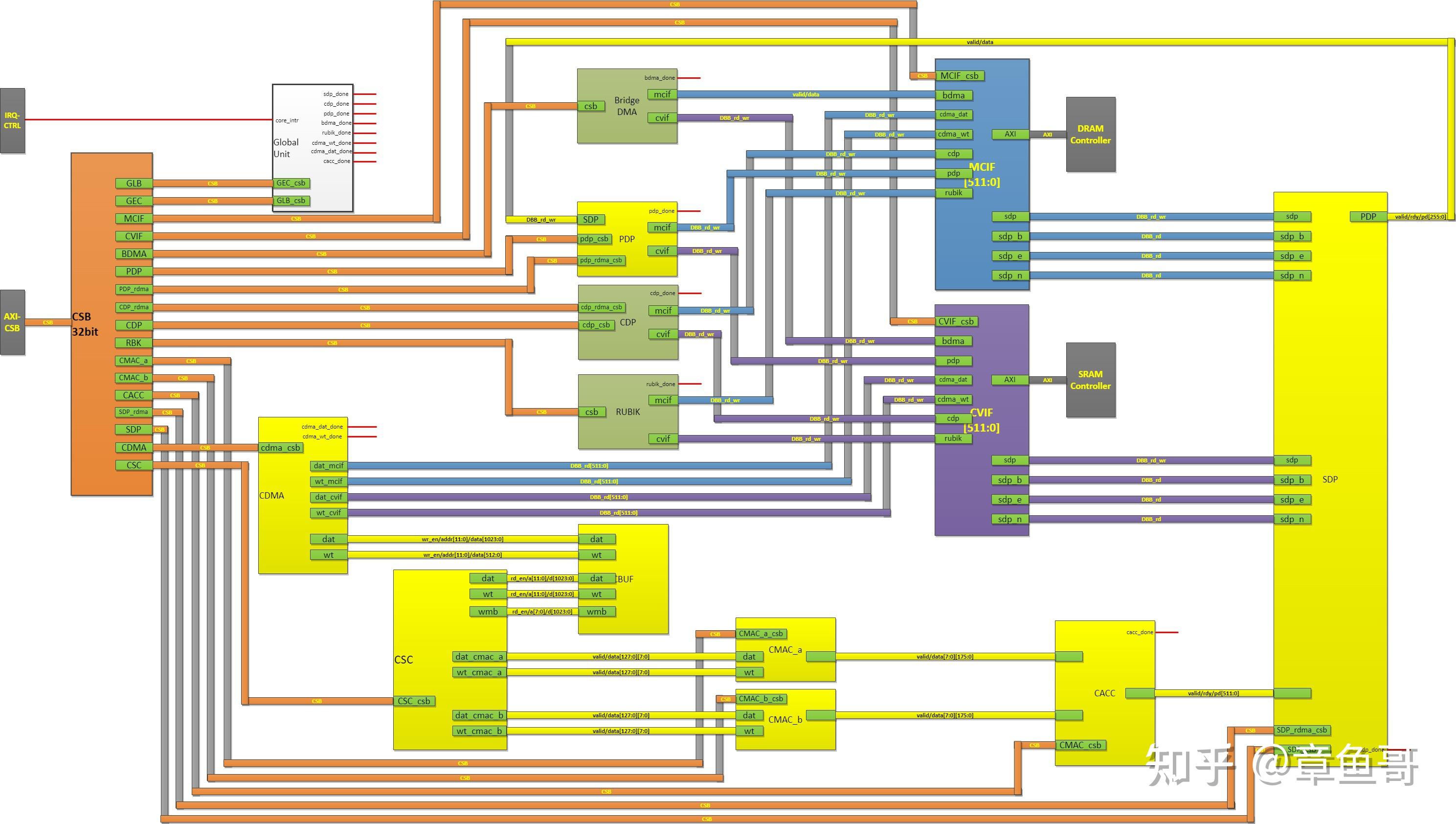

NVDLA

虚拟仿真平台

NVDLA 加速器硬件架构

NVDLA Quick Start

参考文献

李挥,陈曦, SystemC电子系统级设计 ↩︎

![Python 机器学习 基础 之 监督学习 [线性模型] 算法 的简单说明](https://img-blog.csdnimg.cn/direct/824311c328f94832b5bfc93660d0c294.png)