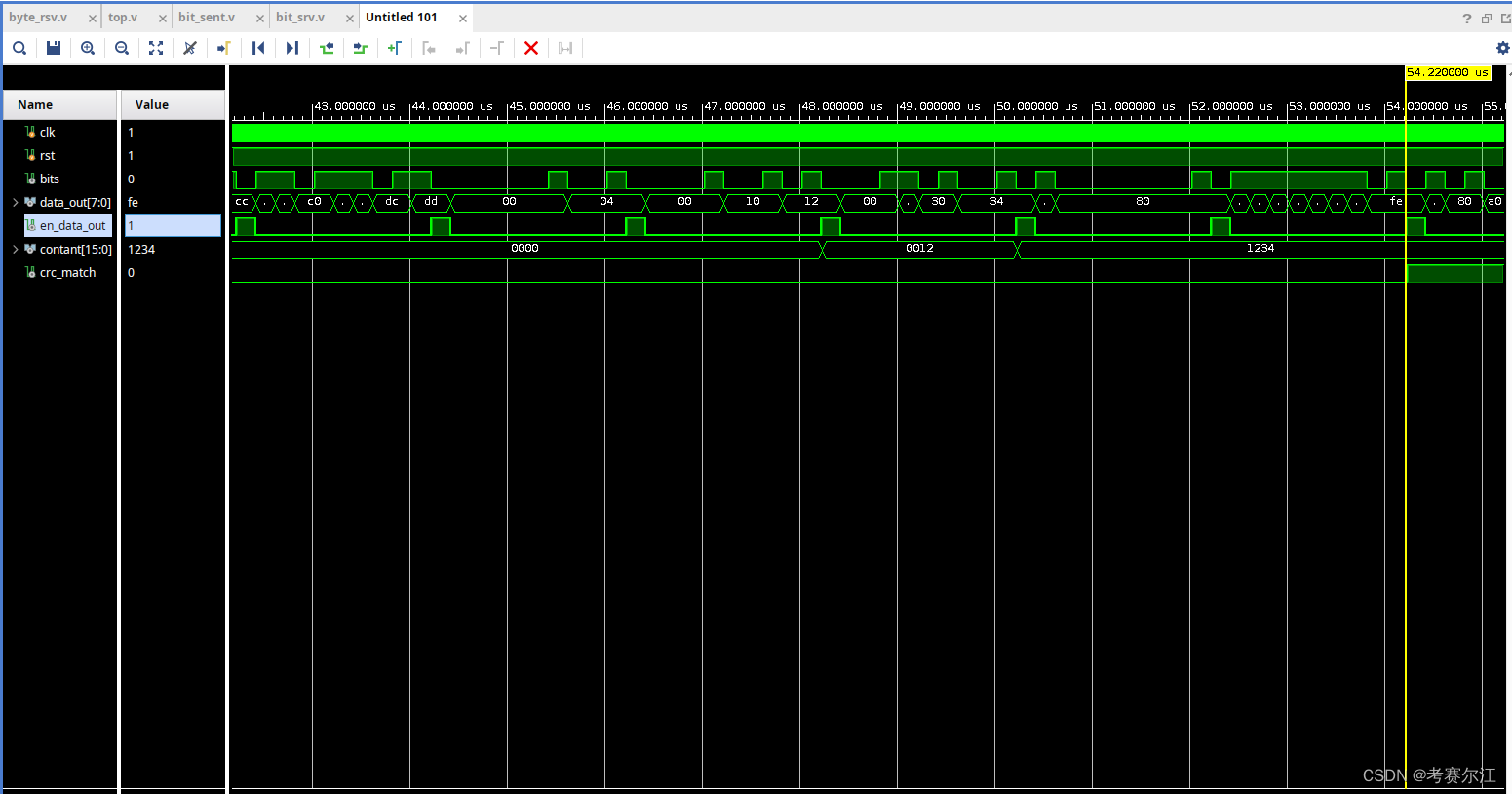

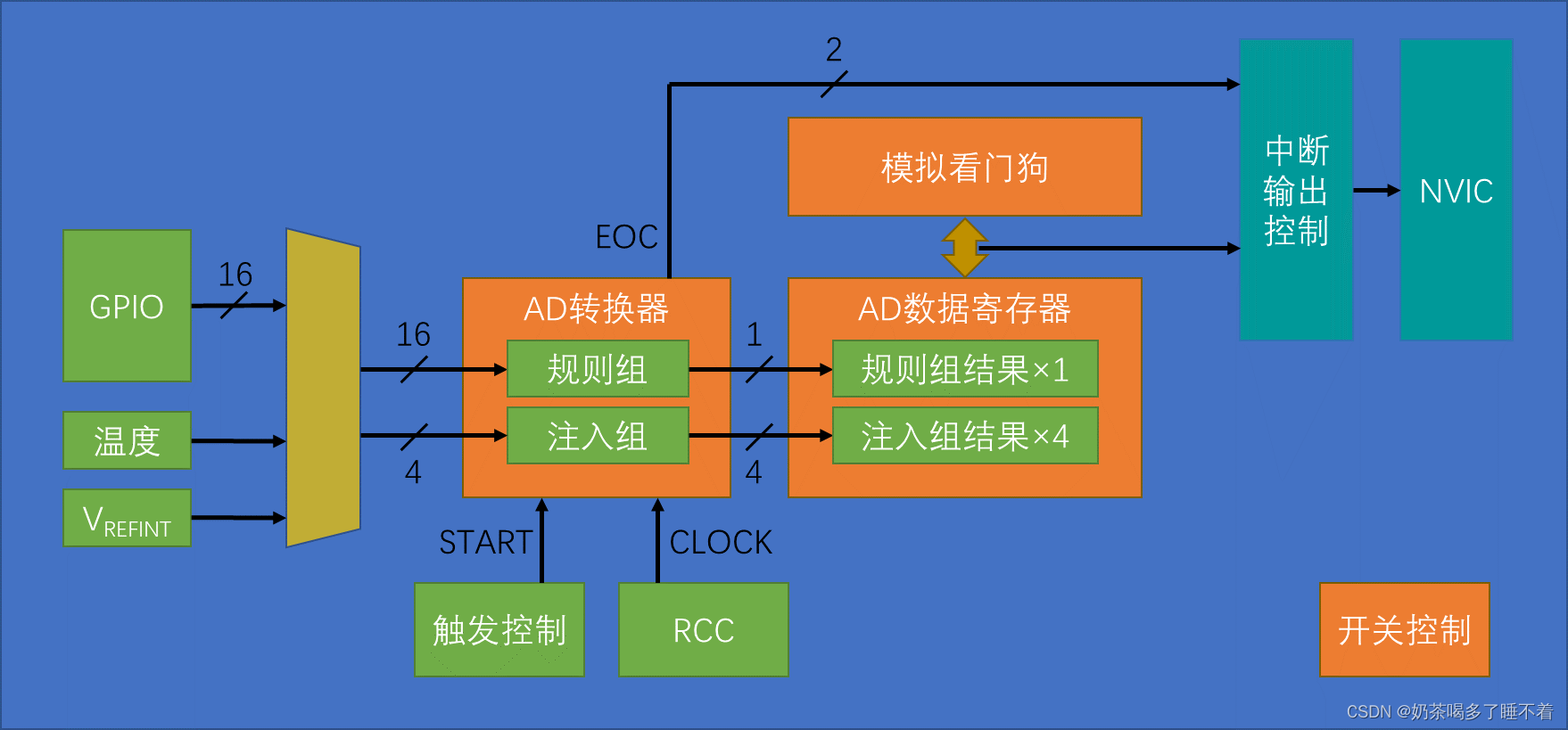

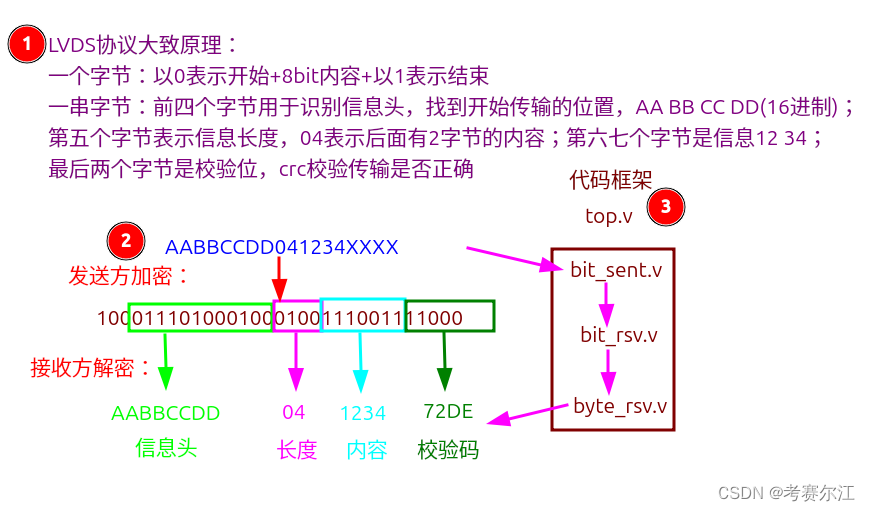

一幅图胜过千言万语

直接开始挫代码,先写top.v。

module top();

reg clk; // 生成时钟的寄存器

reg rst; // 生成复位信号的寄存器

initial clk = 1; // 初始值取1

always #1 clk = ~clk; //1ns取反一次

initial begin // 复位信号,先0,过段时间赋1

rst = 0;

# 20;

rst = 1;

$stop;

end

endmodule

再加其他三个子项的接口:

| 输入 | 输出 | |

| bit_sent | 时钟,复位 | 比特流 |

| bit_rsv | 时钟,复位,比特流 | 字节,字节输出信号 |

| byte_rsv | 时钟,复位,字节,字节输出信号 | 内容,校验结果 |

//top.v

module top();

reg clk;

reg rst;

initial clk = 1;

always #1 clk = ~clk;

initial begin

rst = 0;

# 20;

rst = 1;

$stop;

end

// wire表示线,其他文件的输出用线接,自己的内容用寄存器输出或者保存

wire bits;

bit_sent bit_sent(

.clk (clk),

.reset (rst),

.bits(bits) //这里不能有逗号

); //这里不能忘记冒号

wire [7:0] data_out; // [7:0] 表示高位7到底为0,共8比特

wire en_data_out;

bit_rsv bit_rsv

(

.clk (clk),

.reset (rst),

.uart_tx (bits), // .uart_tx是bit_rsv文件形参名称

//括号内的bits是bit_sent的输出bits接到uart_tx上

.data_out (data_out),

.en_data_out (en_data_out)

);

wire [15:0] contant;

wire crc_match;

byte_rsv byte_rsv

(

.clk (clk),

.reset (rst),

.byte_in(data_out),

.en_byte(en_data_out),

.contant(contant),

.crc_match (crc_match)

);

endmodule 采用的校验法: