视频链接

CPLD电路设计(安路为例)01_哔哩哔哩_bilibili

CPLD电路设计(以安路为例)

浅谈板级电源设计的三种方法_哔哩哔哩_bilibili 参考【浅谈板级电源设计的三种方法】

FPGA板级硬件实战S1~7课

实战Power2-电源入口:ATX电源

1、安路科技

安路科技的ELF2系列FPGA有多个器件,定位低成本、低功耗可编程市场。ELF2器件旨在用于大批量,成本敏感的应用,使系统设计师在降低成本的同时又能够满足不断增长的带宽要求。

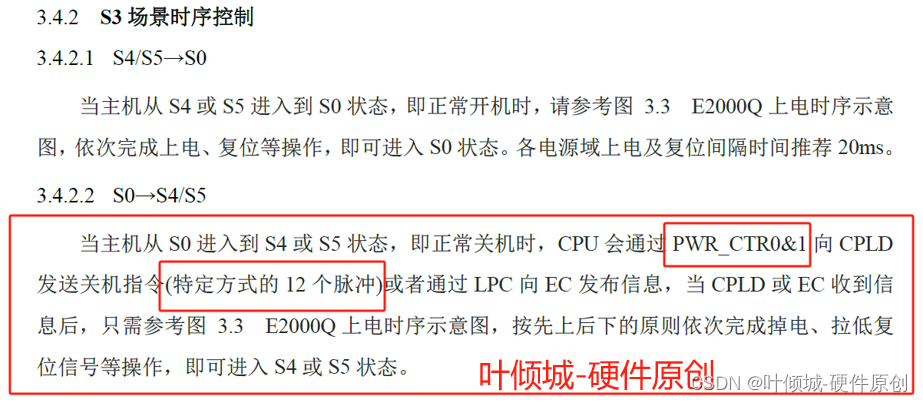

2、CPLD的应用案例

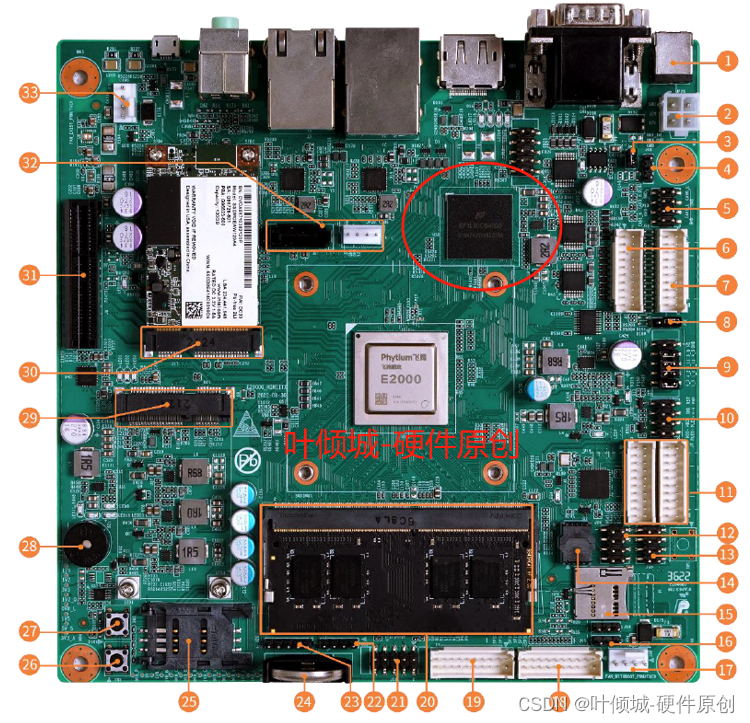

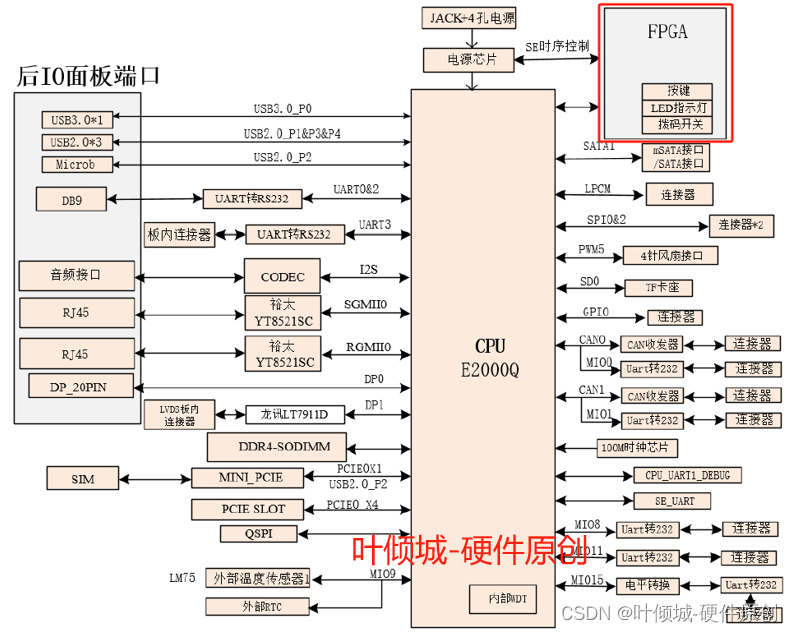

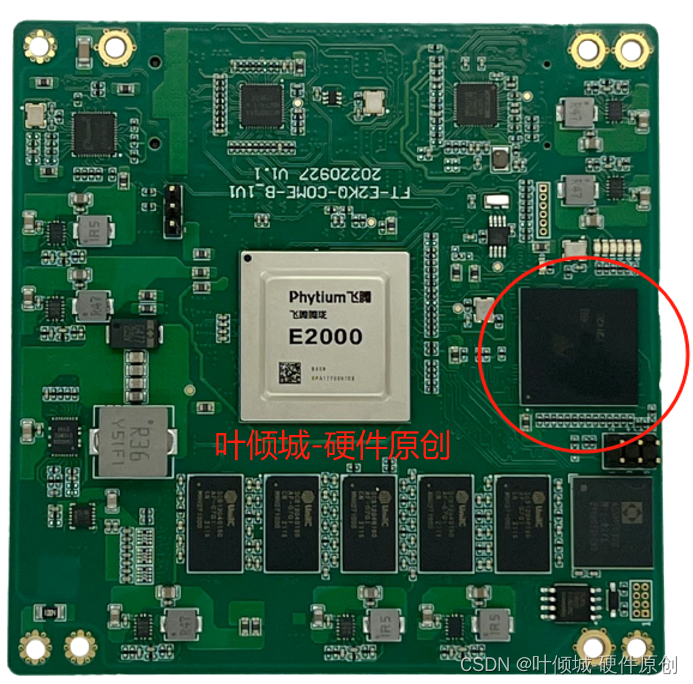

2.1、《E2000Q_Mini-ITX_用户手册》

2.2、《国产化飞腾开发套件_E2000-Q-EVB用户手册》

2.3、《E2000Q_教育开发板使用说明》

编号22: CPLD烧录口

CPLD的作用:

1、接电源的EN和PG信号

2、接各功能模块的复位信号

3、接PCIE或者USB等唤醒信号

4、接中断信号给CPU

5、接控制风扇的信号

6、接控制灯指示信号

7、其他等

8、接ACPI相关的信号

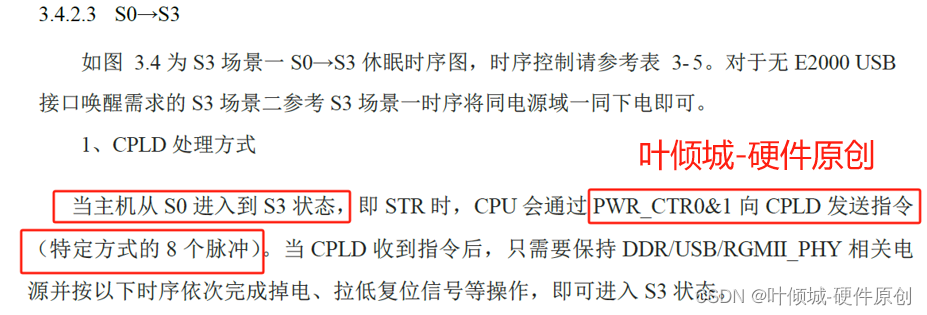

3、安路科技 EF2系列

EF2系列FPGA产品是安路科技推出的“小精灵”系列第二代产品,包含内嵌MCU的SOC FPGA产品。采用55nm低功耗工艺,具有多功能配置、高性能、内部资源丰富等特点。

在视频采集、工业控制、通信等领域具有广泛的适应性。

4、EF2系列:以EF2L45BG256B为例

4.1、信号管脚

| 引脚名称 | 方向 | 描述 |

| 时钟引脚 | ||

| GPLLx_CLKIN/ GPLLx_CLKIP | I/O | PLL参考时钟专用输入引脚 |

| GPLLx_OUTN/GPLLx_OUTP | I/O | PLL输出时钟专用引脚 |

| GCLKIOT/GCLKIOR | 输入 | 除EF2L25芯片只有一组GCLKIO信号外,EF2系列其他器件均预留了四组信号连接PLL参考时钟输入 |

| 普通I/O | ||

| NC | - | 无连接 |

| GND | - | 电源地 |

| VCCIOx | - | I/O组电源 |

| VCCAUX | - | 辅助电源 |

| GND_PLLx | - | PLL地 |

| JTAG专用引脚 | ||

| TCK | 输入 | TCK输入边界扫描时钟 |

| TDI | 输入 | 边界扫描数据输入 |

| TDO | 输出 | 边界扫描数据输出 |

| TMS | 输入 | 边界扫描模式选择 |

| JTAGEN | 输入 | JTAG使能 |

| 配置专用管脚 | ||

| CSN | 输入 | 并行下载模式片选信号,低有效 |

| PROGRAMN | 输入 | 全局复位输入,低有效 |

| SCLK | I/O | 配置时钟专用引脚 |

| DONE | I/O | 专用配置状态引脚,在配置完成后会输出高,源端开路 |

| INITN | I/O | 专用配置状态引脚,输出高表示FPGA准备好配置,源端开路 |

| ADC功能管脚 | ||

| ADC_CHx | 输入 | ADC模拟信号输入 |

| ADC_VREF | 输入 | ADC参考电压 |

| ADC_VDDA | 输入 | ADC模拟电源 |

| ADC_VDDD | 输入 | ADC数字电源 |

4.2、电源管脚

4.3、配置说明

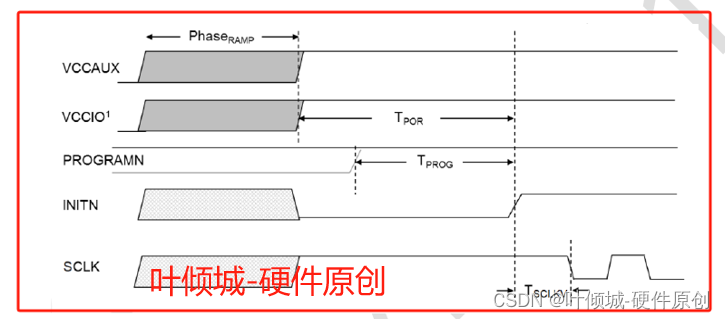

4.4、配置流程

ELF2 FPGA芯片的整个配置过程可以分三个部分。首先,在芯片上电复位或者系统复位信号有效后进入复位,等待内部信号和电源稳定后,系统进入初始化阶段,装载Feature寄存器值,内部配置信息清除,初始化完成后,FPGA开始接受配置数据写入,写入完成后,FPGA芯片启动阶段。

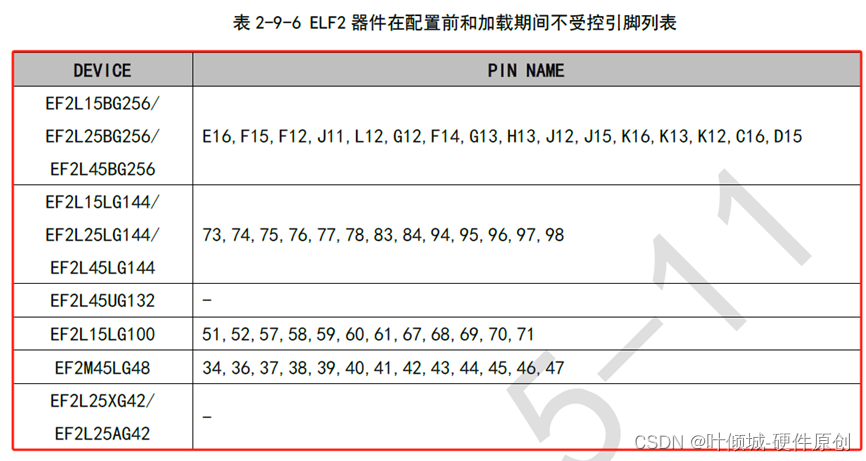

4.5、FPGA I/O 引脚在配置阶段的状态

4.5.1、非配置相关IO

4.5.2、配置相关引脚跟配置设置相关

4.6、热插拔规格

4.7、IO配置

4.7.1、时钟输入

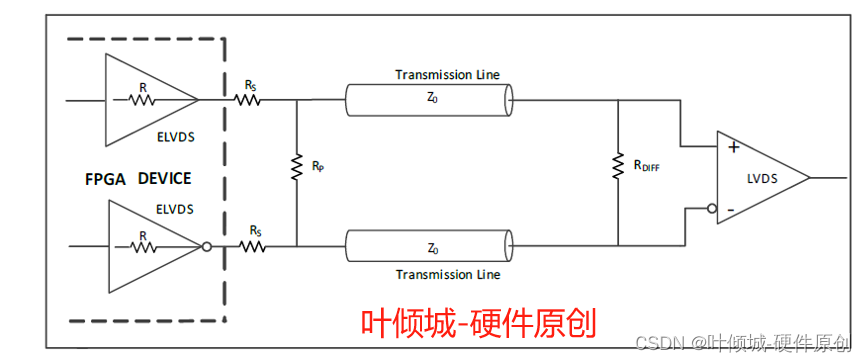

4.7.2、LVDS

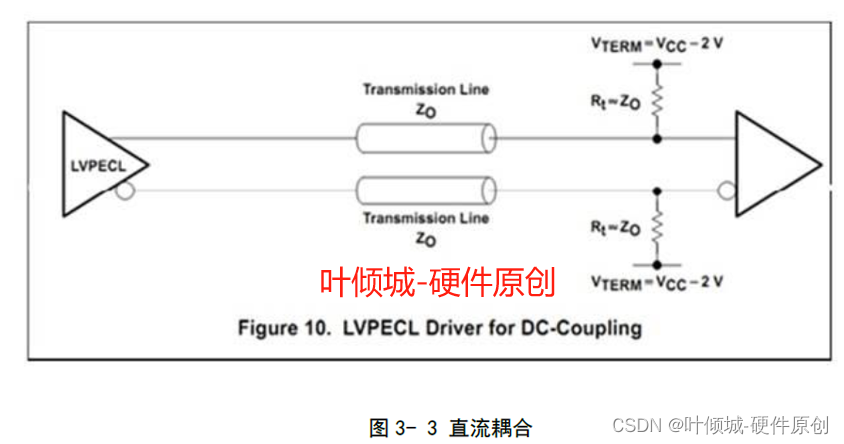

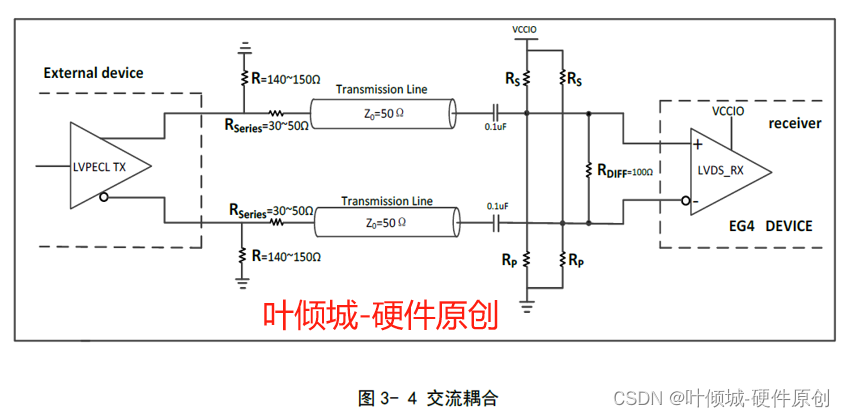

4.7.3、LVPECL

4.8、上下电时序