名称:基于FPGA的累加器及数码管显示VHDL代码Quartus仿真(文末获取)

软件:Quartus

语言:VHDL

代码功能:

累加器及数码管显示

1、可以通过按键输入1~9

2、数字输入后进行累加,将累加结果显示在数码管

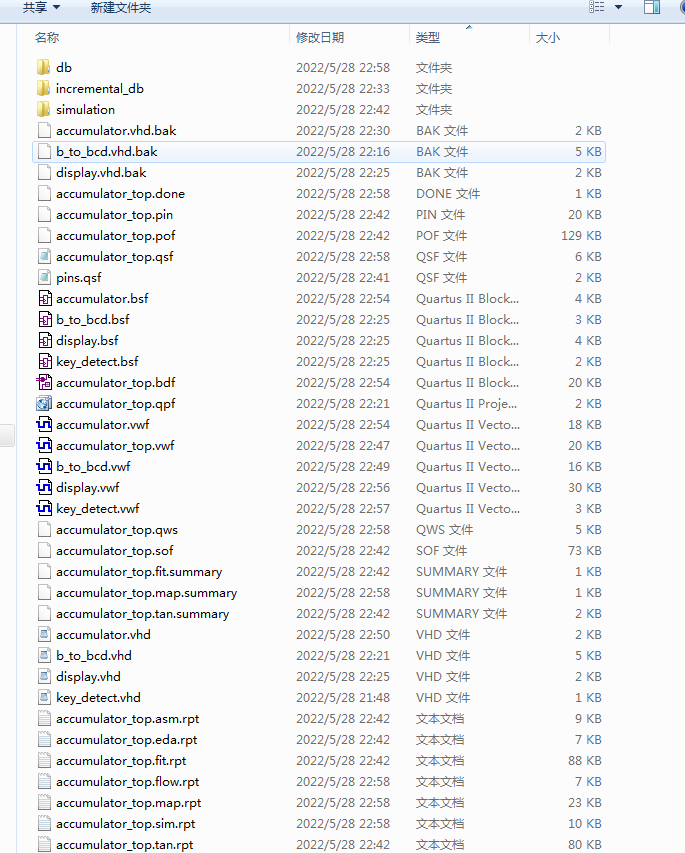

1. 工程文件

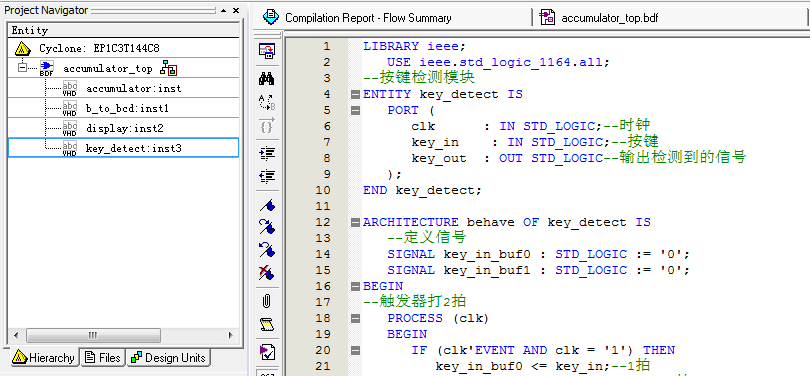

2. 程序文件

3. 程序编译

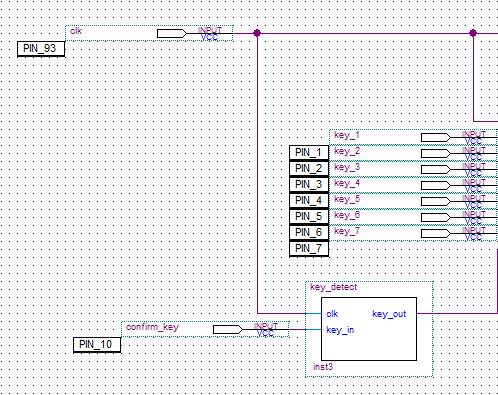

4. 管脚分配

时钟接1000Hz左右

5. RTL图

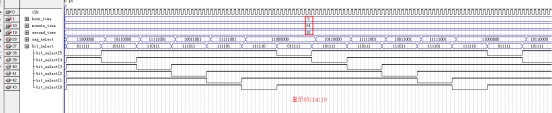

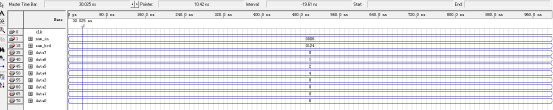

6. 仿真图

整体仿真图

按键模块

累加模块

BCD转换模块

显示模块

![]()

设计文档.doc

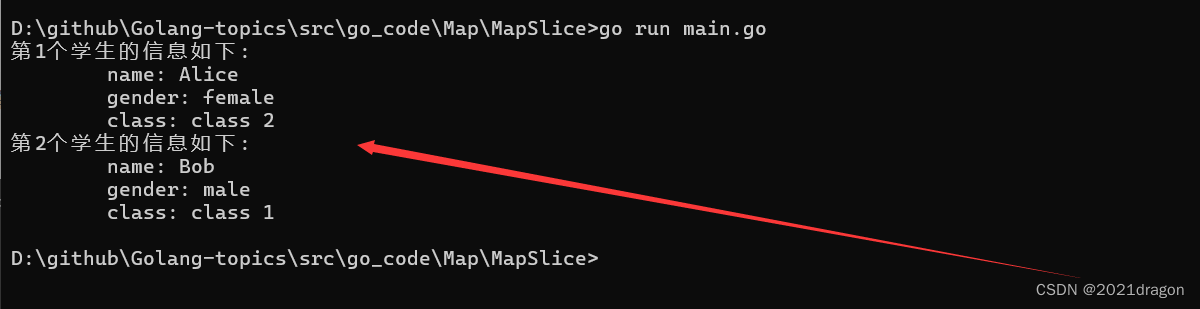

部分代码展示:

LIBRARY ieee; USE ieee.std_logic_1164.all; USE ieee.std_logic_unsigned.all; --累加显示模块 ENTITY accumulator IS PORT ( clk : IN STD_LOGIC;--时钟 key_1 : IN STD_LOGIC;--按键1 key_2 : IN STD_LOGIC;--按键2 key_3 : IN STD_LOGIC;--按键3 key_4 : IN STD_LOGIC;--按键4 key_5 : IN STD_LOGIC;--按键5 key_6 : IN STD_LOGIC;--按键6 key_7 : IN STD_LOGIC;--按键7 key_conf : IN STD_LOGIC;--确认按键 num_in : OUT STD_LOGIC_VECTOR(15 DOWNTO 0);--加数 sum : OUT STD_LOGIC_VECTOR(15 DOWNTO 0)--累加和 ); END accumulator; ARCHITECTURE behave OF accumulator IS --定义信号 SIGNAL data_in : STD_LOGIC_VECTOR(15 DOWNTO 0) := x"0000";--输入加数 SIGNAL data_sum : STD_LOGIC_VECTOR(15 DOWNTO 0) := x"0000";--累加和 BEGIN PROCESS (clk) BEGIN IF (clk'EVENT AND clk = '1') THEN if(key_1='1')then--按键1 data_in<=x"0001";--输入1 elsif(key_2='1')then--按键2 data_in<=x"0002";--输入2 elsif(key_3='1')then--按键3 data_in<=x"0003";--输入3 elsif(key_4='1')then--按键4 data_in<=x"0004";--输入4 elsif(key_5='1')then--按键5 data_in<=x"0005";--输入5 elsif(key_6='1')then--按键6 data_in<=x"0006";--输入6 elsif(key_7='1')then--按键7 data_in<=x"0007";--输入7 end if; END IF; END PROCESS; PROCESS (clk) BEGIN IF (clk'EVENT AND clk = '1') THEN if(key_conf='1')then--确认按键 data_sum<=data_sum+data_in;--累加 end if; END IF; END PROCESS; num_in<=data_in; sum<=data_sum; END behave;

源代码

扫描文章末尾的公众号二维码