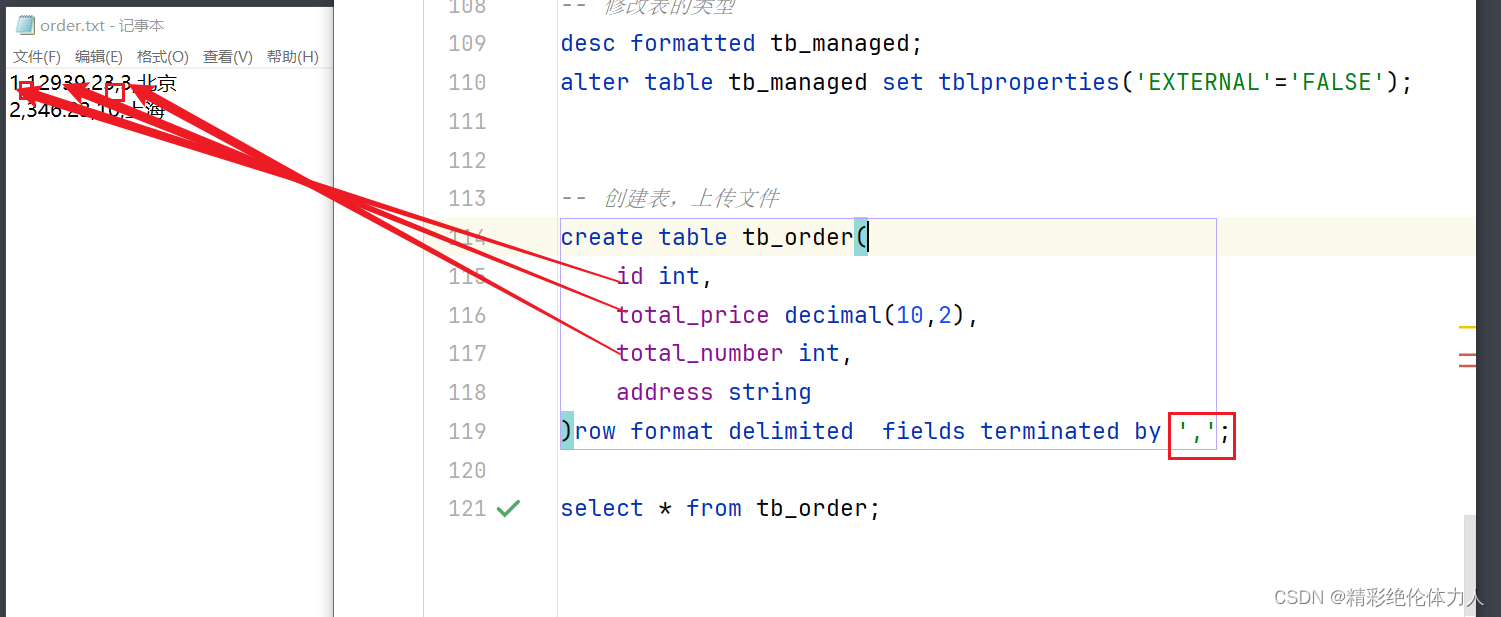

verilog分析task的接口设计,证明这种写法:assign {a,b,c,d} = links;

- 1,task在状态机中的使用好处:

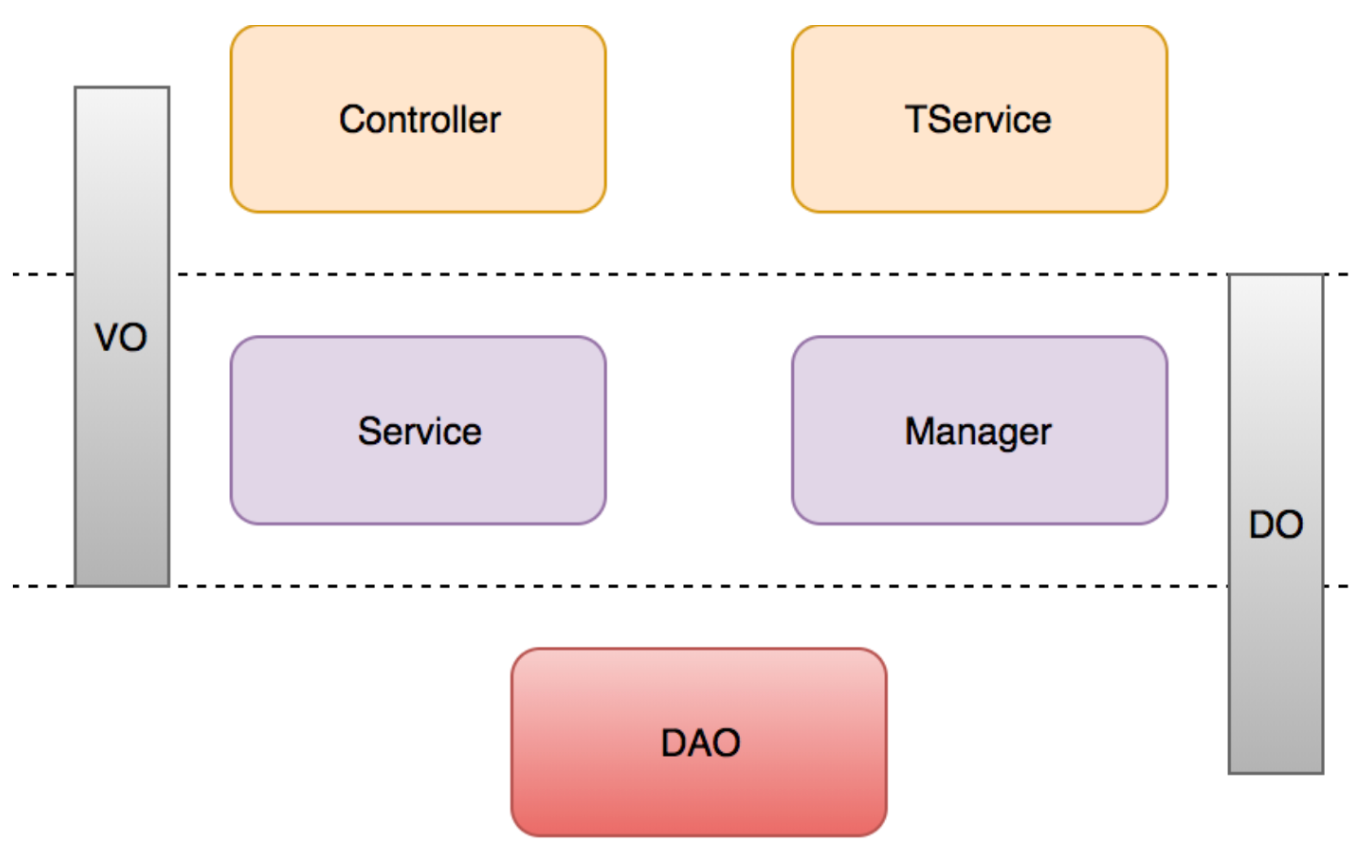

- 2,RTL设计

- 3,测试testbench

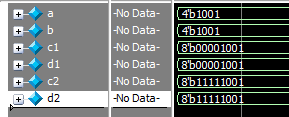

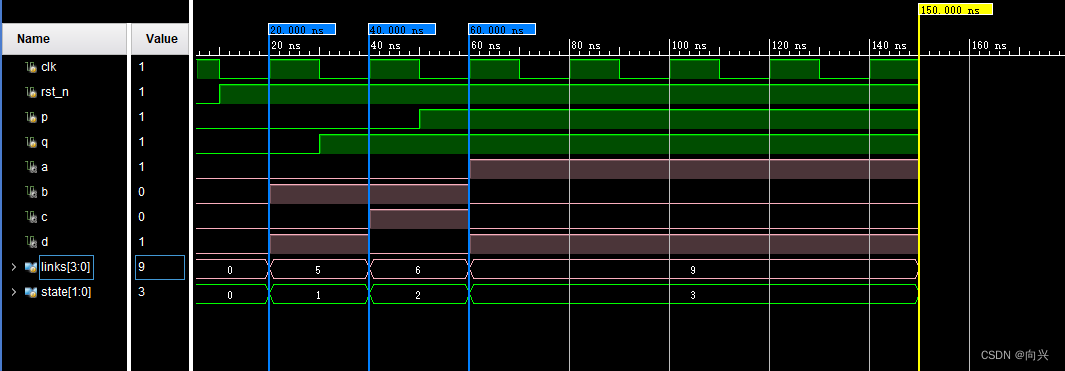

- 4,波形分析,正确!

参考文献:

1,练习七-在Verilog中使用任务task

1,task在状态机中的使用好处:

2,RTL设计

//

// 设计一个模块

module link_ports(

input clk,

input rst_n,

input p,

input q,

output a,

output b,

output c,

output d

//output out

);

reg [3:0] links;

reg [1:0] state;

// 判断是否 在rst_n后 的第一个clk,就实现输出结果:1111.

assign {a,b,c,d} = links; //证明这种写法是对的!

always@(posedge clk or negedge rst_n) begin

if(!rst_n) begin

state <= 2'b00;

links <= 4'b0000;

end

else // 来一个clk, 进行 1次任务.

add;

end

task add;

begin

casex(state)

2'b00:

if(p == 0 && q == 0) begin

links <= 4'b0101;

state <= 2'b01;

end

2'b01:

if(p == 0 && q == 1) begin

links <= 4'b0110;

state <= 2'b10;

end

2'b10: begin

links <= 4'b1001;

state <= 2'b11;

end

2'b11:

if(p ==1 && q == 0) begin

links <= 4'b1111;

state <= 2'b00;

end

default: begin // 回到原态

links <= 4'b0000;

state <= 2'b00;

end

endcase

end

endtask

endmodule

3,测试testbench

//

// 测试信号

module tb_link_port;

reg clk;

reg rst_n;

reg p, q;

wire a;

wire b;

wire c;

wire d;

// wire out;

always #10 clk = ~clk; // T = 20.

initial begin

rst_n = 0; clk = 1; p = 0; q = 0;

#10 rst_n = 1;

// repeat(8) begin

#20 p = 0; q = 1;

#20 p = 1; q = 0;

#100 $finish;

// end

end

link_ports u1_link_ports(

.clk (clk ),

.rst_n (rst_n ),

.p (p ),

.q (q ),

.a (a ),

.b (b ),

.c (c ),

.d (d )

);

endmodule

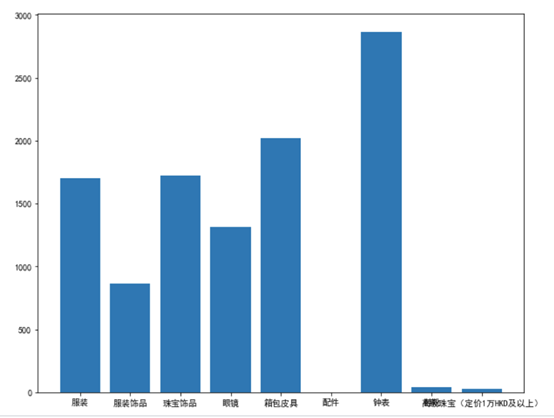

4,波形分析,正确!

![AD21技巧[更加便捷的DRC检查][把线框转成Keep-Out Layer板框]](https://img-blog.csdnimg.cn/direct/1b36524dd1054bb29bc78f48a7a7d219.png)

![[Android14] SystemUI的启动](https://img-blog.csdnimg.cn/direct/840460aceb7d488cb2ae8a93c2980a43.png)