本文参考PCIe协议 5.0:https://download.csdn.net/download/zz2633105/89204842

PCIe配置空间

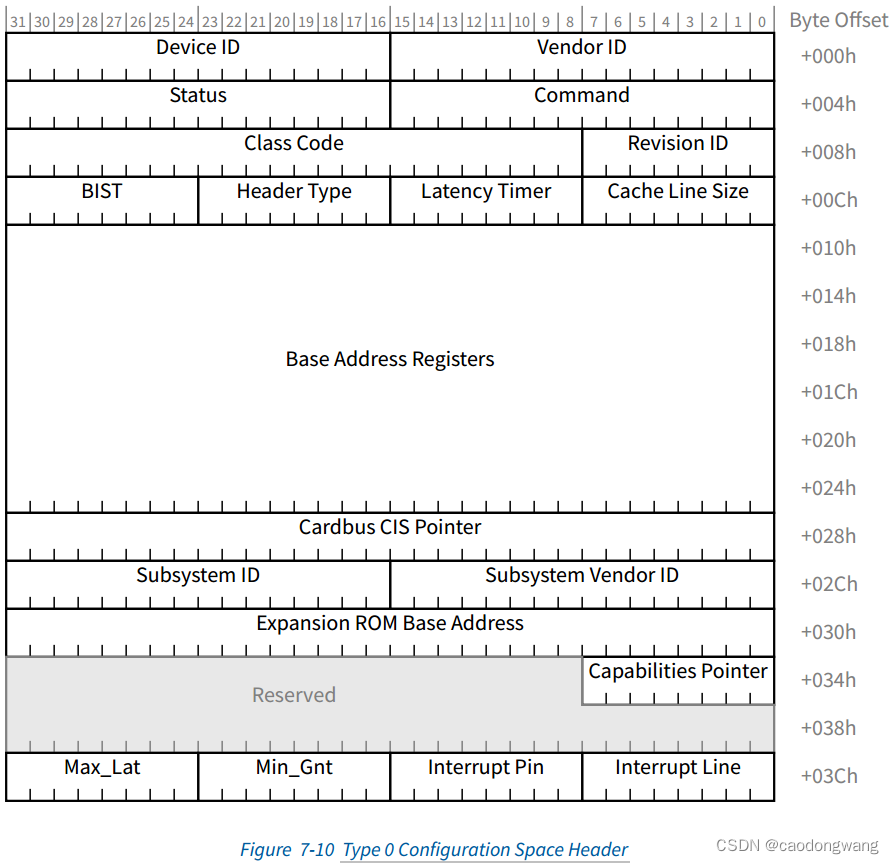

EP标准配置空间

Vendor ID Register (Offset 00h)

PCIe设备厂商ID,比如Intel的Vendor ID通常是0x8086。需要注意的是,厂商的ID不是厂商随意定的,而是由厂商花钱申请的,已申请PCIe厂商ID可以通过网址查询。

Device ID Register (Offset 02h)

PCIe设备ID,需要厂商自定义,通常用来区分不同种类的设备。在系统中,一般通过厂商ID(Vendor ID)和设备ID(Device ID)来加载驱动,较复杂的设备还可能借助子系统ID(Subsystem ID)和子系统厂商ID(Subsystme Vendor ID)。

Command Register (Offset 04h)

该寄存器为PCI设备的命令寄存器,在初始化时,其值为0,此时这个PCIe设备除了能够接受配置请求总线事务之外,不能接收任何存储器或I/O请求。系统软件需要合理设置该寄存器之后,才能访问该设备的存储器或者I/O空间。在linux系统中,设备驱动程序调用pci_enable_device函数,使能该寄存器的I/O和Memory Space位之后,才能访问该设备的存储器或者I/O地址空间。

| bit | 功能 |

|---|---|

| 0 | I/O Space Bit,该Bit表示PCIe设备是否响应I/O请求,为1时响应,为0时不响应。如果PCIe设备支持I/O地址空间,系统软件会将该Bit置1,复位值为0。 |

| 1 | Memory Space Bit,该Bit表示PCIe设备是否响应内存请求(Memory Read/Write),为1时响应,为0时不响应。如果PCIe设备支持内存空间,系统软件会将Bit置1,复位值为0。 |

| 2 | Bus Master Bit,对于EP,该Bit表示PCIe设备是否可以主动发起I/O和内存请求,为1时表示可以,为0时表示不可以,复位时为0。 对于Bridge,该Bit除了表示自身是否可以主动发起I/O和内存请求外,还可以控制Bridge是否转发下行端口的I/O和存储器请求到上行端口。若该Bit为0,则拒绝转发下行端口的I/O和内存请求,并对Non-Posted请求给予回复UR(Unsupported Requests),Posted请求丢弃。 |

| 3 | Special Cycle Enable,该BIt为PCI设备特有的。对于PCIe设备,该Bit无意义,必须硬连接到0 b。 |

| 4 | Memory Write and Invalidate,该BIt为PCI设备特有的。对于PCIe设备,该Bit无意义,必须硬连接到0 b。 |

| 5 | VGA Palette Snoop,该BIt为PCI设备特有的。对于PCIe设备,该Bit无意义,必须硬连接到0 b。 |

| 6 | Parity Error Response,复位值为0,当PCIe报文传输过程中出现奇偶校验错误时,该Bit为0,则只会将Status寄存器的Detected Parity Error bit置1,该Bit为1,则即将Status寄存器的Detected Parity Error bit置1,又将Status寄存器的Master Data Parity Error bit置1。 |

| 7 | IDSEL Stepping/Wait Cycle Control,该BIt为PCI设备特有的。对于PCIe设备,该Bit无意义,必须硬连接到0 b。 |

| 8 | SERR# Enable,复位值为0。该Bit为1时,当PCIe设备出现错误,则允许发送Messages报文上报错误,具体的错误类型上报还需要看PCI Express Capability 的Device Control Register 寄存器。 |

| 9 | Fast Back-to-Back Transactions Enable,该BIt为PCI设备特有的。对于PCIe设备,该Bit无意义,必须硬连接到0 b。 |

| 10 | Interrupt Disable,控制PCIe生成INTx中断的能力。置位为1时,禁止PCIe产生INTx中断。需要注意的是,PCIe设备取消了INTx中断线,改成Message方式上报INTx中断。对于Bridge,该BIt只会影响自身产生中断,不会影响中断转发。 |

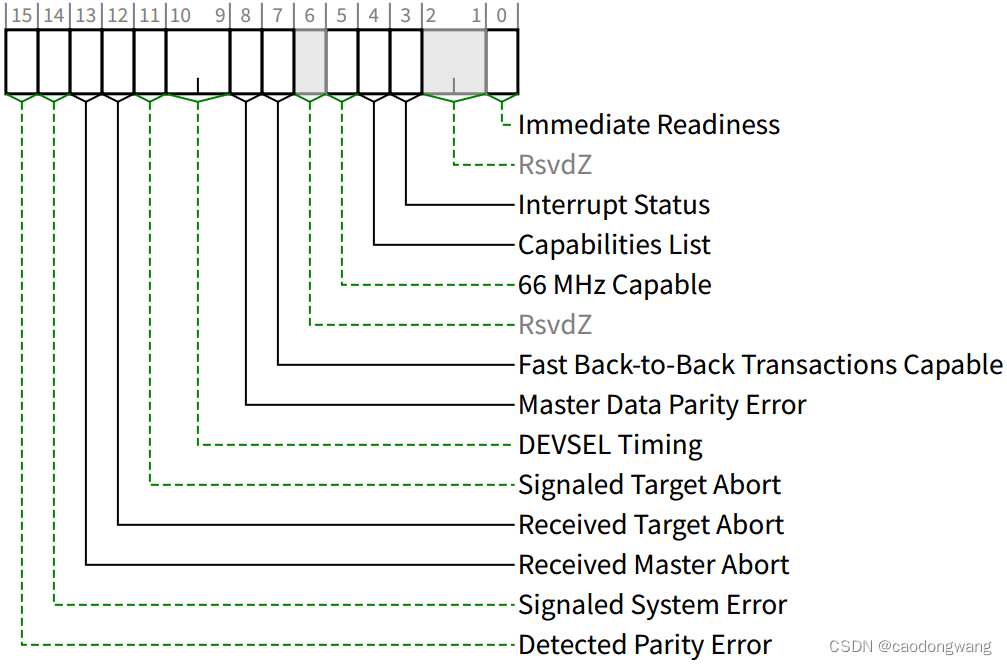

Status Register (Offset 06h)

该寄存器绝大多数位都是只读位,保存PCIe设备状态。

| bit | 功能 |

|---|---|

| 0 | Immediate Readiness,可选位,当该Bit为1时,表示该function可以随时响应有效的配置请求。比如对某个function执行FLR(function层面复位)操作,正常情况下,主机应至少等待100ms才能发出配置请求访问这个function,但该Bit置1的话,主机便可立即访问该function。 |

| 3 | Interrupt Status,复位值为0,只读Bit,当该Bit为1时,表示有一个INTx传统中断在设备内部挂起。驱动程序很少使用该Bit判断是否有中断未处理,大多数是采用BAR空间中自定义Bit来确定某个中断是否pending。 |

| 4 | Capabilities List,只读Bit,为1时表示Capability Pointer寄存器中值有效,对于PCIe设备,必需实现PCI Express Capability,因此,该BIt需要硬连线置1。 |

| 5 | 66 MHz Capable,该BIt为PCI设备特有的。对于PCIe设备,该Bit无意义,必须硬连接到0 b。 |

| 7 | Fast Back-to-Back Transactions Capable,该BIt为PCI设备特有的。对于PCIe设备,该Bit无意义,必须硬连接到0 b。 |

| 8 | Master Data Parity Error,复位值为0,如果 Comand 寄存器的 Parity Error Response 为 0,那么该位在任何情况下都是 0。若该Bit为1,则: 对于EP,表示接收到Poisoned Completion TLP或者发送了Poisoned Request TLP。 对于Bridge,表示从下游(Downstream)收到Poisoned Completion TLP或者向上游(Upstream)发送了Poisoned Request TLP。 |

| 10:9 | DEVSEL Timing,为PCI设备特有的。对于PCIe设备,该字段无意义,必须硬连线到00 b。 |

| 11 | Signaled Target Abort,复位值为0,设备收到 Posted 或者 Non-Posted 请求后,如果对该请求产生一个 Completer Abort Error,则将该Bit置为 1。如果收到的是 Non-Posted 请求,则设备需要向请求端回复一个带 Completion Abort Completion Status 的 Completion。 |

| 12 | Received Target Abort,该Bit写1清除,复位值为0,置1时,表示设备收到带有 Completer Abort Completion Status 的 Completion。 |

| 13 | Received Master Abort,该Bit写1清除,复位值为0,置1时,表示设备收到带有 Unsupported Request Completion Status 的 Completion。 |

| 14 | Signaled System Error,该Bit写1清除,复位值为0,在 Command 寄存器的 SERR# Enable 位设置为 1 的前提下,如果设备发送过 ERR_FATAL 或者 ERR_NONFATAL 消息,那么会将该位置为 1。 |

| 15 | Detected Parity Error, 该位的设置不受 Command 寄存器的 Parity Error Response 位的影响。 对于EP,设备收到 Poisoned TLP 时会将该位置 1。 对于Bridge,当它从上游(Primary )侧收到 Poisoned TLP 时,会将该位置 1。 |

Revision ID Register (Offset 08h)

修订ID寄存器存放硬件修订标识符,值由厂商自定义。一般系统会使用设备ID、厂商ID、修订ID来决定加载哪个驱动程序。厂商必须确保所选择的值不会导致使用不兼容的设备驱动程序。

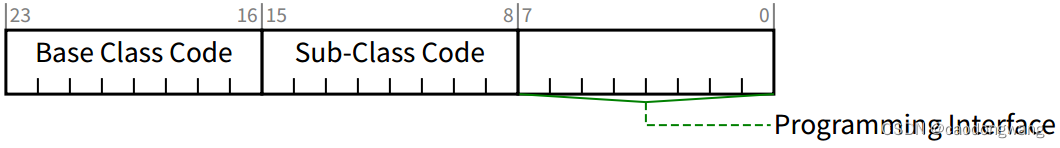

Class Code Register (Offset 09h)

设备分类信息寄存器, 只读,表示PCIe设备属于哪一种类别,如网卡,存储卡,显卡等,是需要重点关注的一个寄存器。

Base Class Code

| Base Class Code | Description |

|---|---|

| 0x00 | Unclassified device |

| 0x01 | Mass storage controller |

| 0x02 | Network controller |

| 0x03 | Display controller |

| 0x04 | Multimedia device |

| 0x05 | Memory Controller |

| 0x06 | Bridge Device |

| 0x07 | Simple communications controllers |

| 0x08 | Base system peripherals |

| 0x09 | Inupt devices |

| 0x0A | Docking Stations |

| 0x0B | Processorts |

| 0x0C | Serial bus controllers |

| 0x0D | Wireless controller |

| 0x0E | Intelligent controller |

| 0x0F | Satellite communications controller |

| 0x10 | Encryption controller |

| 0x11 | Signal processing controller |

| 0x12 | Processing accelerators |

| 0x13 | Non-Essential Instrumentation |

| 0x40 | Coprocessor |

| 0xFF | Unassigned class |

Sub Class Code & Programming Interface

Unclassified device(0x00)

| Sub Class Code | Description |

|---|---|

| 0x00 | Non-VGA unclassified device |

| 0x01 | VGA compatible unclassified device |

| 0x05 | Image coprocessor |

Mass storage controller(0x01)

| Sub Class Code | Description | Programming Interface & Description |

|---|---|---|

| 0x00 | SCSI storage controller | N/A |

| 0x01 | IDE interface | 0x00 ISA Compatibility mode-only controller 0x05 PCI native mode-only controller 0x0a ISA Compatibility mode controller, supports both channels switched to PCI native mode 0x0f PCI native mode controller, supports both channels switched to ISA compatibility mode 0x80 ISA Compatibility mode-only controller, supports bus mastering 0x85 PCI native mode-only controller, supports bus mastering 0x8a ISA Compatibility mode controller, supports both channels switched to PCI native mode, supports bus mastering 0x8f PCI native mode controller, supports both channels switched to ISA compatibility mode, supports bus mastering |

| 0x02 | Floppy disk controller | N/A |

| 0x03 | IPI bus controller | N/A |

| 0x04 | RAID bus controller | N/A |

| 0x05 | ATA controller | 0x20 ADMA single stepping 0x30 ADMA continuous operation |

| 0x06 | SATA controller | 0x00 Vendor specific 0x01 AHCI 1.0 0x02 Serial Storage Bus |

| 0x07 | Serial Attached SCSI controller | 0x01 Serial Storage Bus |

| 0x08 | Non-Volatile memory controller | 0x01 NVMHCI 0x02 NVM Express |

| 0x09 | Universal Flash Storage controller | 0x00 Vendor specific 0x01 UFSHCI |

| 0x80 | Mass storage controller | N/A |

Network controller(0x02)

| Sub Class Code | Description | Programming Interface & Description |

|---|---|---|

| 0x00 | Ethernet controller | N/A |

| 0x01 | Token ring network controller | N/A |

| 0x02 | FDDI network controller | N/A |

| 0x03 | ATM network controller | N/A |

| 0x04 | ISDN controller | N/A |

| 0x05 | WorldFip controller | N/A |

| 0x06 | PICMG controller | N/A |

| 0x07 | Infiniband controller | N/A |

| 0x08 | Fabric controller | N/A |

| 0x80 | Network controller | N/A |

Display controller(0x03)

| Sub Class Code | Description | Programming Interface & Description |

|---|---|---|

| 0x00 | VGA compatible controller | 0x00 VGA controller 0x001 8514 controller |

| 0x01 | XGA compatible controller | N/A |

| 0x02 | 3D controller | N/A |

| 0x80 | Display controller | N/A |

Multimedia controller(0x04)

| Sub Class Code | Description | Programming Interface & Description |

|---|---|---|

| 0x00 | Multimedia video controller | N/A |

| 0x01 | Multimedia audio controller | N/A |

| 0x02 | Computer telephony device | N/A |

| 0x03 | Audio device | N/A |

| 0x80 | Multimedia controller | N/A |

Memory controller(0x05)

| Sub Class Code | Description | Programming Interface & Description |

|---|---|---|

| 0x00 | RAM memory | N/A |

| 0x01 | FLASH memory | N/A |

| 0x02 | CXL | 0x00 CXL Memory Device - vendor specific 0x10 CXL Memory Device (CXL 2.x) |

| 0x80 | Memory controller | N/A |

Bridge(0x06)

| Sub Class Code | Description | Programming Interface & Description |

|---|---|---|

| 0x00 | Host bridge | N/A |

| 0x01 | ISA bridge | N/A |

| 0x02 | EISA bridge | N/A |

| 0x03 | MicroChannel bridge | N/A |

| 0x04 | PCI bridge | 0x00 Normal decode 0x01 Subtractive decode |

| 0x05 | PCMCIA bridge | N/A |

| 0x06 | NuBus bridge | N/A |

| 0x07 | CardBus bridge | N/A |

| 0x08 | RACEway bridge | 0x00 Transparent mode 0x01 Endpoint mode |

| 0x09 | Semi-transparent PCI-to-PCI bridge | 0x40 Primary bus towards host CPU 0x80 Secondary bus towards host CPU |

| 0x0a | InfiniBand to PCI host bridge | N/A |

| 0x80 | Bridge | N/A |

Communication controller(0x07)

| Sub Class Code | Description | Programming Interface & Description |

|---|---|---|

| 0x00 | Serial controller | 0x00 8250 0x01 16450 0x02 16550 0x03 16650 0x04 16750 0x05 16850 0x06 16950 |

| 0x01 | Parallel controller | 0x00 SPP 0x01 BiDir 0x02 ECP 0x03 IEEE1284 0xfe IEEE1284 Target |

| 0x02 | Multiport serial controller | N/A |

| 0x03 | Modem | 0x00 Generic 0x01 Hayes/16450 0x02 Hayes/16550 0x03 Hayes/16650 0x04 Hayes/16750 |

| 0x04 | GPIB controller | N/A |

| 0x05 | Smard Card controller | N/A |

| 0x80 | Communication controller | N/A |

Generic system peripheral(0x08)

| Sub Class Code | Description | Programming Interface & Description |

|---|---|---|

| 0x00 | PIC | 0x00 8259 0x01 ISA PIC 0x02 EISA PIC 0x10 IO-APIC 0x20 IO(X)-APIC |

| 0x01 | DMA controller | 0x00 8237 0x01 ISA DMA 0x02 EISA DMA |

| 0x02 | Timer | 0x00 8254 0x01 ISA Timer 0x02 EISA Timers 0x03 HPET |

| 0x03 | RTC | 0x00 Generic 0x01 ISA RTC |

| 0x04 | PCI Hot-plug controller | N/A |

| 0x05 | SD Host controller | N/A |

| 0x06 | IOMMU | N/A |

| 0x80 | System peripheral | |

| 0x99 | Timing Card | 0x01 TAP Timing Card |

Input device controller(0x09)

| Sub Class Code | Description | Programming Interface & Description |

|---|---|---|

| 0x00 | Keyboard controller | N/A |

| 0x01 | Digitizer Pen | N/A |

| 0x02 | Mouse controller | N/A |

| 0x03 | Scanner controller | N/A |

| 0x04 | Gameport controller | 0x00 Generic 0x10 Extended |

| 0x80 | Input device controller | N/A |

Docking station(0x0a)

| Sub Class Code | Description | Programming Interface & Description |

|---|---|---|

| 0x00 | Generic Docking Station | N/A |

| 0x80 | Docking Station | N/A |

Processor(0x0b)

| Sub Class Code | Description | Programming Interface & Description |

|---|---|---|

| 0x00 | 386 | N/A |

| 0x01 | 486 | N/A |

| 0x02 | Pentium | N/A |

| 0x10 | Alpha | N/A |

| 0x20 | Power PC | N/A |

| 0x30 | MIPS | N/A |

| 0x40 | Co-processor | N/A |

Serial bus controller(0x0c)

| Sub Class Code | Description | Programming Interface & Description |

|---|---|---|

| 0x00 | FireWire (IEEE 1394) | 0x00 Generic 0x10 OHCI |

| 0x01 | ACCESS Bus | N/A |

| 0x02 | SSA | N/A |

| 0x03 | USB controller | 0x00 UHCI 0x10 OHCI 0x20 EHCI 0x30 XHCI 0x40 USB4 Host Interface 0x80 Unspecified 0xfe USB Device |

| 0x04 | Fibre Channel | N/A |

| 0x05 | SMBus | N/A |

| 0x06 | InfiniBand | N/A |

| 0x07 | IPMI Interface | 0x00 SMIC 0x01 KCS 0x02 BT (Block Transfer) |

| 0x08 | SERCOS interface | N/A |

| 0x09 | CANBUS | N/A |

| 0x80 | Serial bus controller | N/A |

Wireless controller(0x0d)

| Sub Class Code | Description | Programming Interface & Description |

|---|---|---|

| 0x00 | IRDA controller | N/A |

| 0x01 | Consumer IR controller | N/A |

| 0x10 | RF controller | N/A |

| 0x11 | Bluetooth | N/A |

| 0x12 | Broadband | N/A |

| 0x20 | 802.1a controller | N/A |

| 0x21 | 802.1b controller | N/A |

| 0x80 | Wireless controller | N/A |

Intelligent controller(0x0e)

| Sub Class Code | Description | Programming Interface & Description |

|---|---|---|

| 0x00 | I2O | N/A |

Satellite communications controller(0x0f)

| Sub Class Code | Description | Programming Interface & Description |

|---|---|---|

| 0x01 | Satellite TV controller | N/A |

| 0x02 | Satellite audio communication controller | N/A |

| 0x03 | Satellite voice communication controller | N/A |

| 0x04 | Satellite data communication controller | N/A |

Encryption controller(0x10)

| Sub Class Code | Description | Programming Interface & Description |

|---|---|---|

| 0x00 | Network and computing encryption device | N/A |

| 0x10 | Entertainment encryption device | N/A |

| 0x80 | Encryption controller | N/A |

Signal processing controller(0x11)

| Sub Class Code | Description | Programming Interface & Description |

|---|---|---|

| 0x00 | DPIO module | N/A |

| 0x01 | Performance counters | N/A |

| 0x10 | Communication synchronizer | N/A |

| 0x20 | Signal processing management | N/A |

| 0x80 | Signal processing controller | N/A |

Processing accelerators(0x12)

| Sub Class Code | Description | Programming Interface & Description |

|---|---|---|

| 0x00 | Processing accelerators | N/A |

| 0x01 | SNIA Smart Data Accelerator Interface (SDXI) controller | N/A |

Non-Essential Instrumentation(0x13)

N/A

Coprocessor(0x40)

N/A

Unassigned class(0xff)

N/A

Cache Line Size Register (Offset 0Ch)

cache缓存大小,是为了PCI设备设计的。对于PCIe设备,该寄存器的值无意义。

Latency Timer Register (Offset 0Dh)

为了PCI bridge设备设计的,对于PCIe设备,该寄存器的值无意义。

Header Type Register (Offset 0Eh)

PCIe设备头类型寄存器, 表示该设备是PCIe EP设备还是PCIe bridge设备。 PCIe 配置空间是type0类型还是type1类型,就是由该寄存器定义。该寄存器只读,由8位组成。

- 第 7 Bit 为1表示当前PCI设备为多功能设备,为0表示为单功能设备(对于单PF多VF的设备,需要填写为0)。

- 第 6-0 Bit 表示当前配置空间类型,为0表示普通PCIe设备配置空间,为1表示PCIe bridge设备配置空间,为2表示Cardbus桥片配置空间。

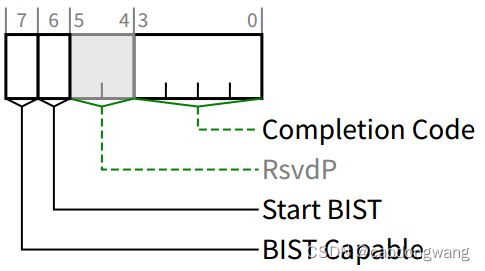

BIST Register (Offset 0Fh)

Built In Self Test(内部自检测试),用于BIST的控制和状态检查,调用BIST功能的function不能影响PCIe link状态。

| Bit | Description |

|---|---|

| 3:0 | Completion Code,表示自检的完成状态,0000b表示自检测ok,非0000b表示自检测失败。 |

| 6 | Start BIST,用于软件启用function自检测功能,当 BIST Capable 为1时,系统软件可以通过对该BIt写1激活function自检。function应保证在2s内完成自检,并清除该Bit,将自检结果显示在Completion Code字段。若function在2s内未清除该Bit,则软件可以认为设备出现故障,进行故障处理操作。 |

| 7 | BIST Capable,为1时,表示支持BIST功能(内部自检测试)。 |

Base Address Registers (Offset 10h - 24h)

BAR地址寄存器负责PCIe设备内部空间的映射。

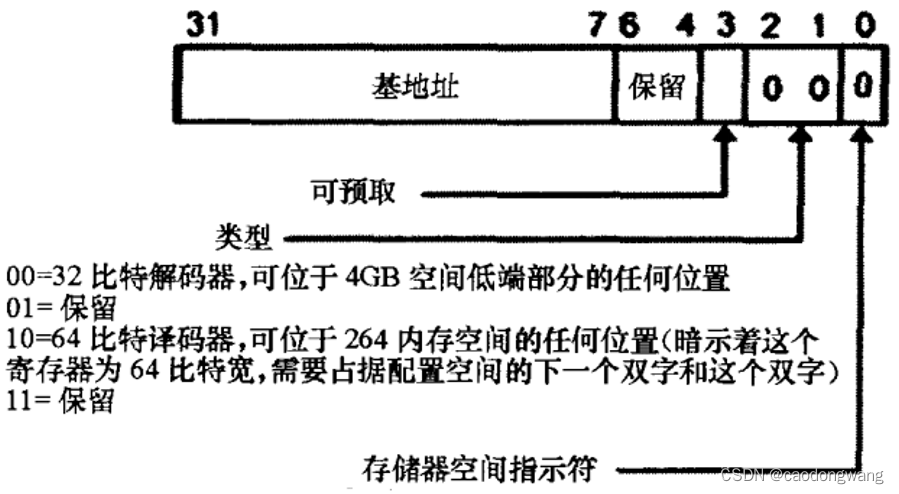

PCIe EP配置空间头部有6个BAR(Base Address Registers)寄存器, 决定PCIe设备空间映射到系统空间具体位置的寄存器, BAR记录了设备所需要的地址空间的类型(memory space或者I/O space),基址以及其他属性。 BAR的格式如下:

| Bit | 描述 |

|---|---|

| 0 | 表示这个BAR是I/O空间还是mem空间,1表示I/O空间,0表示mem空间。 |

| 2:1 | 表示这个BAR是32bit还是64bit,00b表示32Bit,10b表示64Bit,当BAR为64Bit时,其高32Bit在下一个BAR中填写,比如BAR0和BAR1组成一个64Bit BAR寄存器。注意,由于PCIe Bridge的non prefetchable memory limit/base(offset 0x20h)位宽限制,PCIe EP设备不可预取BAR只能使用32 Bit,即使该字段值为10b,host也只会分配32 Bit的地址空间下来。 |

| 3 | 1表示mem空间可预取,0表示不可预取。注意,如果BAR支持可预取,请确保BAR空间没有副作用(读无副作用、内部值不会意外改变)。 |

type0(PCIe EP设备)有6个32bit的BAR寄存器,type1(PCIe Bridge设备)有2个32bit的BAR寄存器。每一个BAR地址对应一个地址空间。

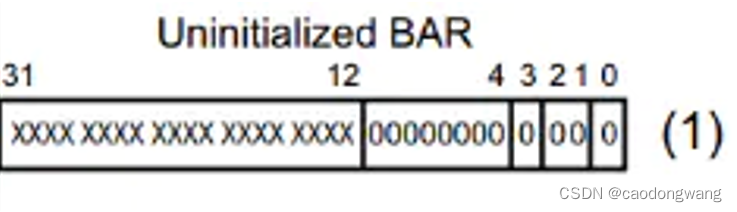

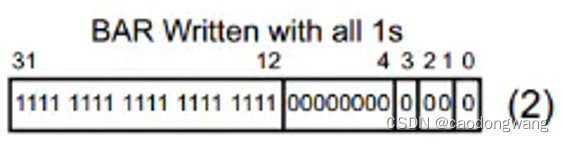

在BAR寄存器有些bit是只读的,是PCI设备在出厂前就固定好的bit,写全1进去,如果值保持不变,就说明这些bit是厂家固化好的,这些固化好的bit提供了这块内部空间的一些信息。

举个例子:

上电时,系统软件首先会读取PCIe设备的BAR0,得到数据:

然后系统软件往该BAR0写入全1,得到:

低12bit没变,表明该设备空间大小是4KB(2的12次方),BAR地址的低4位表明了该存储空间的一些属性。然后系统软件根据这些信息,在系统内存空间找到这样一块地方来映射这4KB的空间,把分配的基地址写入到BAR寄存器。

系统启动时通过BAR地址把PCIe设备空间映射到存储器空间,CPU要访问该PCIe设备空间,只需访问对应的存储器空间。CPU发出一个物理地址,RC检查该地址,如果发现该内存空间地址是某个PCIe设备空间的映射,就会触发其产生TLP,去访问对应的PCIe设备,读取或者写入PCIe设备。

Cardbus CIS Pointer Register (Offset 28h)

为了PCI bridge设备设计的,对于PCIe设备,该寄存器的值无意义。

Subsystem Vendor ID Register/Subsystem ID Register (Offset 2Ch/2Eh)

PCIe设备的子系统厂商和子系统ID。比如inter提供了一个PCIe总线接口的IP核,并且IP核固化了设备ID和厂商ID为inter,但其他厂商使用这个IP生产了设备,所以可以通过子系统厂商和子系统ID来区分不同设备。

Expansion ROM Base Address Register (Offset 30h)

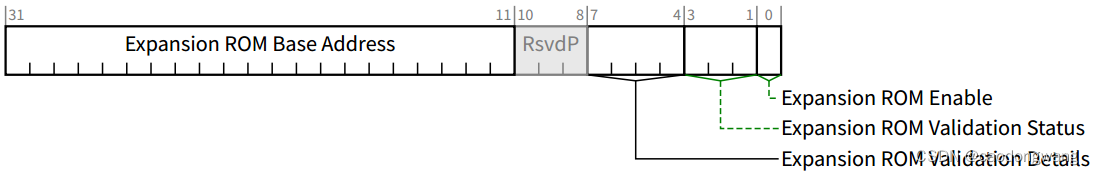

扩展ROM映射基地址寄存器。分配给ROM使用,用于PCIe设备在处理器还没有运行操作系统之前,完成基本的初始化设置。比如显卡、键盘、硬盘等设备,在处理器初始化过程中将运行这段ROM程序,初始化这些PCIe设备。这个寄存器记载这段ROM程序的基地址(类似BAR寄存器)。

| Bit | 描述 |

|---|---|

| 0 | Expansion ROM Enable,使能位,表示这个设备是否支持ExROM,1表示支持,0表示不支持。 |

| 3:1 | Expansion ROM Validation Status,表示硬件验证ExROM内容的状态。例如,厂商制造了PCIe设备卖给客户,客户可以自行更换有效可信的ExROM程序,如果非法,则通过该字段告知host主机,让host主机忽略执行ExROM程序。 000b:验证不支持 001b:验证进行中 010b:验证通过,内容有效,但未执行信任测试 011b:验证通过,内容有效且可信 100b:验证失败,内容无效 101b:验证失败,内容有效但不可信(例如,过时、过期或已撤销的证书) 110b:警告通过,具有特定实现警告,内容有效,但未执行信任测试 111b:警告通过,具有特定实现警告,内容有效且可信。 |

| 7:4 | Expansion ROM Validation Details,ExROM验证详细信息,包含与Expansion ROM验证相关的可选的、特定于实现的详细信息。 1. 如果function不支持验证,则此字段为RsvdP(保留位)。 2. 此字段是可选的。当支持验证但未实现此字段时,此字段必须硬连到0000b。此字段中的任何未使用位都可以硬连到0b。 3. 如果验证正在进行中(Expansion ROM验证状态为001b),此字段的非零值表示验证进度的特定于实现的指示(例如,50%完成)。值0000b表示未提供验证进度信息。 4. 如果验证已完成(Expansion ROM验证状态为010b到111b),此字段中的非零值表示附加的特定于实现的信息。值0000b表示未提供信息。 5. 如果功能支持验证并具有用于Expansion ROM的增强分配能力(EA条目),则此字段为HwInit(硬件初始化)。 否则,此字段为只读位。 6. 此字段仅通过冷复位重置,并不受其他复位的影响。 7. 一旦验证过程完成,此字段的值不能更改。 8. 建议系统软件在报告验证状态(例如,错误日志)时包含此字段的值。 |

Capabilities Pointer (Offset 34h)

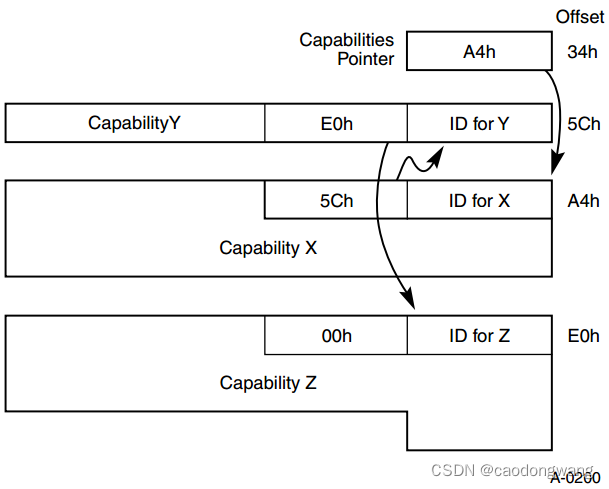

PCIe capbility的地址偏移, capbility用于表示PCIe设备支持的能力。该寄存器存放Capabilities 结构链表的头指针。在一个PCIe 设备中,可能含有多个Capability 结构,这些寄存器组成一个链表:

注意,PCIe设备必须要实现PCI Power Management Capability和PCI Express Capability,所以该字段必然不会为0。

Interrupt Line Register (Offset 3Ch)

表示当前PCIe设备使用的中断向量号,注意,这是由系统软件配置下来的,PCIe硬件不使用该寄存器。

Interrupt Pin Register (Offset 3Dh)

传统中断引脚只读寄存器,如果PCIe设备不支持传统中断,该寄存器值必须为0x00h。0x01~0x04值对应INTA、INTB、INTC和INTD中断,对于单function的PCIe设备,只能使用INTA,对于多function的PCIe设备,需要依次按序使用中断引脚号。

Min_Gnt Register/Max_Lat Register (Offset 3Eh/3Fh)

为了PCI设备设计的。对于PCIe设备,该寄存器的值无意义。

下一篇将讲解PCIe Bridge标准配置空间。