文章目录

- Features of RH850/P1x-C CSIH

- Units

- Register Base Address

- Clock Supply

- Interrupt Requests

- Hardware Reset

- External Input/Output Signals

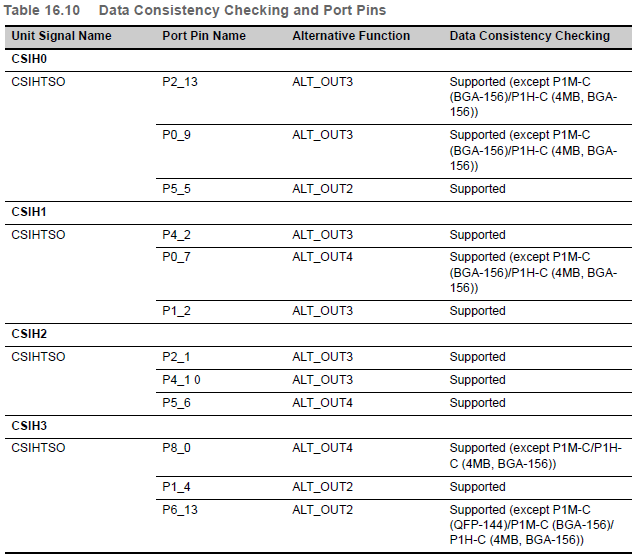

- 数据一致性检查

- Overview

- Functional Overview

- Functional Overview Description

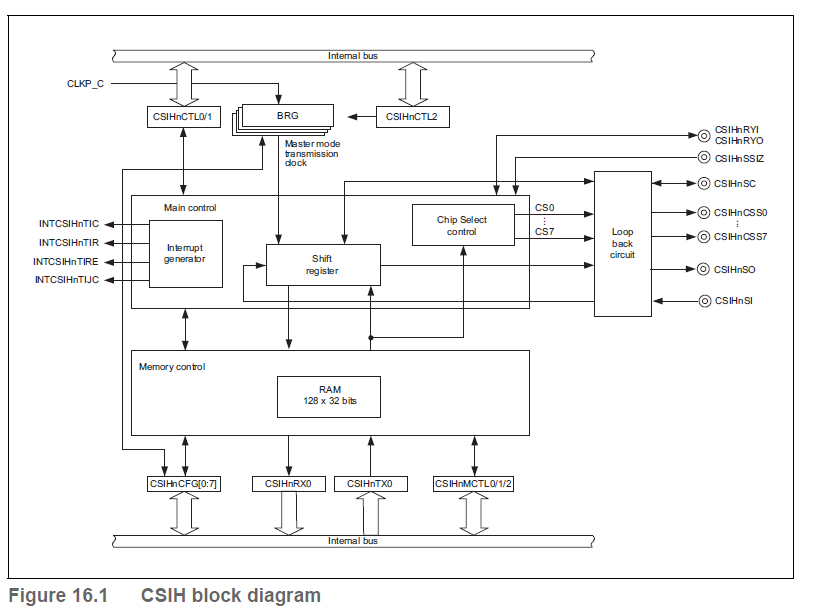

- Block Diagram

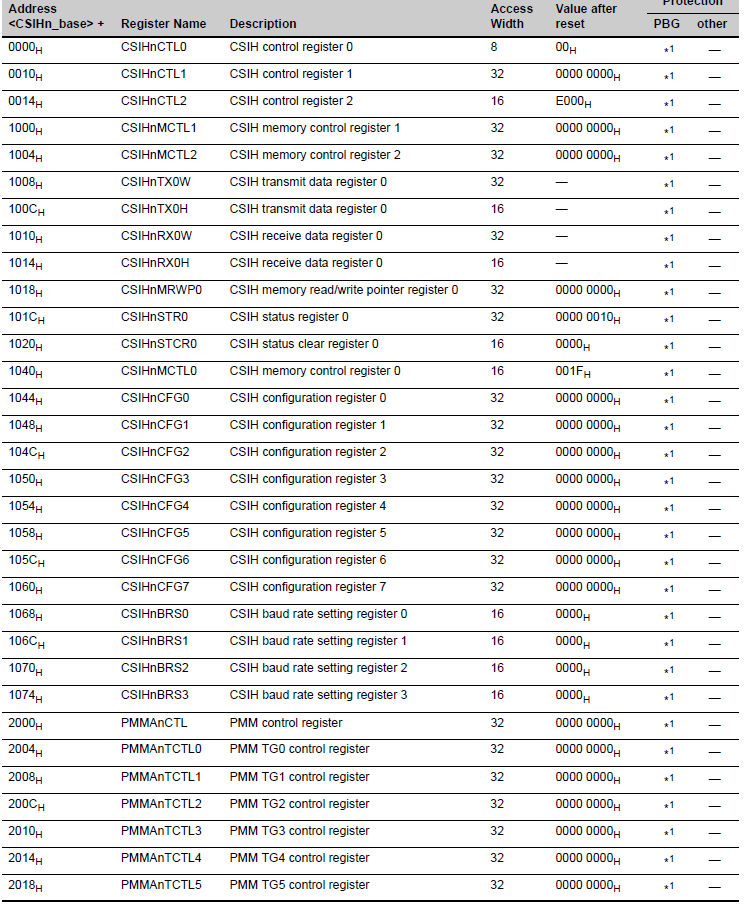

- Registers

- List of Registers

- CSIHnCTL0 — CSIH control register 0

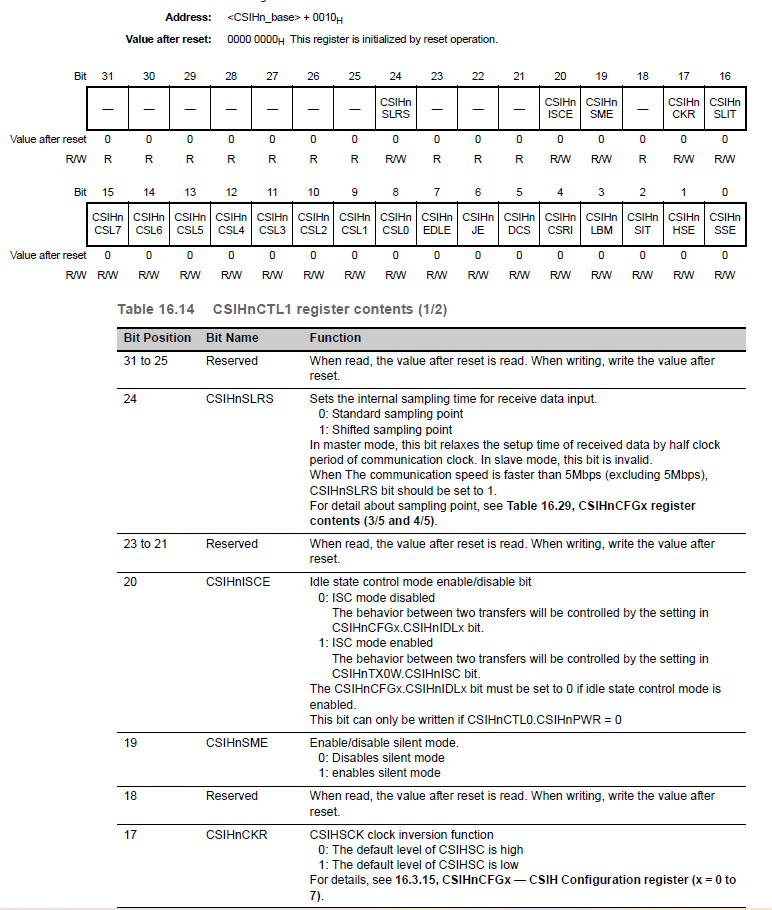

- CSIHnCTL1 — CSIH control register 1

- CSIHnCTL2 — CSIH control register 2

- CSIHnMCTL1 — CSIH Memory control register 1

- CSIHnMCTL2 — CSIH Memory control register 2

- CSIHnTX0W — CSIH transmit data register 0 for word access

- CSIHnTX0H — CSIH transmit data register 0 for half word access

- CSIHnRX0W — CSIH receive data register 0 for word access

- CSIHnRX0H — CSIH receive data register 0 for half word access

- CSIHnMRWP0 — CSIH memory read/write pointer register 0

- CSIHnSTR0 — CSIH status register 0

- CSIHnSTCR0 — CSIH status clear register 0

- CSIHnMCTL0 — CSIH Memory control register 0

- CSIHnCFGx — CSIH Configuration register (x = 0 to 7)

- CSIHnBRSx — CSIH baud rate setting register (x = 0 to 3)

- PMMAnCTL — PMM control register

- PMMAnTCTLx — PMM TG control register (x = 0 to 7)

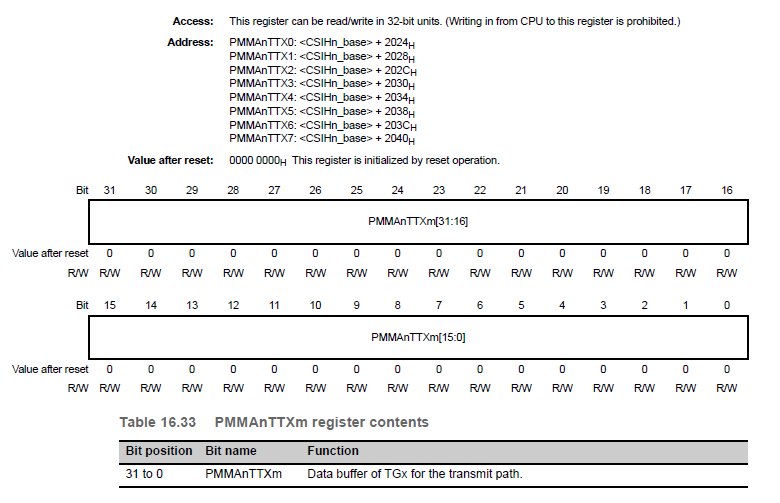

- PMMAnTTXm — PMM TG transmit buffer (x = 0 to 7)

- PMMAnRX — PMM TG receive buffer

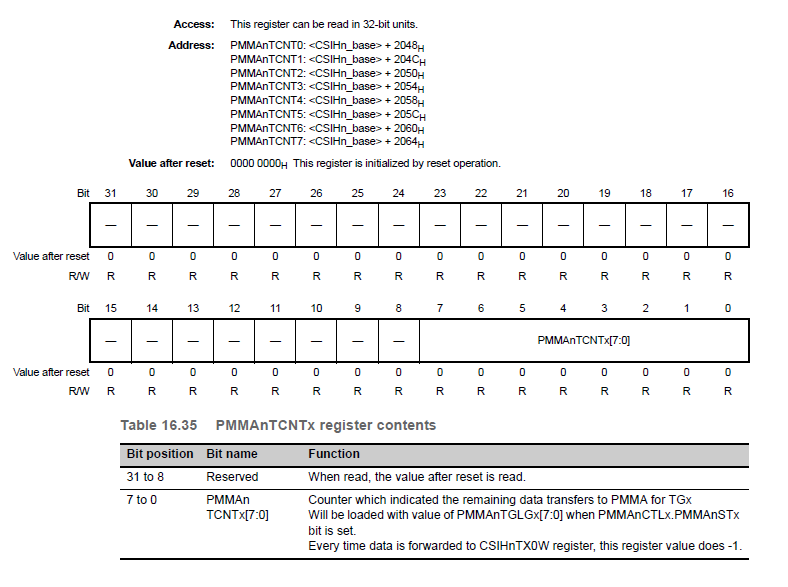

- PMMAnTCNTx — PMM TGx counter (x = 0 to 7)

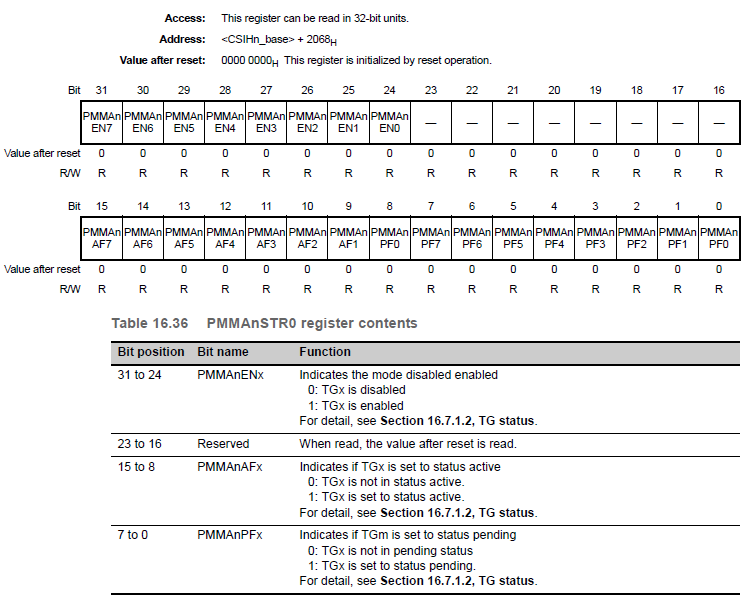

- PMMAnSTR0 — PMM TG status register 0

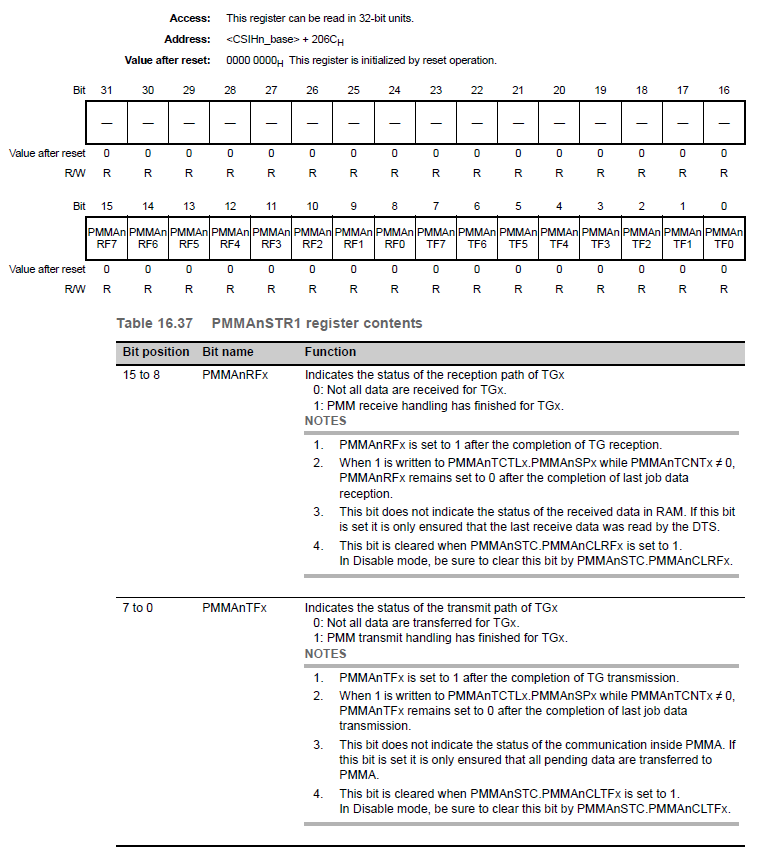

- PMMAnSTR1 — PMM TG status register 1

- PMMAnSTC — PMM TG status clear register

- Interrupt Sources

- Overview

- General interrupt delay

- CSIHTIC (communication interrupt)<br>

- CSIHTIC in direct access mode

- CSIHTIC in FIFO mode

- CSIHTIC in job mode

- CSIHTIR in direct access mode

- CSIHTIR in dual buffer mode

- CSIHTIRE (reception error interrupt)

- CSIHTIJC (job completion interrupt)

- Operation

- Master/slave connections

- Transmission clock selection

- Operating Procedures

- Procedures in direct access mode

- Transmit/receive in master mode when job mode is disabled

- Transmit/receive in master mode when job mode is enabled

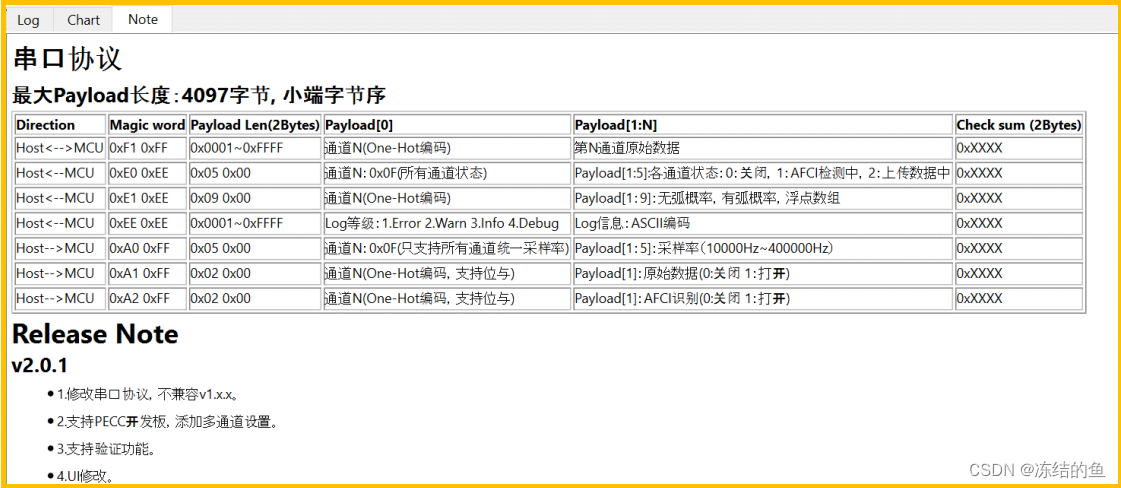

- Priority Management Module (PMM)

- Transfer groups

- TG structure

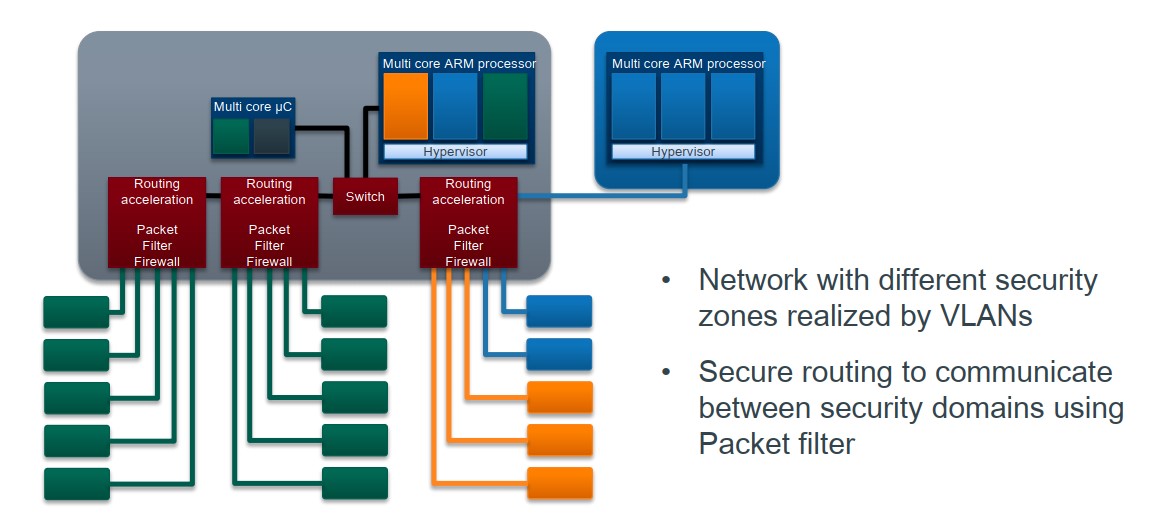

- Block Diagram

- Functional Overview

Features of RH850/P1x-C CSIH

CSIH其实就是SPI

该模块是时钟串行接口(CSIH),具有以下附加功能。

•灵活的空闲状态控制方式

•静默模式

•采样点修改功能

•优先级管理模块(PMM)功能

由于优先级管理模块功能是上述功能中一个比较大的附加功能,所以在CSIH基本功能介绍之后,将对其进行单独介绍。

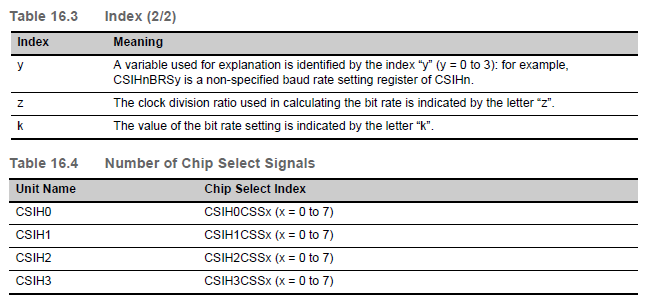

Units

该微控制器具有以下数量的CSIH单元。

每个CSIH单元有一个通道接口。

每个通道各有8个片选

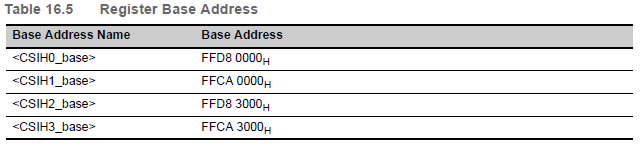

Register Base Address

下表列出了CSIH基址。

CSIH寄存器地址通常作为基址的偏移量给出

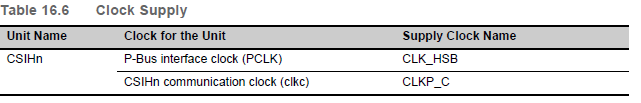

Clock Supply

下表列出了CSIH和CSIH提供的时钟。

一般SPI时钟为160M

注:若为P1M-C,则必须满足P1H-C以下时钟条件

CLK_HSB < CLKP_C < (3 × CLK_HSB)

在P1H-CE的情况下,必须满足以下时钟条件

CLK_HSB <= CLKP_C < (3 * CLK_HSB)

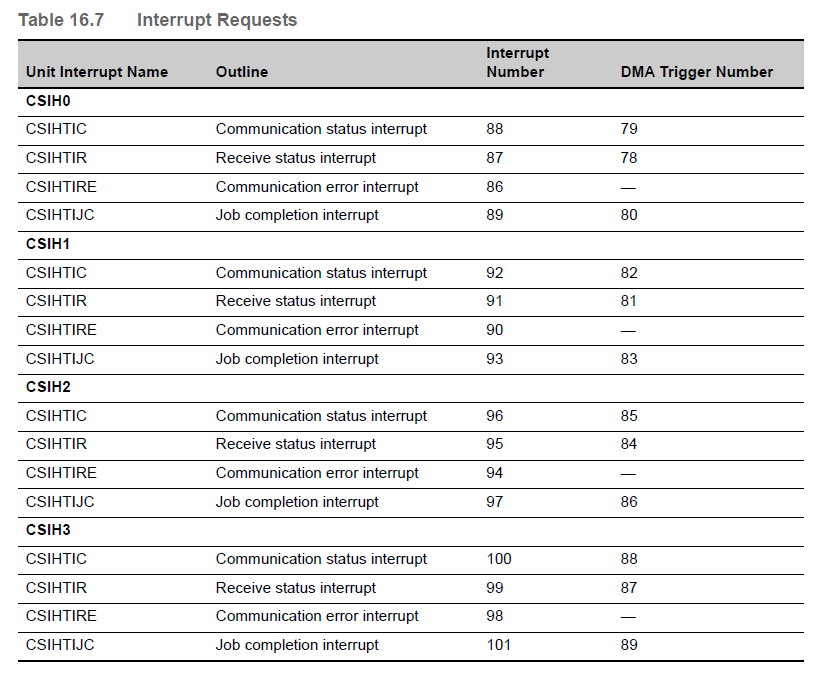

Interrupt Requests

下表列出了CSIH中断请求

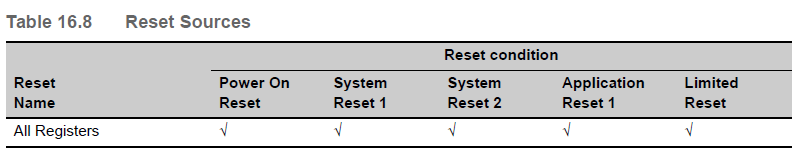

Hardware Reset

下表列出了CSIH复位源。CSIH由这些复位源初始化

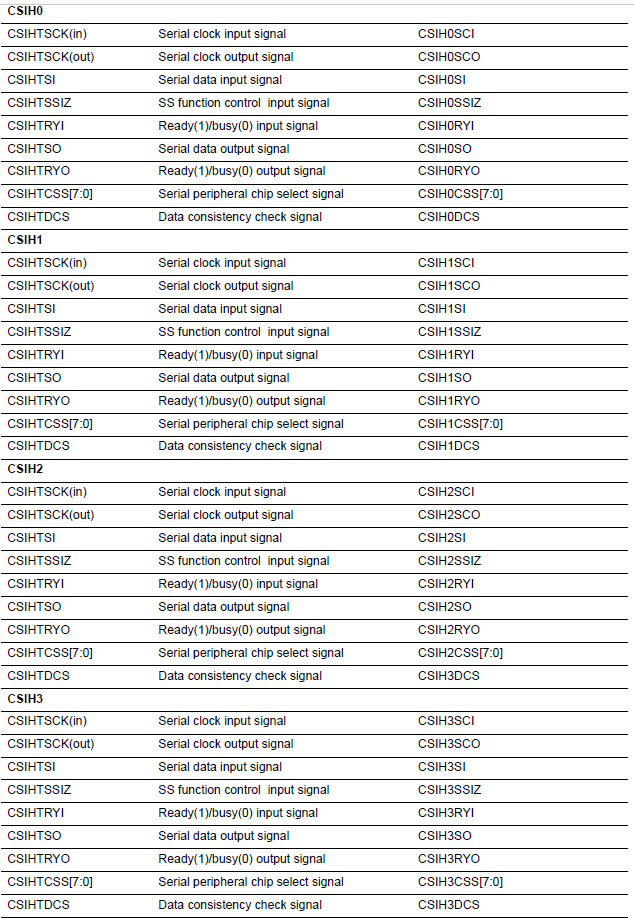

External Input/Output Signals

数据一致性检查

下表列出了CSIHnSO引脚函数复用的端口引脚,以及CSIHnSO引脚函数是否支持数据一致性检查。请参见16.5.12错误检测,了解数据一致性检查的详细信息

Overview

Functional Overview

•三线串行同步数据传输

•全双工操作(同时发送和接收),仅接收模式或仅发送模式

•可选择主模式和从模式

•时钟和数据的相位可选的每个芯片选择

•数据传输与MSB或LSB首先选择每个芯片选择

•传输数据长度可选择从2到16位在1位单位为每个芯片选择

•EDL(扩展数据长度)功能,用于传输超过16位的数据

•最大传输速度:

—主模式:20mhz

—in slave mode: 20mhz

•波特率可选择由BRG(波特率发生器)输出(在主模式)或由从时钟

•发送模式,接收模式和发送/接收模式可选

•缓冲区大小为128字(1字是数据32位+ ECC 7位)

•内存模式可选(FIFO,双缓冲区,传输缓冲,和直接访问)

•内置握手功能

•错误检测(数据一致性检查,奇偶校验,超时,溢出和溢出)

•AUTOSAR JOB启用控制位

•RCB(广播隐性配置)位用于广播

•LBM(回环模式)功能自检

•四种不同的中断请求信号。(INTCSIHnTIC, INTCSIHnTIR, INTCSIHnTIR,INTCSIHnTIJC)

•IDLE状态控制功能。

•静默模式通信,延长空闲时间

•自动生成芯片选择输出信号与可配置的激活电平

•数据传输没有激活芯片选择

•每个芯片选择的传输速度是可选择的四个预定义波特率(在主模式)或时钟输入信号从主(在从模式)

•对所有CSIH寄存器的完全DMA支持(SPI接口应该由多个总线主机访问,而无需显式的sw同步)

Functional Overview Description

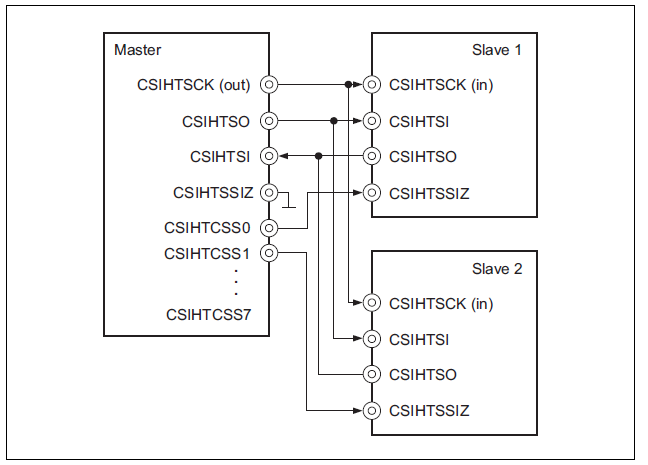

时钟串行接口使用三种信号进行通信:

•传输时钟CSIHTSCK(主模式输出,从模式输入)

•数据输出信号CSIHTSO

•数据输入信号CSIHTSI

附加信号可用于外部控制和监测。

•CSIHTSSIZ:从机选择输入信号

•CSIHTRYO: Ready/busy输出信号(握手信号)

•CSIHTRYI:就绪/忙输入信号(握手信号)

•CSIHTCSS[7:0]:芯片选择信号

•CSIHTDCS:数据一致性检查信号

一般用到的就四根线,时钟,数据输出,数据输入,片选

数据传输采用位方式和串行方式,与传输时钟同步。

下表显示了用于设置CSIH的最重要的寄存器。

Block Diagram

框图显示了CSIH的主要组件。

在主模式下,传输时钟CSIHTSCK由内置波特率发生器产生(BRG)。在从模式下,传输时钟由外部源提供。

内置内存可以配置为FIFO、双缓冲区(单独的发送和接收缓冲区)或仅发送缓冲区。也可以绕过它进行数据传输和接收,而不需要缓冲。

回环电路将CSIH完全从端口断开,并支持内部自检。

可以预配置4种不同的波特率,可以为每个CS单独选择

Registers

List of Registers

CSIHnCTL0 — CSIH control register 0

该寄存器控制操作时钟并启用/禁用发送/接收以及用于发送和/或接收的存储部分。它强制在当前作业结束时停止通信

CSIHnPWR:控制操作时钟

0:停止操作clock0。

1:提供操作时钟。

将CSIHnPWR清零复位内部电路,停止运行,复位CSIH切换到备用状态。内部电路不提供时钟。如果CSIHnPWR在通信过程中被清除,正在进行的通信将立即中止。

CSIHnTXE:使能发送

0:表示禁止传输

1:表示使能传输

CSIHnRXE:使能接收

0:表示无法接收

1:表示开启接收功能。

CSIHnJOBE:在当前作业结束时停止通信(发送CSIHnEOJ = 1的数据后通信结束):

0:未请求停止通信。

1:停止通讯。

CSIHnMBS:绕过内存传输和/或接收数据。

0:内存模式

CSIH存储器用于传输和/或接收数据。

1:直连模式

CSIH内存被绕过。

CSIHnCTL1 — CSIH control register 1

这个寄存器指定中断时间和中断延迟模式。它启用/禁用扩展数据长度控制、数据一致性检查、环回模式、握手功能和作业模式。它选择每个芯片选择信号的主动输出电平以及最终数据传输后芯片选择信号的行为。

CSIHnSLRS:设置接收数据输入的内部采样时间。

0:标准采样点

1:移位采样点

在主模式下,该位将接收数据的设置时间放宽通信时钟的半个时钟周期。在从模式下,该位无效。

当通信速度大于5Mbps(不含5Mbps)时,

CSIHnSLRS位应该设置为1。

CSIHnISCE:空闲状态控制模式使能位

0:ISC mode disabled,两次传输之间的行为将由CSIHnCFGx.CSIHnIDLx位中的设置控制。

1:ISC mode enabled,两次传输之间的行为将由CSIHnTX0W.CSIHnISC位中的设置控制。

当使能idle state control时,CSIHnCFGx.CSIHnIDLx bit必须为0

此位只能在CSIHnCTL0.CSIHnPWR = 0时写入

CSIHnSME:使能静默模式,1使能

CSIHnCKR:CSIHSCK时钟反转功能

0: CSIHSC的默认电平为高

1: CSIHSC的默认电平为低

CSIHnSLIT:选择INTCSIHnTIC中断的时间。

0:正常中断定时(传输后产生中断)

1:一旦CSIHnTX0寄存器的内容被转移到移位寄存器,就会产生中断(该功能仅在直接访问模式下激活)。

CSIHnCSLx(x = 0 to 7):配置片选信号的激活电平,0低电平,1高电平

CSIHnEDL:使能扩展数据长度模式(EDL),1使能

CSIHnJE:使能job模式,1使能

CSIHnDCS:使能数据一致性检查,1使能

CSIHnCSRI:定义最后一次数据传输后的芯片选择信号行为。

0:芯片选择信号保持活动电平。

1:芯片选择信号返回非活动电平

CSIHnLBM:是否激活环回模式,1激活。环回模式下,数据输入与输出直接相连

CSIHnSIT:选择中断延迟模式。

0:表示无延迟。

1:所有中断都产生半时钟延时

CSIHnHSE:启用/禁用握手模式。

0:关闭握手功能。

1:开启握手功能。

CSIHnSSE:启用/禁用slave选择功能。

0:忽略输入信号CSIHnSSIZ。

1:输入信号CSIHnSSIZ被识别。

如果不使用从选择功能,则必须将该位设置为0

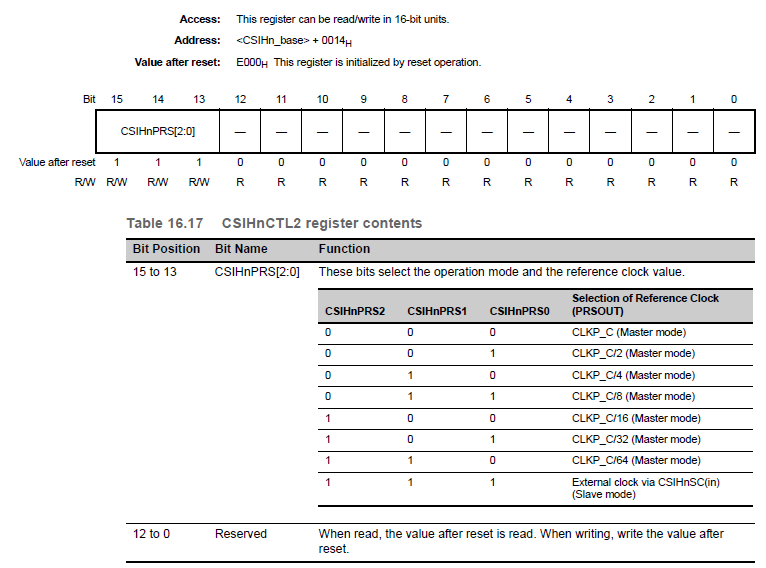

CSIHnCTL2 — CSIH control register 2

这个寄存器为四个波特率发生器选择工作模式和输入时钟

CSIHnPRS[2:0]:这些位选择操作模式和参考时钟值。

三个bit都为1时,表示从模式,其他值表示分频

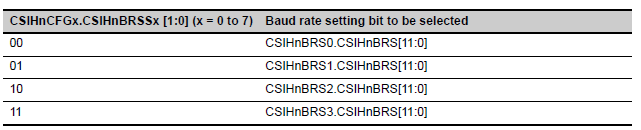

通过CSIHnCFGx.CSIHnBRSSx[1:0]选择CSIHnBRSy四个波特率中的一个,通过CSIHnBRSy.CSIHnBRSy设置波特率

下表显示了当CSIHnPRS[2:0]位值为α时,波特率设置CSIHnBRSy[11:0]与CSIHnBRSSx[1:0]位选择的波特率之间的关系。

当CLKP_C = 80MHz时,主模式下的“快速波特率”为20.0Mbps (CLKP_C/4)

13.3Mbps (CLKP_C/6)在Slave模式。

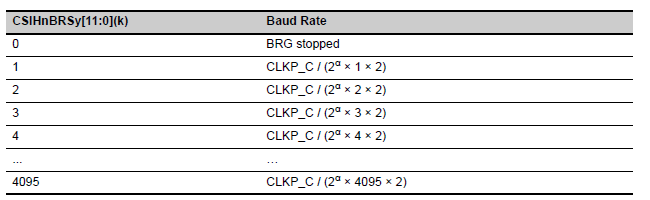

CSIHnMCTL1 — CSIH Memory control register 1

这个寄存器选择条件来产生中断请求,CSIHTIC和CSIHTIR在FIFO模式下。

CSIHnFES[6:0]:选择在FIFO模式下生成CSIHTIC中断(传输数据为空)的条件。

当要在FIFO中传输的未发送数据的数量(CSIHnSTR0.CSIHnSPF[7:0])等于CSIHnMCTL1.CSIHnFES[6:0]时,FIFO空标志(CSIHnSTR0.CSIHnMF位)被设置为1,并且产生CSIHTIC中断请求

CSIHnFFS[6:0]:选择在FIFO模式下生成CSIHTIR中断(接收数据full)的条件

当FIFO中接收到的数据的数量(CSIHnSTR0.CSIHnSRP[7:0])等于CSIHnMCTL1.CSIHnFS[6:0]时,FIFO满标志(CSIHnSTR0.CSIHnFF位)被设置为1,并且产生CSIHTIR中断请求

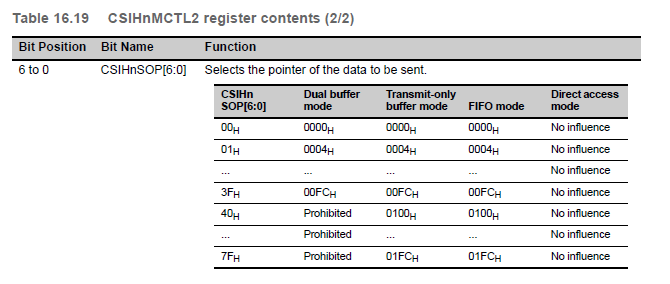

CSIHnMCTL2 — CSIH Memory control register 2

该寄存器控制双缓冲或仅传输缓冲模式下存储器的操作,并触发在缓冲模式下开始通信。

CSIHnBTST:提供缓冲区传输的启动触发器。

0:不操作。

1:发出start transfer命令。

此位只能在双缓冲模式和仅传输缓冲模式下使用。

CSIHnND[7:0]:指定每种内存模式的数据数量。

读取值表示剩余的通信数据数。

数据传输完成后,该数值会自动递减(直连模式下不会递减

CSIHnSOP[6:0]:选择要发送的数据的指针

CSIHnTX0W — CSIH transmit data register 0 for word access

这个寄存器存储传输数据。此外,它还指定了通信中断请求、作业结束、扩展数据长度和芯片选择激活。

CSIHnCIRE:在双缓冲区或仅传输缓冲区模式下启用通信中断请求CSIHTIC,或在FIFO模式下启用作业完成中断CSIHTIJC请求

0:不请求中断。

1:请求中断。传输后产生中断CSIHTIC或CSIHTIJC。

CSIHnEOJ:指定job的结束。

0:表示job不结束。job还在继续。

1:表示job结束数据。

此位仅在启用作业模式时有效(CSIHnCTL1.CSIHnJE = 1)。

从模式下,该位必须设置为0

CSIHnEDL:指定关联数据是否需要扩展数据长度(EDL)选项。

0:正常

1:启用扩展数据长度。

CSIHnSFN[1:0]:将决定插入的虚拟帧的数量,以延长传输数据后的空闲时间

00:传输后不插入虚拟帧。

01:传输后会插入两个虚拟帧(32位)。

10:传输后会插入4个虚拟帧(64位)。

11:8个虚拟帧(128位)在传输后插入

CSIHnISC:空闲状态控制位决定芯片选择信号在传输结束后是否变为非活动状态。

0:传输结束后CS信号输出电平没有变化。

1:传输结束后,CS信号变为非激活状态。

CSIHnCSx(x = 0 to 7):激活一个或多个芯片选择信号。

0:激活芯片选择x进行关联传输。

1:取消激活关联传输的芯片选择x

CSIHnTX[15:0]:存储传输数据。

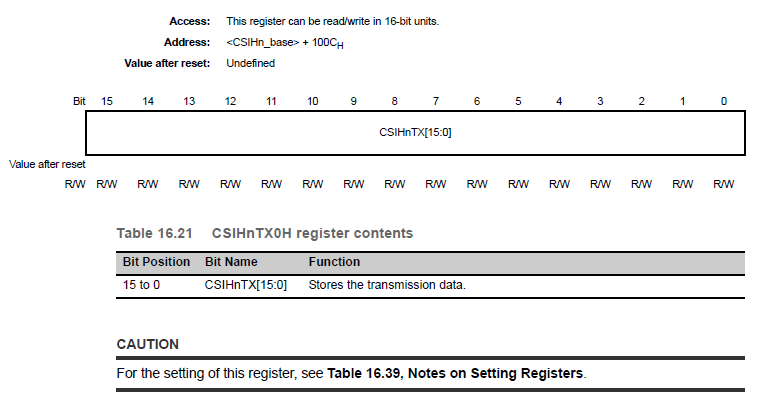

CSIHnTX0H — CSIH transmit data register 0 for half word access

这个寄存器存储传输数据。这个寄存器与寄存器CSIHnTX0W.的15位到0位相同

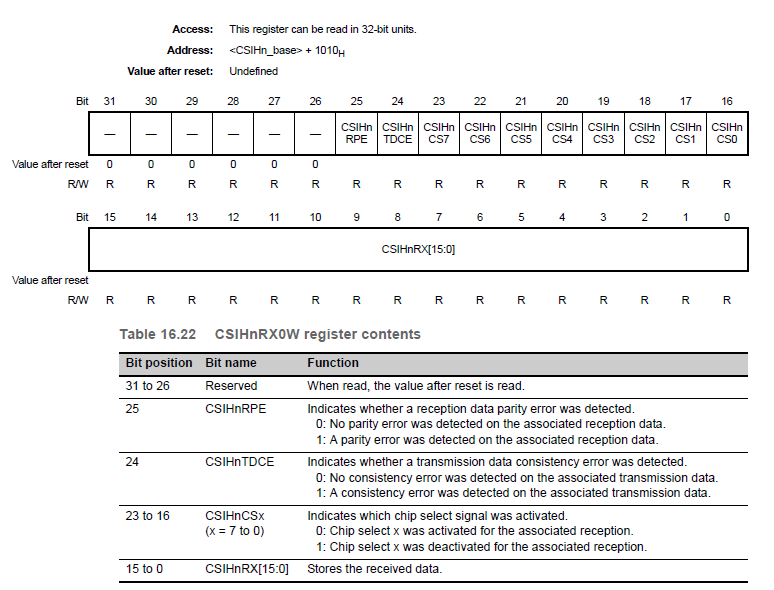

CSIHnRX0W — CSIH receive data register 0 for word access

CSIHnRPE:指示是否检测到接收数据奇偶校验错误。

0:关联接收数据未检测到奇偶校验错误。

1:关联接收数据校验错误。

CSIHnTDCE:是否检测到传输数据一致性错误。1表示检测到

CSIHnCSx(x = 7 to 0):显示哪个芯片选择信号被激活。

CSIHnRX[15:0]:存储接收到的数据

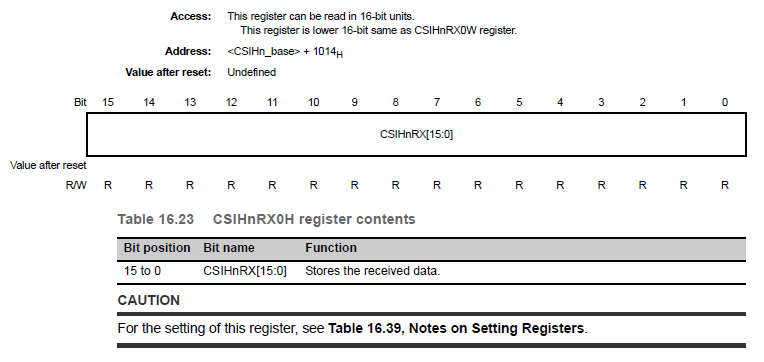

CSIHnRX0H — CSIH receive data register 0 for half word access

这个寄存器存储接收到的数据。这个寄存器与寄存器CSIHnRX0W的15到0位相同

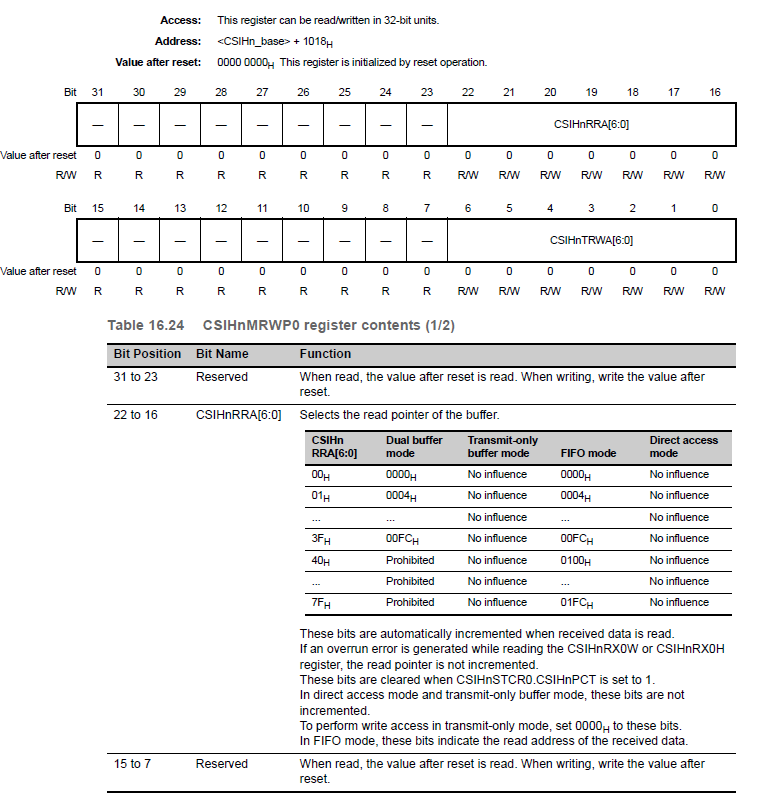

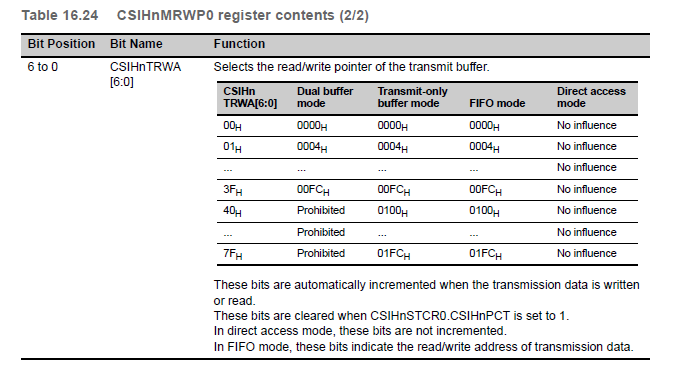

CSIHnMRWP0 — CSIH memory read/write pointer register 0

该寄存器设置从双缓冲区或仅传输缓冲区读取和写入的指针。

CSIHnRRA[6:0]:选择缓冲区的读指针。

CSIHnTRWA[6:0]:选择发送缓冲区的读写指针。

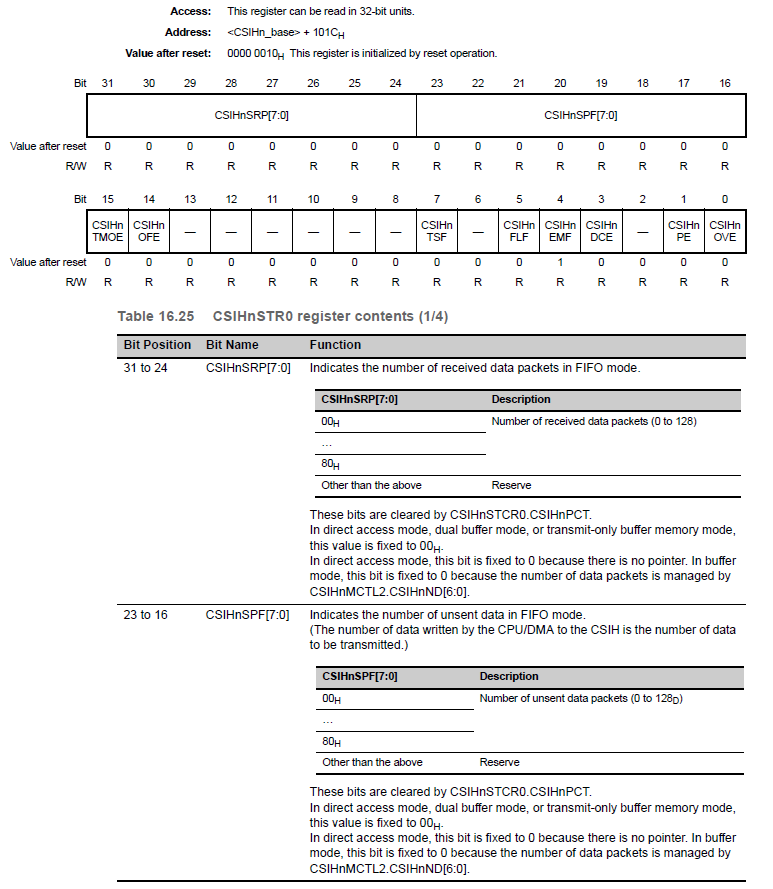

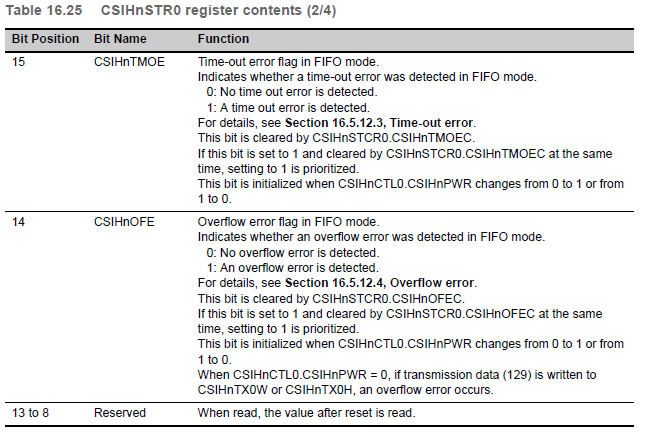

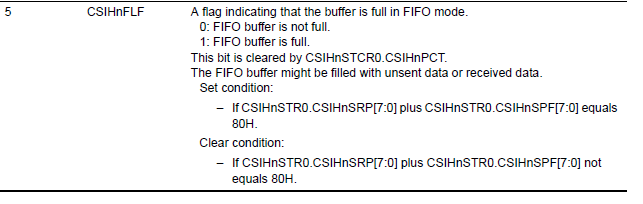

CSIHnSTR0 — CSIH status register 0

该寄存器指示CSIH的状态。

CSIHnSRP[7:0]:反映以FIFO方式接收的数据包数

CSIHnSPF[7:0]:反映FIFO模式下未发送数据的个数。(CPU/DMA写入CSIH的数据数就是要传输的数据数。)

CSIHnTMOE:FIFO模式下的超时错误标志。

指示FIFO模式下是否检测到超时错误。

0:未检测到超时错误。

1:表示检测到超时错误。

CSIHnOFE:FIFO模式溢出错误标志。

指示FIFO模式是否检测到溢出错误。

0:未检测到溢出错误。

1:检测到溢出错误

CSIHnTSF:传输状态标志。

0:空闲状态

1:传输正在进行或准备中

CSIHnFLF:在FIFO模式下表示缓冲区已满的标志。

0: FIFO缓冲区未满。

1: FIFO缓冲区已满。

CSIHnSTCR0.CSIHnPCT清除该位。

CSIHnEMF:在FIFO模式下,缓冲区为空的标志。

0: FIFO缓冲区不为空。

1: FIFO缓冲区为空

该位由CSIHnSTCR0.CSIHnPCT设置为1

CSIHnDCE:数据一致性检查错误标志。

0:未检测到数据一致性错误。

1:检测到数据一致性错误

通过将1写入CSIHnSTCR0.CSIHnDCEC来清除该位。

CSIHnPE:奇偶校验错误标志

0:未检测到校验错误。

1:表示检测到校验错误。

通过将1写入CSIHnSTCR0.CSIHnPEC来清除该位。

CSIHnOVE:溢出错误标志(在双缓冲区模式下固定为0)。

0:未检测到溢出错误。

1:表示检测到溢出错误。

通过将1写入CSIHnSTCR0.CSIHnOVEC来清除该位

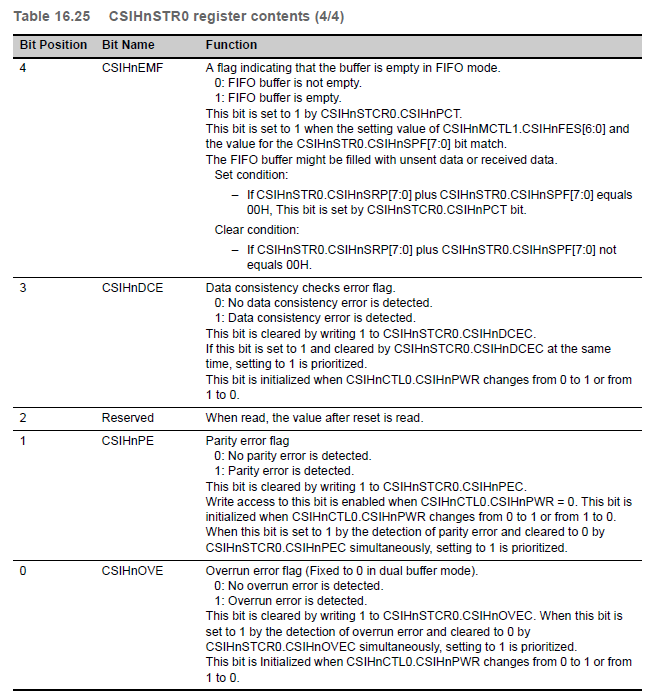

CSIHnSTCR0 — CSIH status clear register 0

该寄存器清除CSIHnSTR0状态寄存器的状态标志

CSIHnTMOEC:控制清除超时错误标志命令。写1清除

CSIHnOFEC:控制溢出错误标志清除命令,写1清除

CSIHnPCT:控制FIFO指针清除命令。写1清除FIFO buffer

CSIHnDCEC:控制数据一致性错误标志清除命令,写1清除

CSIHnPEC:控制奇偶校验错误标志清除命令。写1清除

CSIHnOVEC:控制溢出错误标志清除命令。写1清除

CSIHnMCTL0 — CSIH Memory control register 0

这个寄存器选择内存模式和超时设置

CSIHnMMS[1:0]:选择内存模式,0-FIFO,1-Dual buffer,2-仅发送缓冲模式

CSIHnTO[4:0]:选择FIFO模式下的超时设置

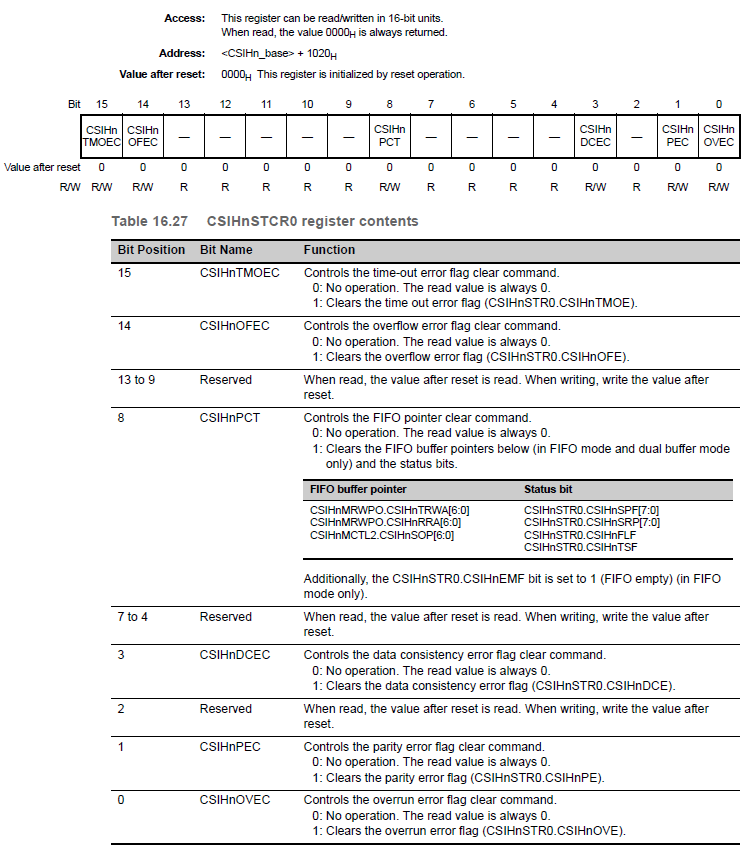

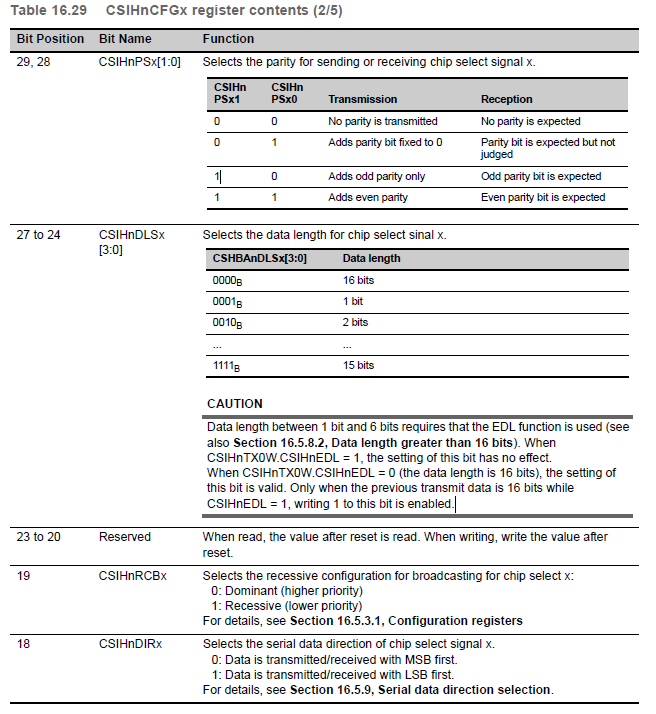

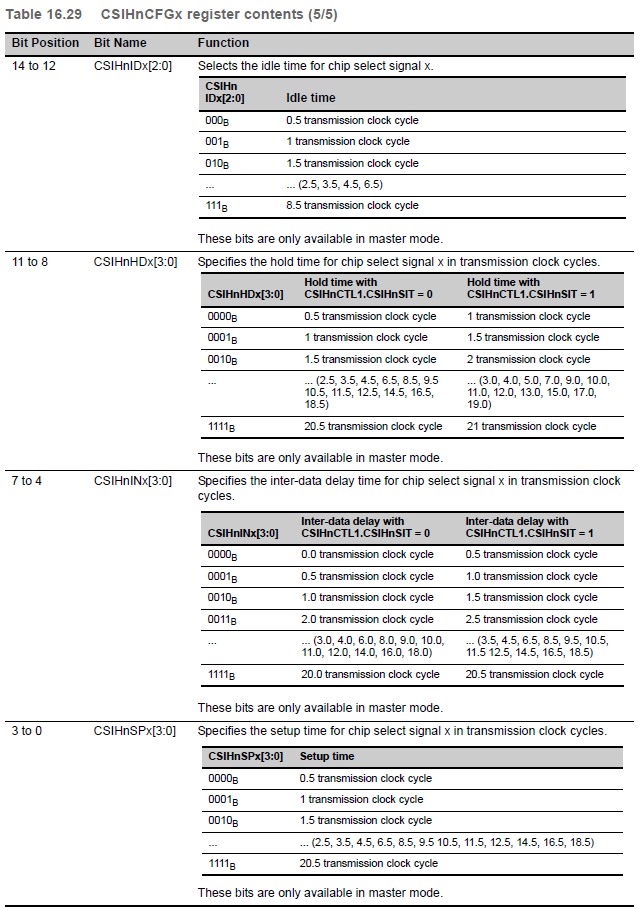

CSIHnCFGx — CSIH Configuration register (x = 0 to 7)

这8个寄存器指定每个芯片选择信号CSIHTCSSx,使用的波特率发生器,奇偶校验,数据长度,广播的隐性配置,串行数据方向,时钟和数据相位,空闲强制配置,空闲时间,保持时间,数据间时间和设置时间

从模式下,CSIHnCFG0寄存器的传输协议设置有效

•CSIHnPS0[1:0]:奇偶校验使用

•CSIHnDLS0[3:0]:数据长度选择

•CSIHnDIR0:数据方向

•CSIHnCKP0, CSIHnDAP0:时钟和数据相位

除上述位之外,其他位都应设置为0,寄存器CSIHnCFG1-7也应全为0

CSIHnBRSSx[1:0]:选择波特率寄存器

CSIHnPSx[1:0]:选择发送或接收芯片选择信号x的奇偶校验。0-无校验,1-校验位为0,2-添加奇校验,3-添加偶校验

CSIHnDLSx[3:0]:为芯片选择信号x选择数据长度。

CSIHnRCBx:为芯片选择x选择广播的隐性配置:

0:优先(优先级更高)

1:隐性(优先级较低)

CSIHnDIRx:选择芯片选择信号x的串行数据方向。LSB/MSB

CSIHnCKR=0时,时钟默认电平为高电平,为1时为低电平

CSIHnSLRS=0时,使用标准采样点,为1时使用采样点偏移,波特率超过5M时必须选择为1

CSIHnCKPx为0,表示CSIHnSCK初始电平为CSIHnCKR设置的电平,为1时翻转

CSIHnDAPx为0表示数据捕获在时钟后边沿,为1表示在前边沿

后边沿可以这么理解:当时钟默认电平为高电平时,后边沿就是上升沿,当时钟默认电平为低电平时,后边沿是下降沿

CSIHnCTL1.CSIHnCKR = 1时,禁止设置CSIHnCKPx=1

当CSIHnSLRS = 1时,使用采样点偏移,实际就是偏移半个时钟周期,数据捕获再取反一下即可,原先后边沿捕获的,变成前边沿捕获

CSIHnIDLx:为chip select x选择空闲强制配置:

0:如果CSIHnTX0W.CSIHnCSx两次连续传输的设置是不同的,两次传输之间所有的CSIHTCSS0到7都是一次取消激活。如果CSIHnTX0W.CSIHnCSx连续两次传输的设置相同,两次传输之间没有不活动时间

1:不管CSIHnTX0W.CSIHnCSx设置的两次连续传输,所有的CSIHTCSS0到7之间的两次传输都是一次停用。

此位仅在主模式下可用。

当CSIHnCTL1.CSIHnJE = 1和CSIHnTX0W.CSIHnEOJ = 1,即使CSIHnCFG0 ~ 7.CSIHnIDLx = 0,空闲状态肯定插入。

CSIHnIDx[2:0]:选择芯片选择信号x的空闲时间。

CSIHnHDx[3:0]:指定芯片选择信号x在传输时钟周期中的保持时间。

CSIHnINx[3:0]:指定芯片选择信号x在传输时钟周期中的数据间延迟时间。

CSIHnSPx[3:0]:指定在传输时钟周期中芯片选择信号x的设置时间。

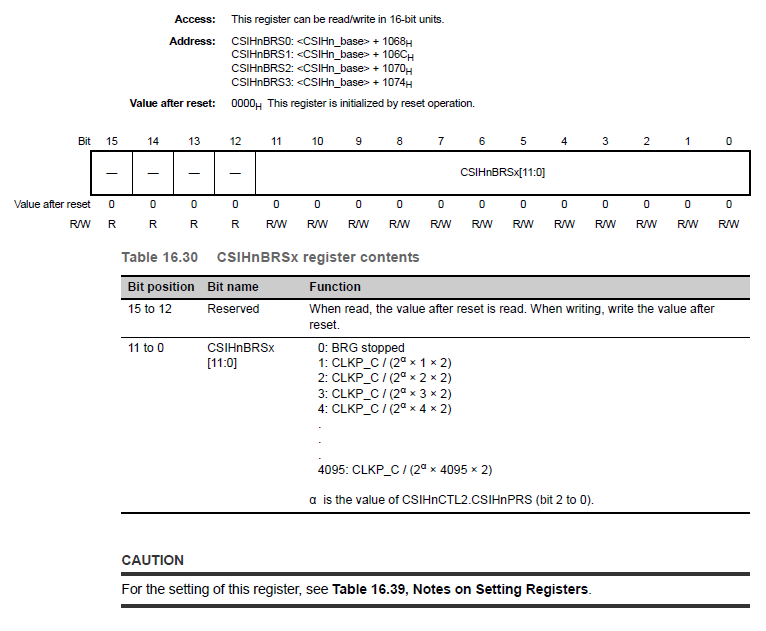

CSIHnBRSx — CSIH baud rate setting register (x = 0 to 3)

这个寄存器设置每个芯片选择信号的波特率。

CSIHnCFGx.CSIHnBRSSx[1:0]位,四种波特率设置中的一种可以为每个芯片选择信号。(x = 0 ~ 7)

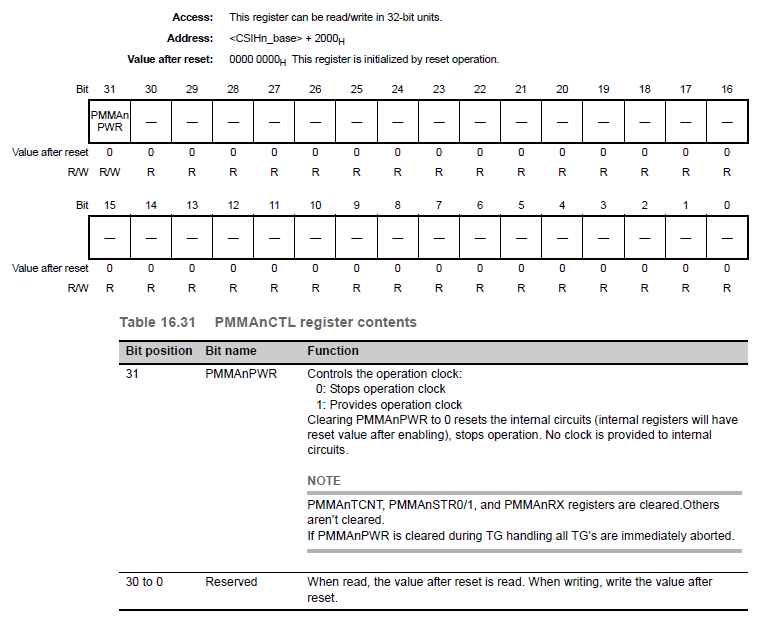

PMMAnCTL — PMM control register

这个寄存器控制操作时钟。

PMMAnPWR:控制操作时钟:

0:停止运行时钟

1:提供操作时钟

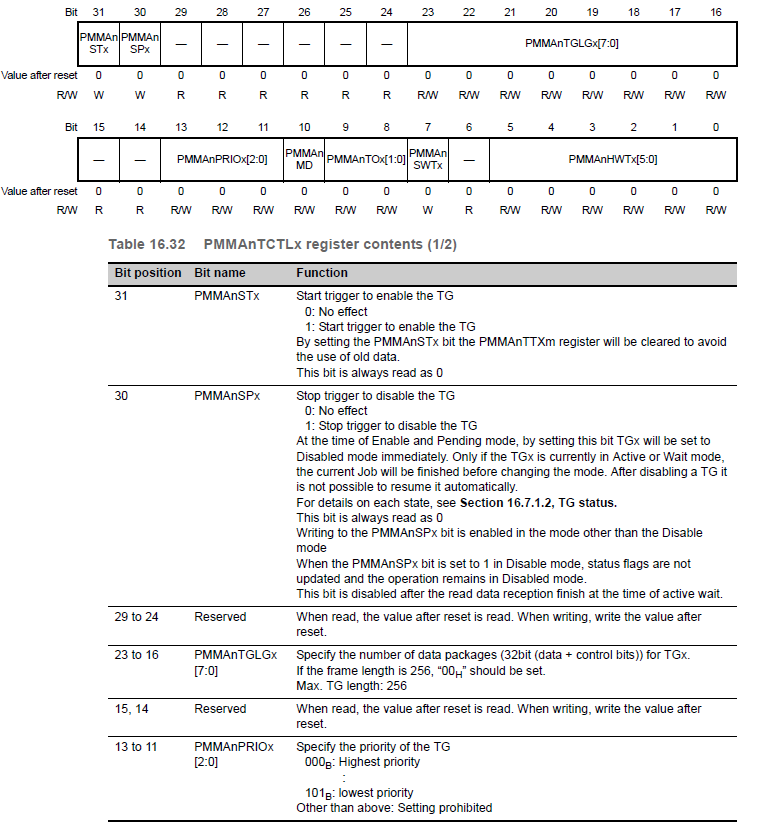

PMMAnTCTLx — PMM TG control register (x = 0 to 7)

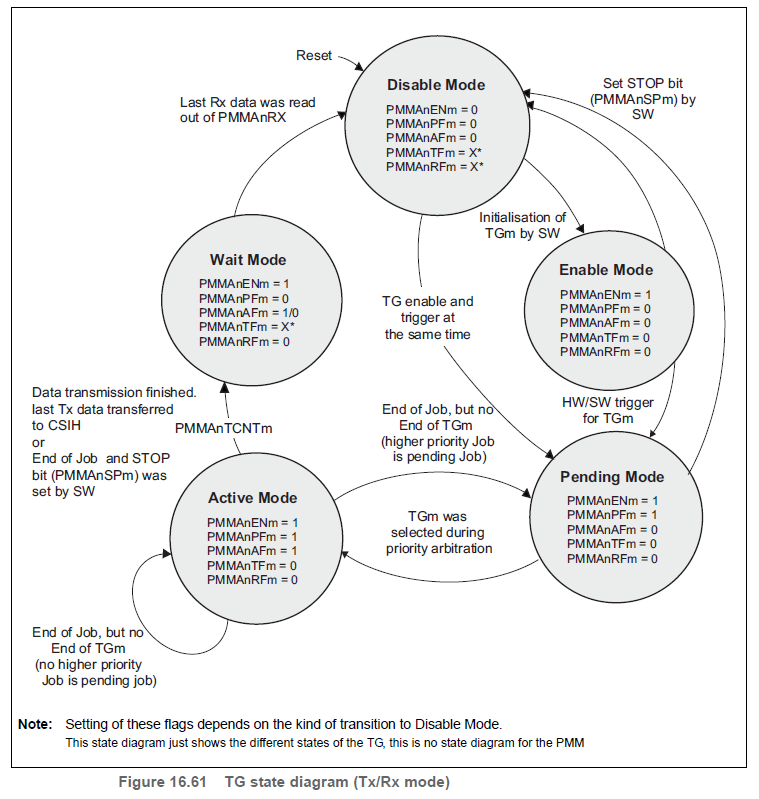

该寄存器控制优先级管理模块的操作

PMMAnSTx:启动触发器使能TG

0:没有影响

1:启动触发器,使能TG

通过设置PMMAnSTx位,PMMAnTTXm寄存器将被清除,以避免使用旧数据。

PMMAnSPx:停止触发器,关闭TG

0:没有影响

1:停止触发器,关闭TG

PMMAnTGLGx[7:0]:指定TGx的数据包数量(32位(数据+控制位))。

如果帧长为256,则应设置“00H”。

Max.TG长度:256

PMMAnPRIOx[2:0]:指定TG的优先级

000B:最高优先级

:

101B:最低优先级

PMMAnMD:指定传输模式

0:仅传输模式(Tx)

1:收发模式(Tx/Rx)

PMMAnTOx[1:0]:指定触发器选项

00B:触发不启用

01B:软件触发

10B:硬件触发

11B:硬件和软件触发

PMMAnSWTx:软件触发设置TGx为挂起模式

该位在启用模式下有效。当在Disable模式下,将1同时写入PMMAnST位和该位时,该位也是有效的。

PMMAnHWTx[5:0]:选择硬件触发源

将100011或更多的号设置为PMMAnTCTL.PMMAnHWTm[5:0]禁止使用。

注意:1. 只有当TG处于禁用模式时,才允许写入PMMAnTCTLx寄存器中的PMMAnSPx和PMMAnSWTx位以外的其他位。

2. 当TG在Disable模式时,PMMAnSTx和PMMAnSWTx位同时被设置为1,切换到Pending模式。

3.如果同时写入PMMAnSTx和PMMAnSPx,则忽略PMMAnSTx位,因为PMMAnSPx位具有高优先级

PMMAnTTXm — PMM TG transmit buffer (x = 0 to 7)

发送缓存区

传输路径的TGx数据缓冲区

PMMAnRX — PMM TG receive buffer

接收缓存区

接收路径的数据缓冲区

在仅传输模式下,数据不存储在PMMAnRX寄存器中

PMMAnTCNTx — PMM TGx counter (x = 0 to 7)

这个寄存器是计数器,它指示剩余的数据传输到TGx的PMMA。

计数器,显示剩余的数据传输到PMMA为TGx

将加载PMMAnTGLGx[7:0]的值,当PMMAnCTLx.PMMAnSTx设置位。

每次数据被转发到CSIHnTX0W寄存器时,该寄存器的值-1。

PMMAnSTR0 — PMM TG status register 0

这个寄存器显示TG的状态

PMMAnENx:表示模式已启用或禁用

0:关闭TGx功能

1:开启TGx功能

PMMAnAFx:显示TGx是否被设置为激活状态

0:表示TGx状态不是active。

1:设置TGx为active状态

PMMAnPFx:指示TGm是否设置为status pending

0:表示TGx不是pending状态

1:设置TGx为status pending。

PMMAnSTR1 — PMM TG status register 1

这个寄存器表示TG的发送/接收状态

PMMAnRFx:TGx的接收路径状态

0:不是所有的数据都被TGx接收。

1: PMM对TGx的接收处理已经完成

PMMAnTFx:显示TGx的发送路径状态

0:不是所有的数据都以TGx传输。

1: PMM对TGx的传输处理已经完成

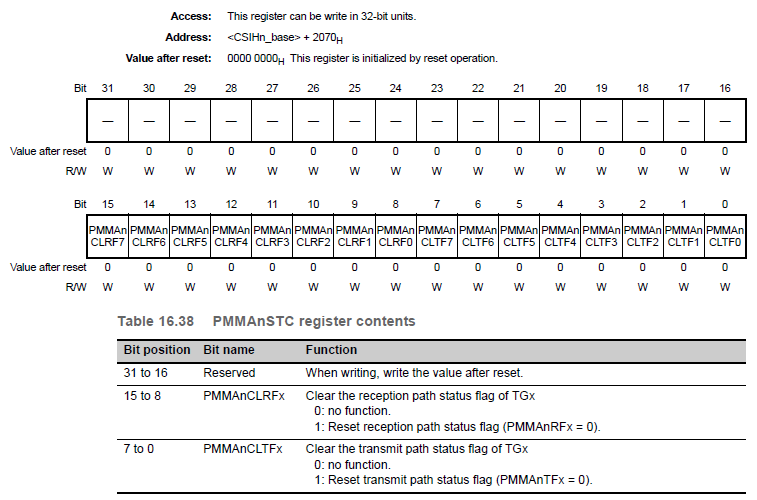

PMMAnSTC — PMM TG status clear register

这个寄存器清除TG的发送/接收状态

写1清除

Interrupt Sources

CSIH可以生成以下中断请求:

•CSIHTIC(通信中断)

•CSIHTIR(通信中断)

•CSIHTIRE(错误中断)

CSIHTIJC(job完成中断)

Overview

当检测到错误时,会生成错误中断CSIHTIRE。其他中断的产生取决于内存模式、作业模式,在作业完成中断CSIHTIJC的情况下,还取决于操作模式

作业完成中断CSIHTIJC仅在启用作业模式时生成(CSIHnCTL1.CSIHnJE = 1).

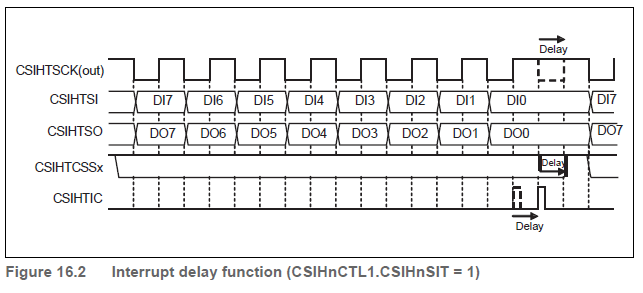

General interrupt delay

在主模式下,所有由主模式产生的中断都可以延迟半个传输时钟周期CSIHTSCK。

延时由设置位CSIHnCTL1.CSIHnSIT = 1.指定

下面的例子说明了中断延迟函数,假设设置为:

CSIHnCTL1.CSIHnSIT = 1(中断延迟启用)

CSIHnCFGx.CSIHnCKPx = 0,CSIHnCFGx.CSIHnDAPx = 0(标准时钟和数据相位),

CSIHnCFGx.CSIHnDLSx[3:0] = 1000B(数据长度8位)。

中断延迟半个时钟周期产生

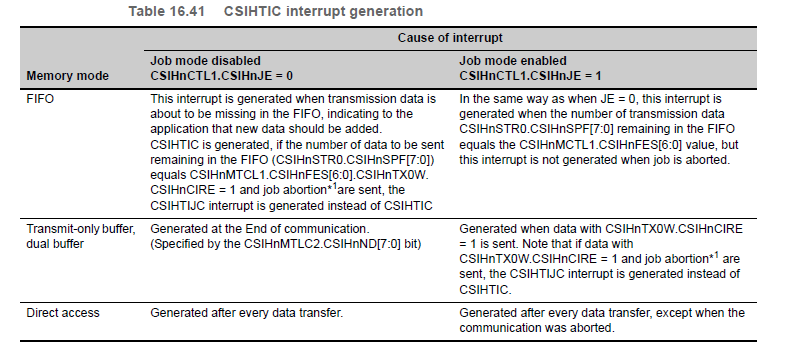

CSIHTIC (communication interrupt)

根据内存模式和作业模式的不同,这个中断是根据下表所示的条件产生的

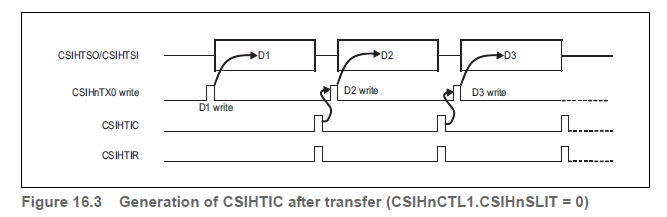

CSIHTIC in direct access mode

下面的示例显示了直接访问模式下的CSIHTIC行为。

这些例子假设:

•主模式

•直接访问模式

•无一般中断延迟(CSIHnCTL1.CSIHnSIT = 0)

•标准时钟和数据相位(CSIHnCFGx.CSIHnCKPx = 0, CSIHnCFGx.CSIHnDAPx = 0)

•数据长度8位(CSIHnCFGx.CSIHnDLSx[3:0] = 1000B)

•正常CSIHTIC中断时间(CSIHnCTL1.CSIHnSLIT = 0)

如果启用了作业模式(CSIHnCTL1.CSIHnJE = 1),作业结束,因为数据被发送到

CSIHnT0W.CSIHnEOJ = 1,请求通信停止(CSIHnCTL0.CSIHnJOBE = 1),则CSIHTIC被作业完成中断CSIHTIJC取代。

还可以将CSIHTIC设置为在CSIHnTX0寄存器空闲时发生下一个数据。这可以通过设置CSIHnCTL1.CSIHnSLIT = 1来指定。

CSIHTIC in FIFO mode

下面的例子显示了FIFO模式下的CSIHTIC行为

这个例子假设:

•主模式

•FIFO模式

•无一般中断延迟(CSIHnCTL1.CSIHnSIT = 0)

•标准时钟和数据相位(CSIHnCFGx.CSIHnCKPx = 0, CSIHnCFGx.CSIHnDAPx = 0)

•数据长度8位(CSIHnCFGx.CSIHnDLSx[3:0] = 1000B)

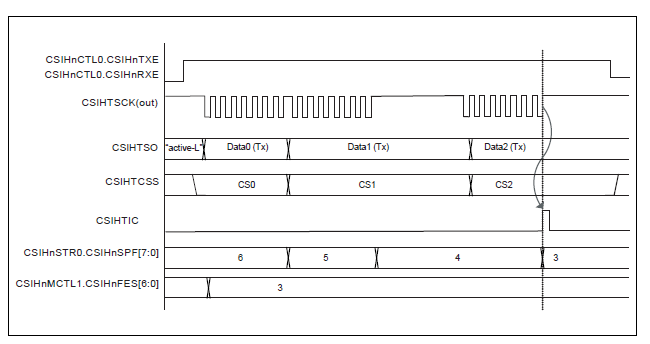

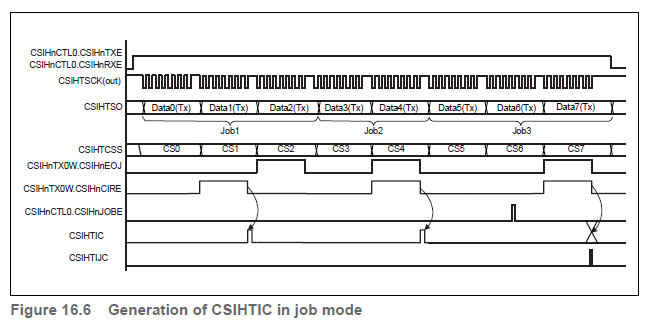

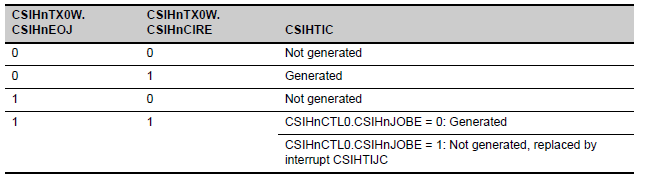

CSIHTIC in job mode

下面的示例显示了作业模式下的CSIHTIC行为。

这个例子假设:

•主模式

•启用作业模式(CSIHnCTL1.CSIHnJE = 1)

•无一般中断延迟(CSIHnCTL1.CSIHnSIT = 0)

•标准时钟和数据相位(CSIHnCFGx.CSIHnCKPx = 0, CSIHnCFGx.CSIHnDAPx = 0)

•数据长度8位(CSIHnCFGx.CSIHnDLSx[3:0] = 1000B)

•正常CSIHTIC中断时间(CSIHnCTL1.CSIHnSLIT = 0)

在作业模式下生成CSIHTIC的规则如下表所示

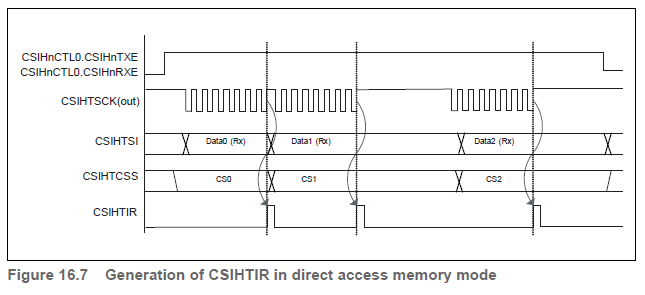

CSIHTIR in direct access mode

下面的示例显示了直接访问模式下的CSIHTIR行为。

这些例子假设:

•主模式

•直接访问模式

•无一般中断延迟(CSIHnCTL1.CSIHnSIT = 0)

•标准时钟和数据相位(CSIHnCFGx.CSIHnCKPx = 0, CSIHnCFGx.CSIHnDAPx = 0)

•数据长度8位(CSIHnCFGx.CSIHnDLSx[3:0] = 1000B)

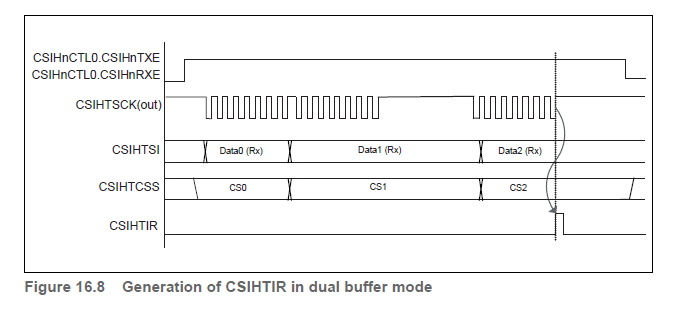

CSIHTIR in dual buffer mode

下面的示例显示了双缓冲区模式下的CSIHTIR行为。

这个例子假设:

•主模式

•双缓冲模式

•无一般中断延迟(CSIHnCTL1.CSIHnSIT = 0)

•标准时钟和数据相位(CSIHnCFGx.CSIHnCKPx = 0, CSIHnCFGx.CSIHnDAPx = 0)

•数据长度8位(CSIHnCFGx.CSIHnDLSx[3:0] = 1000B)

CSIHTIRE (reception error interrupt)

错误中断包括:

FIFO overflow error-FIFO溢出错误

Parity error-校验错误

Data consistency error-数据一致性错误

Time-out error-超时错误

Overrun error-溢出错误

导致生成CSIHTIRE的错误类型在寄存器CSIHnSTR0中被标记。

另外,奇偶错误标志和数据一致性错误标志附加到中的接收数据CSIHnRX0W。

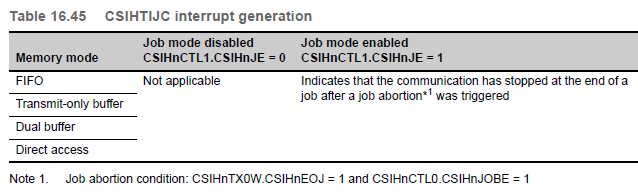

CSIHTIJC (job completion interrupt)

CSIHnCTL1.CSIHnJE = 1时使能job mode,当CSIHnCTL1.CSIHnJE = 0时,CSIHTIJC不会生成

根据内存模式的不同,这个中断是根据下表所示的条件产生的

Operation

Master/slave connections

可以通过片选控制多个从机

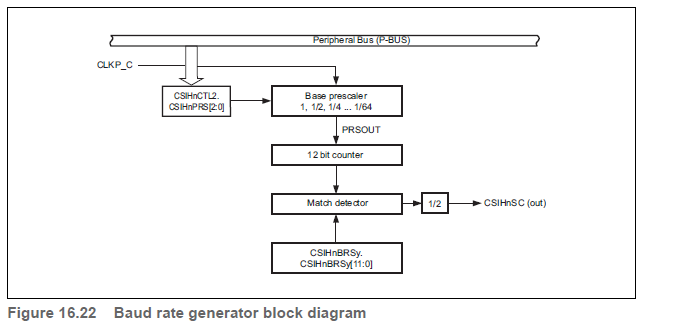

Transmission clock selection

在主模式下,传输波特率可通过以下位数选择:

• CSIHnCTL2.CSIHnPRS[2:0]

• CSIHnBRSy.CSIHnBRSy[11:0] (y = 0 to 3)

• CSIHnCFGx.CSIHnBRSSx[1:0] (x = 0 to 7)

而CSIHnCTL2寄存器中的设置决定传输时钟CSIHTCLK,一个芯片选择专用的预分频器,由CSIHnCFGx控制。CSIHnPSCLx[1:0],允许为不同的芯片选择产生不同的波特率。

当CSIHnBRSy.CSIHnBRSy[11:0]被清除时,时钟停止

波特率计算公式为:

CSIHTSCK = CLKP_C / (2^α × k × 2)

Operating Procedures

下面的示例和过程按照存储方式的顺序描述如下:

•直接访问模式

•仅传输缓冲模式

•双缓冲模式

•FIFO模式

Procedures in direct access mode

提供了两个用于主机的示例,一个禁用了作业模式,另一个启用了作业模式。

Transmit/receive in master mode when job mode is disabled

以下程序是基于以下假设:

•传输数据长度为8位(CSIHnCFGx.CSIHnDLSx[3:0] = 1000B).

•传输方向为MSB优先(CSIHnCFGx.CSIHnDIRx = 0).

•标准时钟和数据相位(CSIHnCFGx.CSIHnCKPx = 0, CSIHnCFGx.CSIHnDAPx = 0)

•无一般中断延迟(CSIHnCTL1.CSIHnSIT = 0)

•未启用作业模式(CSIHnCTL1.CSIHnJE = 0).

•正常CSIHTIC中断时间(CSIHnCTL1.CSIHnSLIT = 0)

•直接访问模式(CSIHnCTL0.CSIHnMBS = 1)

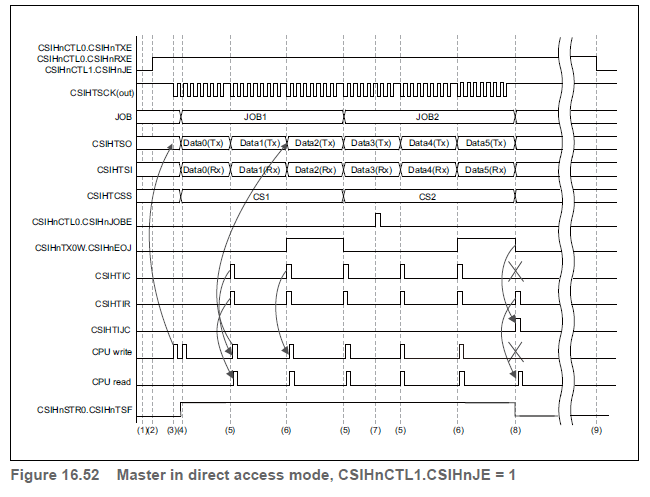

Transmit/receive in master mode when job mode is enabled

以下程序是基于以下假设:

•传输数据长度为8位(CSIHnCFGx.CSIHnDLSx[3:0] = 1000B).

•传输方向为MSB优先(CSIHnCFGx.CSIHnDIRx = 0).

•标准时钟和数据相位(CSIHnCFGx.CSIHnCKPx = 0, CSIHnCFGx.CSIHnDAPx = 0)

•无一般中断延迟(CSIHnCTL1.CSIHnSIT = 0)

•启用作业模式(CSIHnCTL1.CSIHnJE = 1).

•正常CSIHTIC中断时间(CSIHnCTL1.CSIHnSLIT = 0)

•直接访问模式(CSIHnCTL0.CSIHnMBS = 1)

•两个作业,每个作业发送三个数据包

Job完成后会设置CSIHnTX0W.CSIHnEOJ = 1

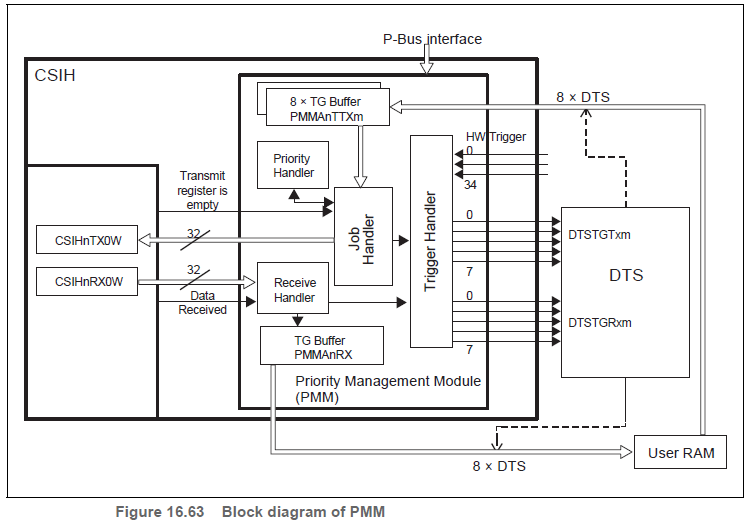

Priority Management Module (PMM)

CSIH优先级管理模块(PMM)是带有传输组的CSIH模块的附加模块&优先处理能力。PMM将处理多达8个TG,具有6个可配置的优先级。每个TG将能够产生两个DTS触发器,可用于从本地或全局RAM加载传输数据,并将接收数据存储到本地或全局RAM中。(DTS配置必须在软件中完成)。PMM将使不同的应用程序能够同时使用相同的CSIH,而无需任何软件同步。

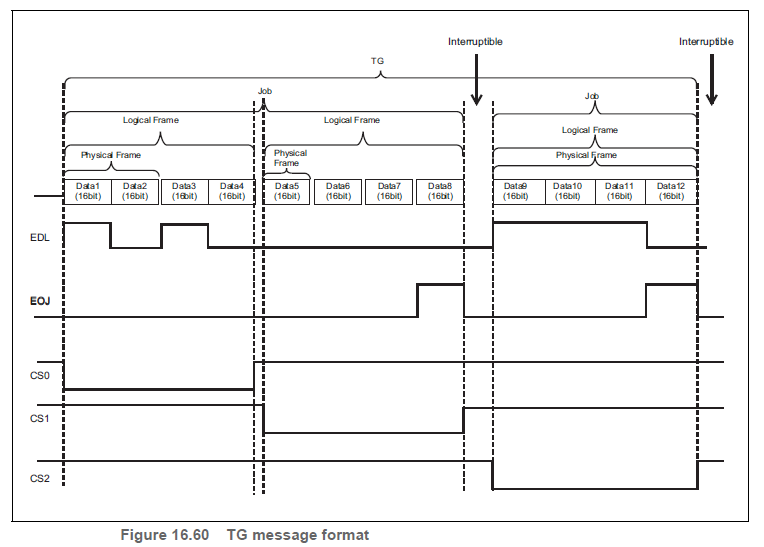

Transfer groups

CSIH通信将由传输组(TG)处理。

每种TG具有以下属性:

•配置了一个或多个作业

•可设置6个优先级

•DTS触发器专用于接收路径和发送路径使用。

-即使在另一个传输组(TG)正在传输时也可以更改

-可以在不影响其他传输组(TG)的情况下进行更改

-可以由具有更高优先级的传输组(TG)在作业之间暂停

—三种类型的触发器

硬件触发

软件触发

硬件和软件触发器

TG structure

Block Diagram

框图显示了PMM的主要组件。

Functional Overview

•每个CSIH实例一个PMM

•支持多达8个传输组,每个组有六个可配置的优先级级别

•三个中断请求信号

- PMMTIC:数据传输到TG的CSIH完成

- PMMRIC: CSIH和PMM的数据接收完成(Tx/Rx模式)。

数据传输完成(仅Tx模式)。 - PMMTIJC: TG被PMMAnSPm bit终止。

每个TG都具有以下功能

•产生DTS触发信号的接收和发射路径

•软件和硬件触发TG转移的启动

•可选择的硬件触发源从多个输入信号

•开启/关闭TG

•支持TG长度达256 × 32bit(数据+控制位)

•支持CSIH的EDL功能

•可配置的作业长度由EOJ位在Tx数据的控制位