数字IC设计、验证、FPGA笔试必会 - Verilog经典习题 (二)异步复位的串联T触发器

🔈声明:

😃博主主页:王_嘻嘻的CSDN博客

🧨未经作者允许,禁止转载

🔑系列专栏:牛客Verilog习题集

🚩推荐一个IC、FPGA新手入门的好网站:👉快 点 击 进 入 学 习 吧

前言:应朋友之约,从今天开始一个新的专栏Verilog习题集,将整理牛客网经典Verilog习题讲解,牛客网里除了最新的Verilog题库还有其它领域的经典笔试、面试题,大家快和我一起刷起来吧 点 击 跳 转

题目

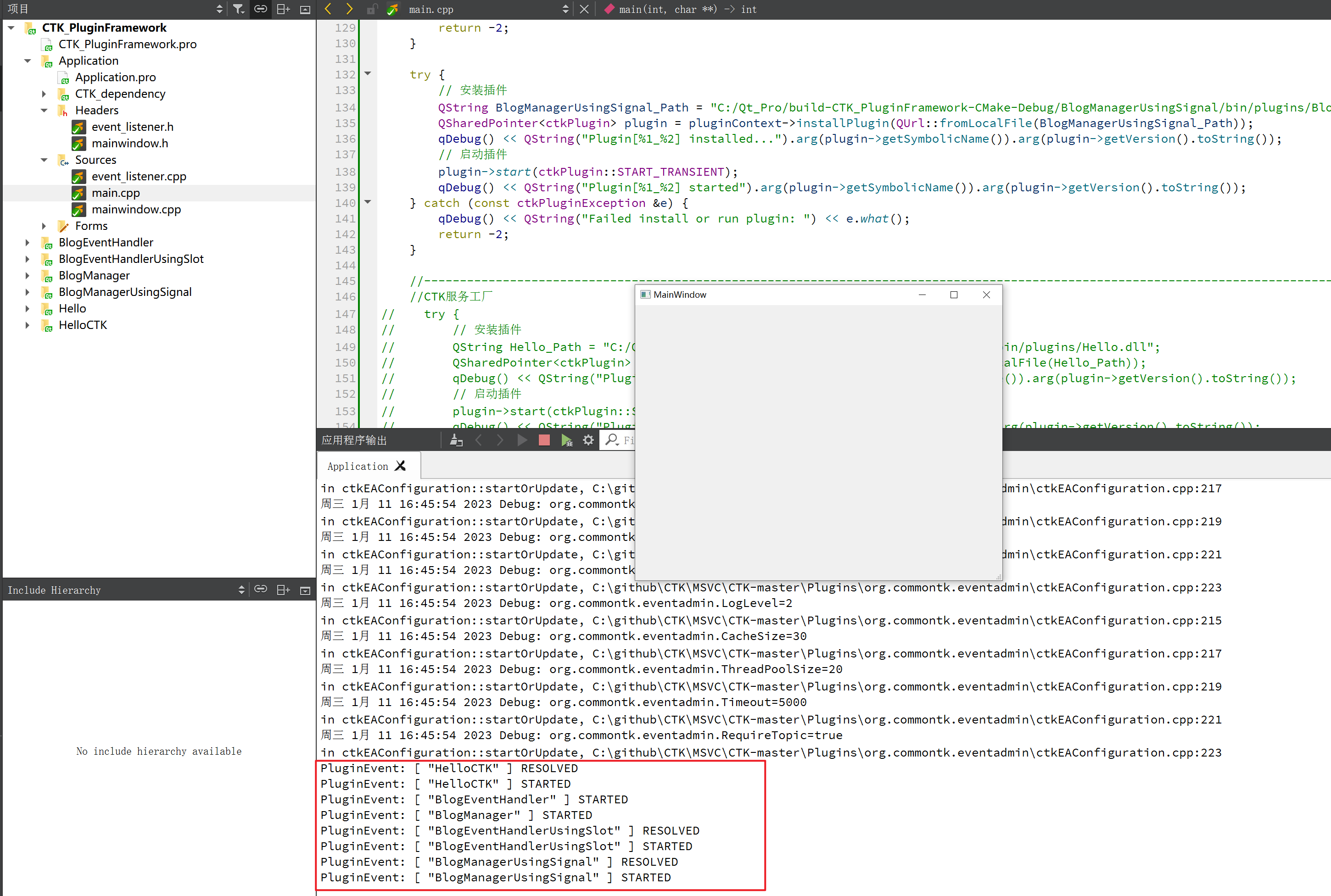

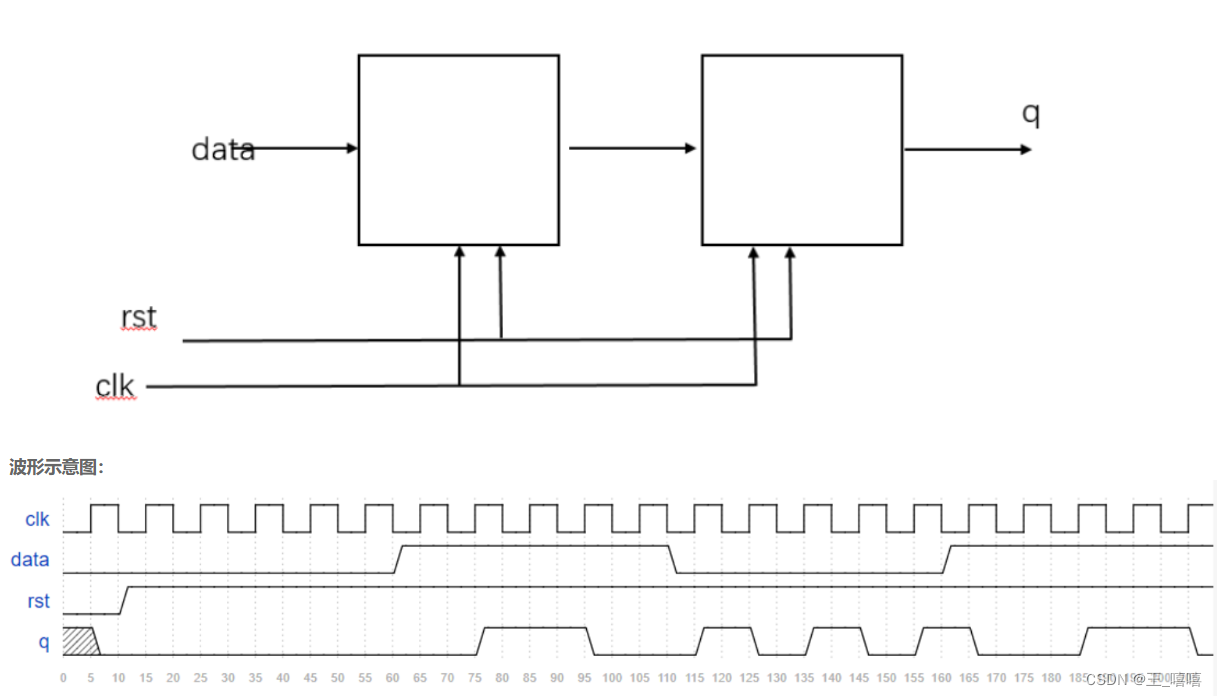

用Verilog实现两个串联的异步复位的T触发器的逻辑,结构如图:

分析:

题目要求完成异步复位的T触发器,T触发器本质就是

- 输入为’0‘时,输出保持;

- 输入为’1‘时,输出翻转;

而题目要求的是两个TFF串联,所以只需要会写TFF的翻转逻辑,再级联即可。异步复位只需要在每个触发器上使用异步复位端口rst,这个端口是触发器器件自带的。

此处需要注意的是,所有的触发器,不论是DFF或者TFF都是时序逻辑,组合逻辑是实现不了保持这个行为的!

题解:

`timescale 1ns/1ns

module Tff_2 (

input wire data, clk, rst,

output reg q

);

reg data_tmp;

always @ ( posedge clk or negedge rst)begin //TFF0

if(~rst)

data_tmp <= 1'b0;

else

if(data)

data_tmp <= !data_tmp;

end

always @ ( posedge clk or negedge rst)begin //TFF1

if(~rst)

q <= 1'b0;

else

if(data_tmp)

q <= !q;

end

endmodule

在写这段Verilog时,很多同学很将两个触发器逻辑写在一个always块中,其实两个触发器输出并没有共同点。

博主建议大家可以将逻辑相同的触发器写在一个always块内,否则还是尽可能分开完成。