文章目录

- 摘要

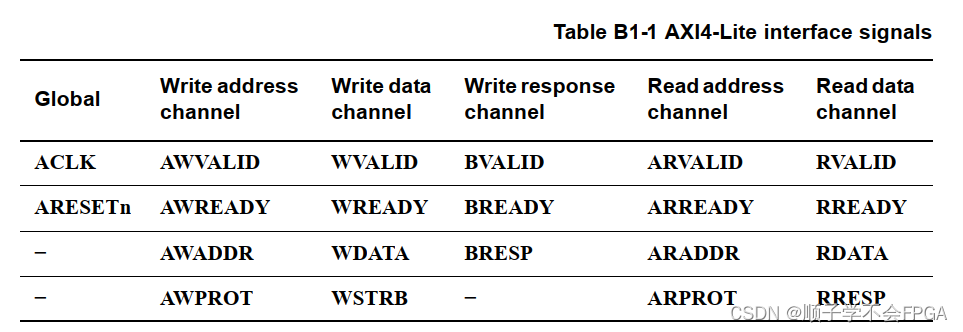

- 一、AXI_Lite接口

- 全局信号:

- 1、写地址通道:

- 2、写数据通道:

- 3、写响应通道:

- 4、读地址通道:

- 5、读数据通道:

- 二、仿真波形

摘要

AXI4-lite是AXI4-full的简化版。用于简单、低吞吐量的内存映射通信。主要用于内核和外设寄存器之间的通信。比如当访问串口的数据寄存器时,只访问四个字节的数据,所以使用AXI4-lite就特别合适。再比如,在PL写一个用于PS端操作的外设时,其外设寄存器一般通过AXI4-lite总线和PS交互。

AXI4-lite总线协议的特性如下:

- 数据总线只能是32位或者64位。

- 每次传输只能传输一个数据。

- 所有访问都是不可修改(Non-modifiable),不可缓冲(Non-bufferable)。

- Exclusive 访问不支持,即独占访问不支持

一、AXI_Lite接口

全局信号:

ACLK :全局时钟信号,所有输入信号均在ACLK上升沿采样,所有输出信号的更改只能在ACLK上升沿之后。主从接口上的所有输入和输出信号间不允许有组合路径,同AXI4

ARESETn :全局复位信号,为异步复位同步置位信号,即ARESETn在任意时刻变为低电平可立刻生效,但置位为1时只能在ACLK的下一个上升沿生效,同AXI4

1、写地址通道:

AWID :(可选,仅但主机是AXI4而从机是AXI-Lite时需要此信号) ,当需要和主机的AXI4协议互联时,从机的AXI-Lite协议增加此信号

AWADDR :协议未定义位宽, Xilinx使用12, 13, … 64,一般为32/64 ,要写入数据的内存地址,同AXI4

AWPORT :写事务的保护属性:特权,安全级别和访问类型,提供用于禁止非法传输事务的访问权限信号,同AXI4,xilinx建议赋值为3’b000.xilinx IP 一般忽略此信号。

AWVALID、AWREADY :握手信号

附:AWPORT信号详解 :

参考:https://blog.csdn.net/weixin_42837669/article/details/107727283

AxPORT共3位,每一位的值代表不同的意义。一般可设置为3‘b000,表示非特权且安全的数据访问。

[0] 0 Unprivileged access 非特权访问 AXI主站可能支持多个级别的操作特权,并将这种特权概念扩展到内存访问。 AxPROT [0]将访问标识为非特权或特权

[0] 1 Privileged access 特权访问

[1] 0 Secure access 安全访问 AXI主站可能支持安全和非安全操作状态,并将这种安全性概念扩展到内存访问。 AxPROT [1]将访问标识为安全或不安全。 AxPROT [1]可以视为定义了两个地址空间,一个安全地址空间和一个非安全地址空间。该信号可被视为附加地址位。安全和非安全地址空间之间的任何别名都必须正确处理。

[1] 1 Non-secure access 非安全访问 -

[2] 0 Data access 数据访问 该位指示事务是指令访问还是数据访问。 AXI协议将此指示定义为提示。并非在所有情况下都是准确的,例如,当事务包含指令和数据项的混合时。本规范建议主机将AxPROT [2]设置为LOW,以指示数据访问,除非已知该访问是指令访问。

[2] 1 Instruction access 指令访问

2、写数据通道:

WDATA :数据信号线,传输数据信息。

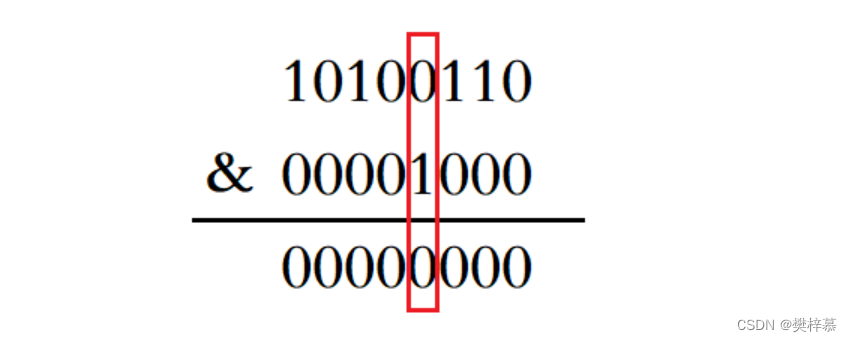

WSTRB :数据总线有效字节控制。比如32位的总线,WSTRB等于4’b0010,那么代表WDATA[15:8]中的数据有效。其他无效。如果要求WDATA[31:0]32位全有效,那么WSTRB就应该等于4’b1111.

ARVALID、ARREADY :握手信号

3、写响应通道:

BREADY、BVALID:握手信号

BRESP :应答类型。AXI4-lite不支持EXOKAY类型的响应。

OKEY 0 正常访问成功

SLVERR 2 从机错误

DECERR 3 解码错误,比如没有从机的地址。

4、读地址通道:

ARVALID、ARREADY:握手信号

ARADDR 地址信号线,传输地址信息。

ARPROT 访问权限信号线,xilinx建议赋值为3’b000.xilinx IP 一般忽略此信号。

5、读数据通道:

RREADY、RVALID:握手信号

RDATA : 数据信号线,传输数据信息。

RRESP :同写应答信号BRESP。

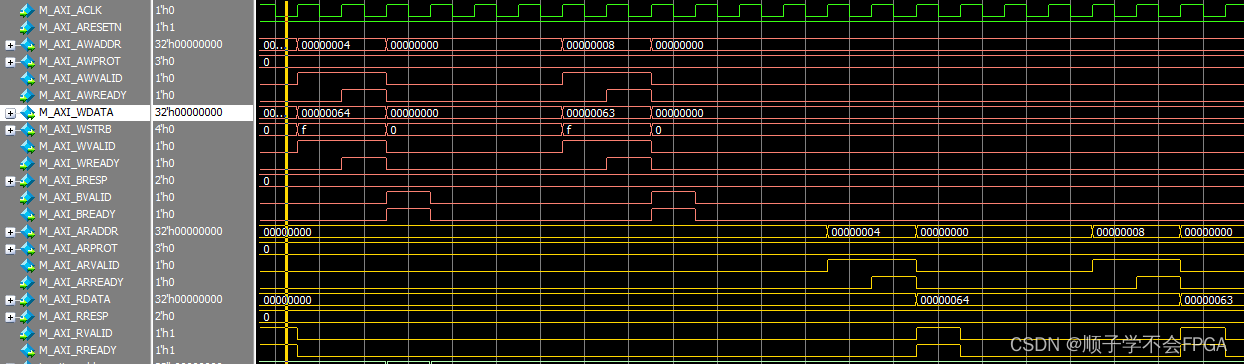

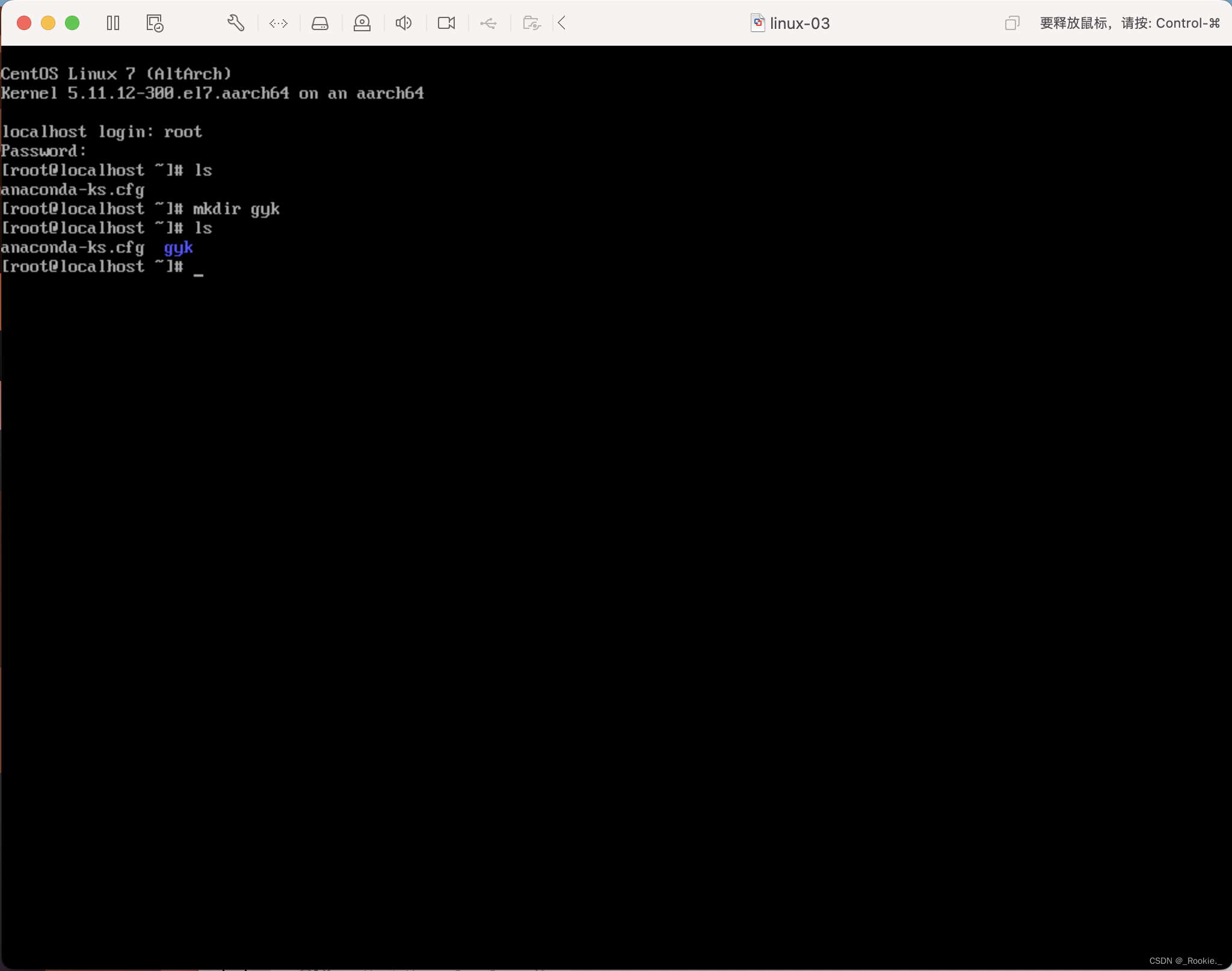

二、仿真波形

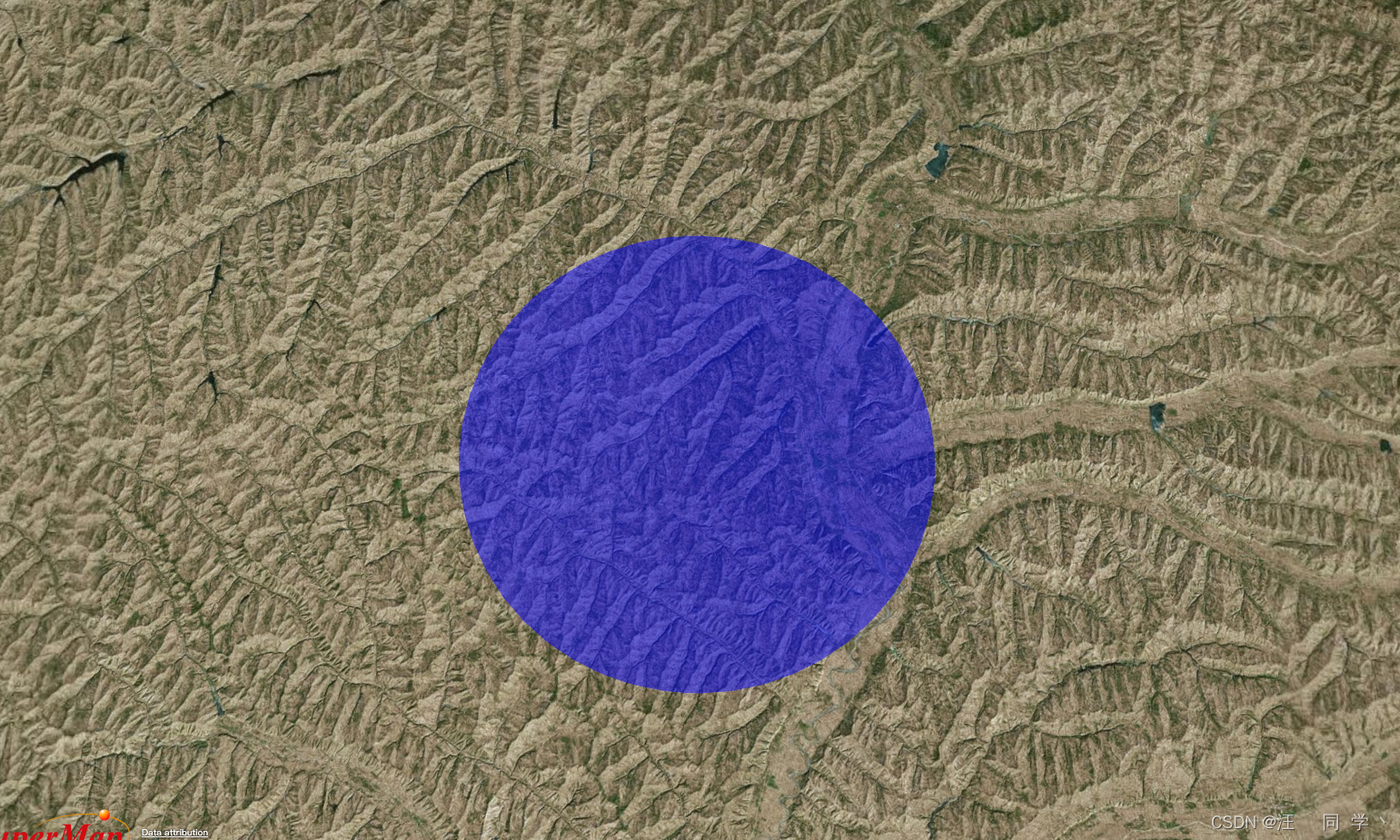

粉色为写地址、写数据、写响应通道,写入俩次数据。

黄色为读地址、读数据通道,读出俩次数据,与写入数据一致

![YOLOv9代码解读[01] readme解读](https://img-blog.csdnimg.cn/direct/63ab14e4139c44c998d0376036c52be7.png)