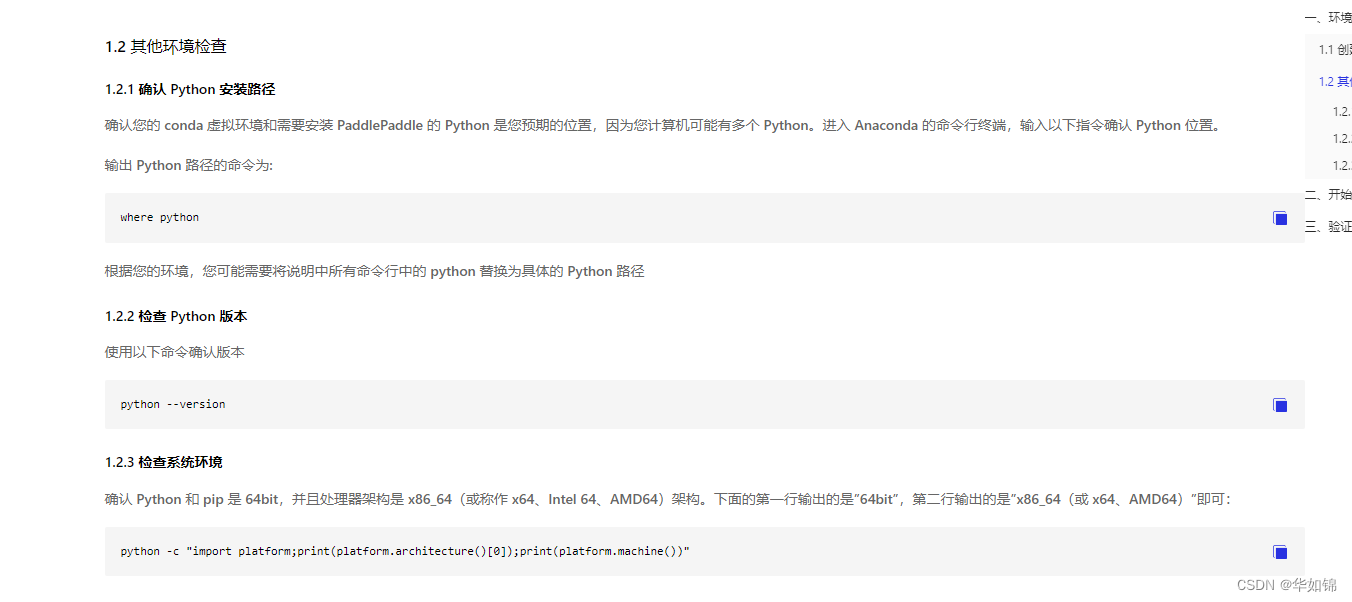

视频链接

eMMC电路设计01_哔哩哔哩_bilibili

eMMC电路设计

1、eMMC简介

eMMC叫嵌入式多媒体卡,英文全称为Embedded Multi Media Card。是一种闪存卡(Flash Memory Card)标准,它定义了MMC的架构以及访问Flash Memory的接口和协议。

嵌入式多媒体存储卡eMMC是一种管理型Nand Flash。

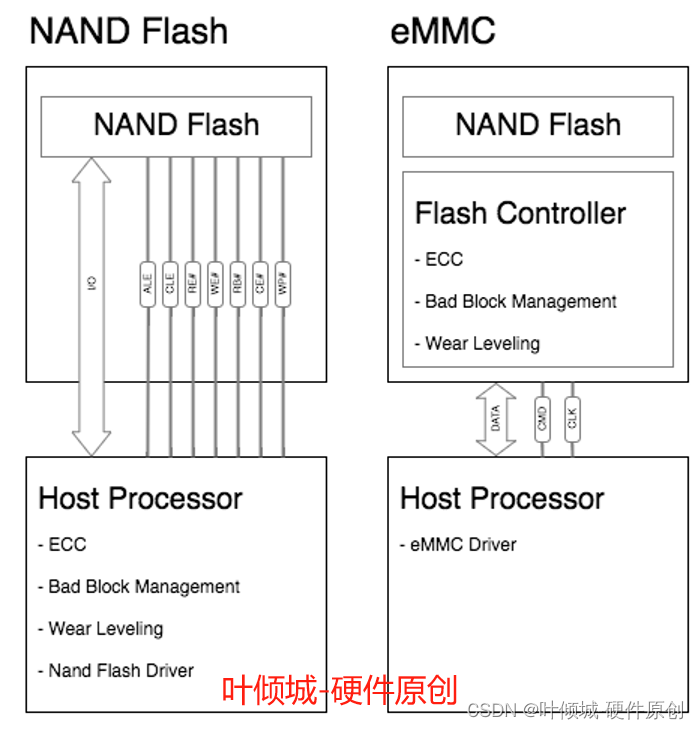

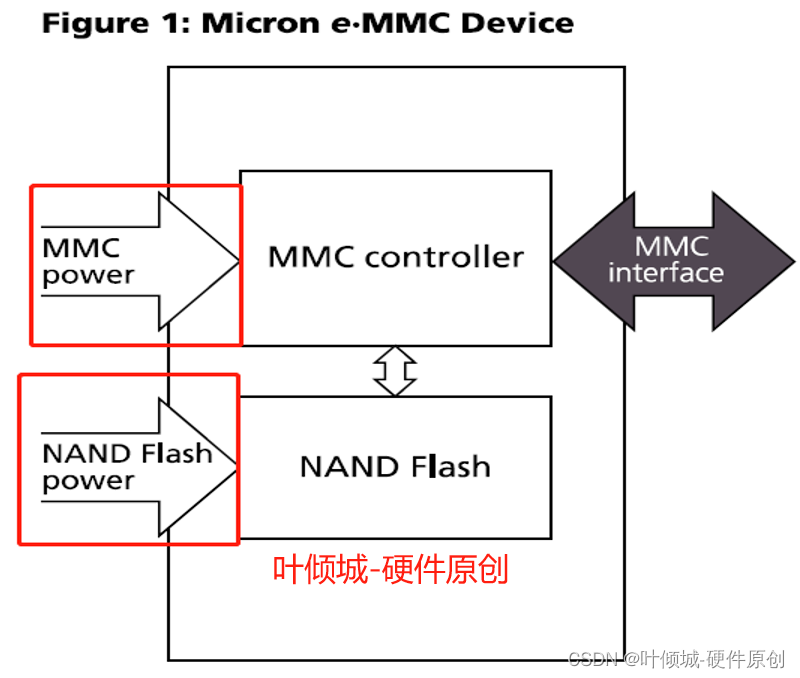

eMMC芯片实际上是一个封装继承了Nand Flash和控制Flash的控制器,控制器把坏块管理、ECC校验以及损耗均衡等一些Flash具备的管理功能集成到芯片里,然后对外的接口采用的是标准的MMC(多媒体存储卡)接口,用户只需要根据接口的协议,开发控制器就能操作芯片。

其接口电压可以是1.8V或者是3.3V。它的特点就是容量大,数据传输快,尺寸小,开销很小。

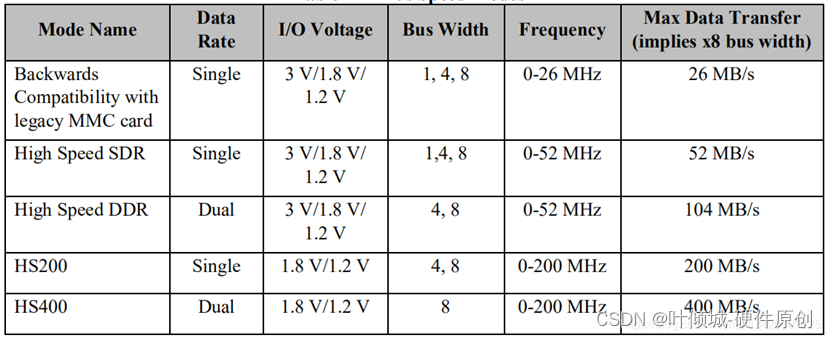

eMMC5.0的协议与eMMC低版本例如4.5,4.4等的区别就在于读写速度有区别。低版本的不支持HS200和HS400的速度,四点几的现在基本上停产,选用eMMC5.0的协议。

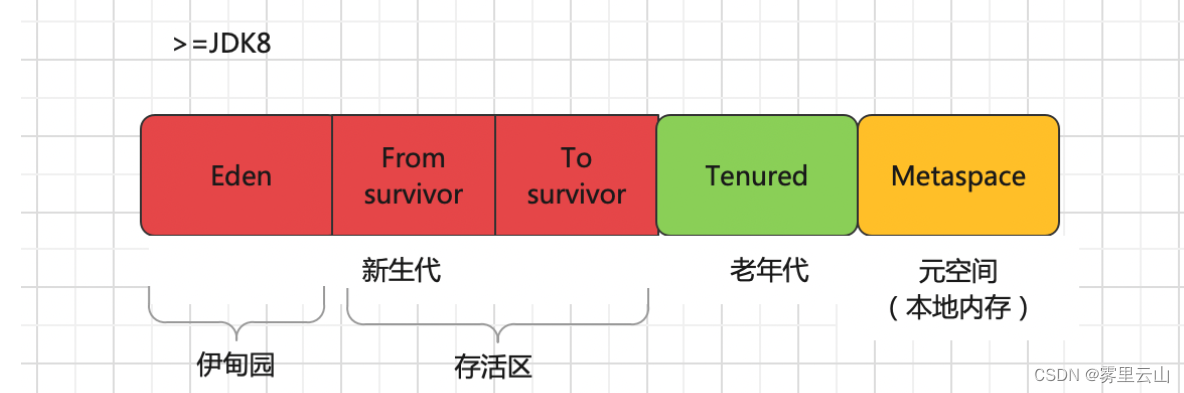

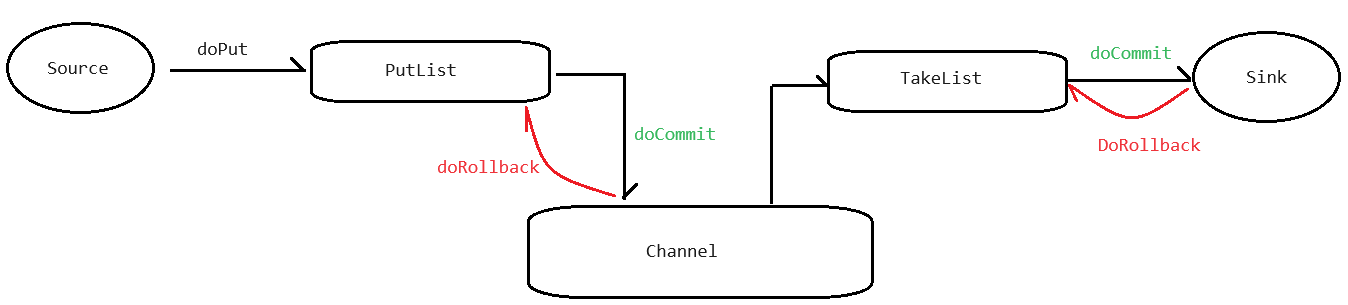

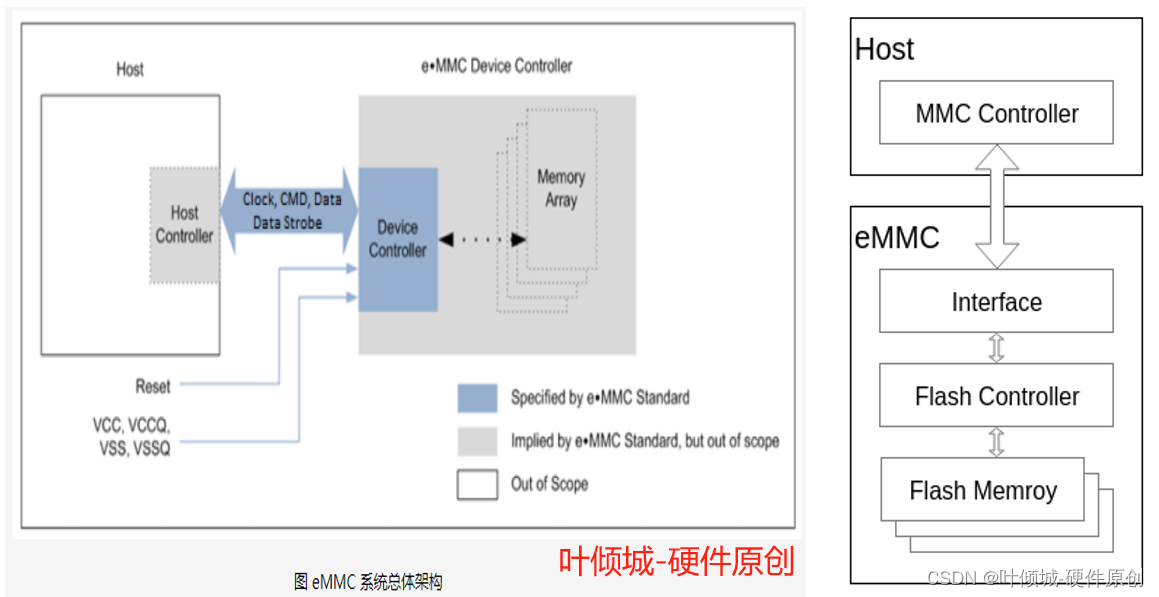

2、eMMC系统总体架构(三部分)

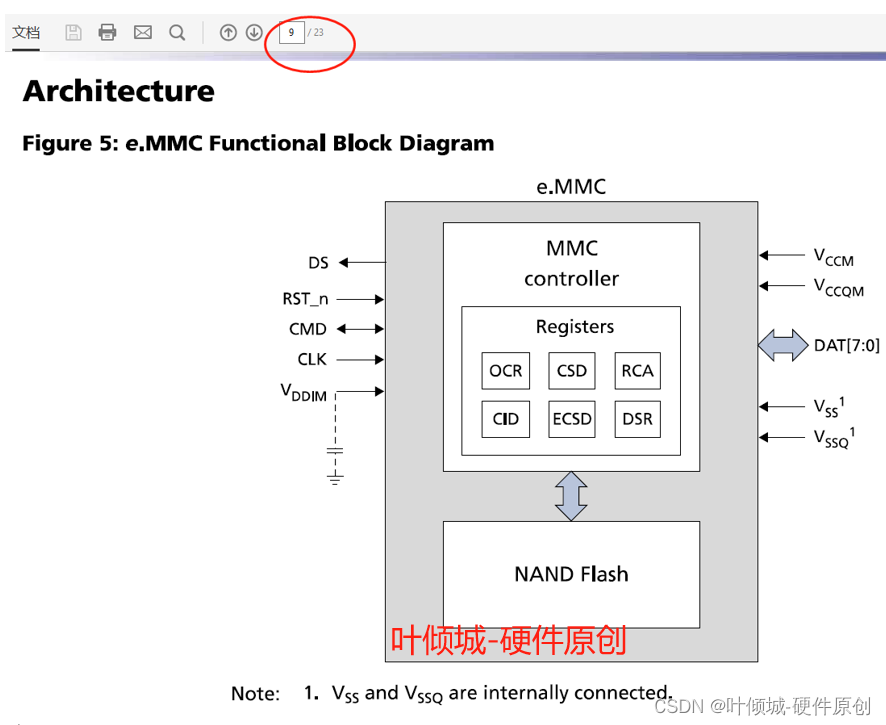

eMMC规范主要定义了Device Controller和接口的相关规范,如图中蓝色部分标识

eMMC内部主要可以分为Flash Memory、Flash Controller以及Host Interface三大部分。

2.1、Flash Memory

Flash Memory是一种非易失性的存储器,通常在嵌入式系统中用于存放系统、应用和数据等,类似与PC系统中的硬盘。

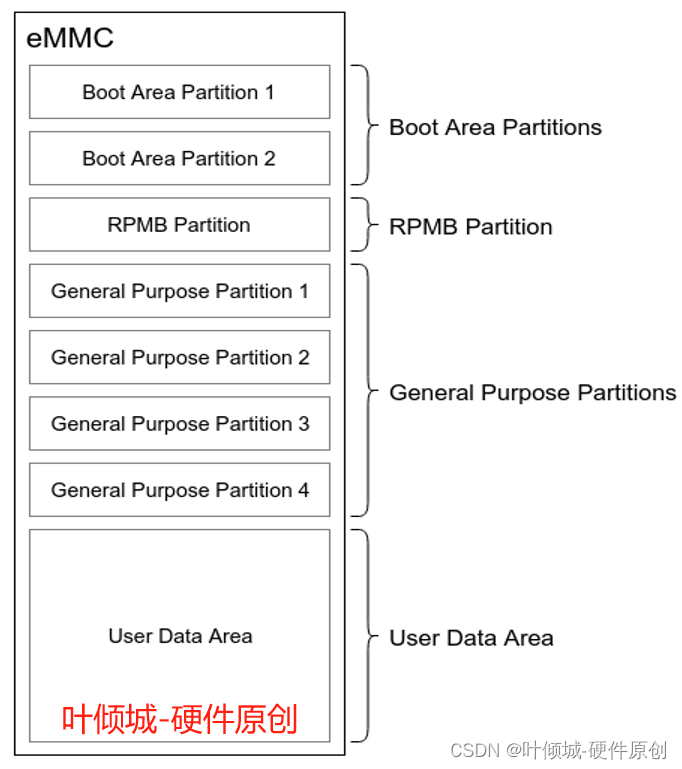

eMMC在内部对Flash Memory划分了4个主要区域,如下图所示:

eMMC 内部分区

1、BOOT Area Partition 1&2:此分区主要是为了支持从eMMC启动系统而设计的。

2、RPMB Partition:RPMB是Replay Protected Memory Block的简称。

3、General Purpose Partition 1~4:此区域则主要用于存储系统或者用户数据。

4、User Data Area:此区域则主要用于存储系统和用户数据。

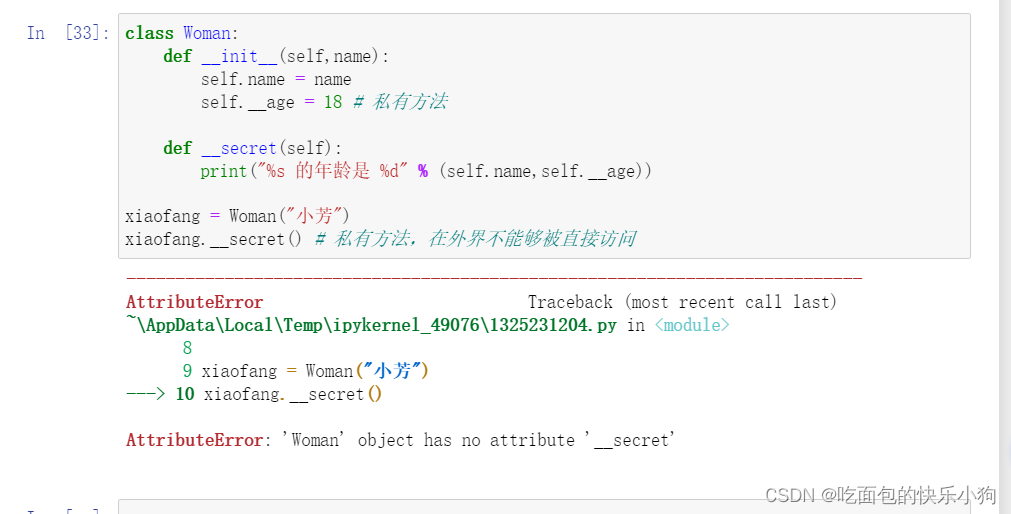

2.2、Flash Controller

NAND Flash直接接入Host时,Host端通常需要有NAND Flash Translation Layer,即NFTL或者NAND Flash文件系统来做坏块管理、ECC等的功能。

NAND Flash 与 eMMC

2.3、Host Interface

eMMC与Host之间的连接如下图所示:

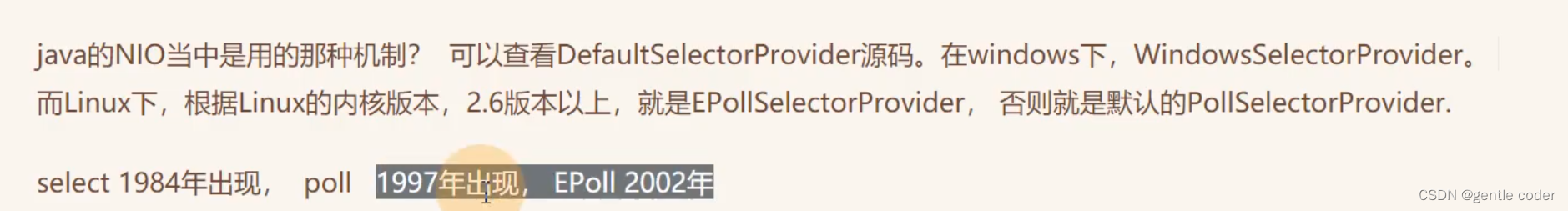

3、eMMC性能

接口速度高达每秒52MB,EMMC具有快速、可升级的性能。同时接口电压可以是1.8V或者3.3V。eMMC的速度模式分为SDR50、HS200、HS400,共三种。

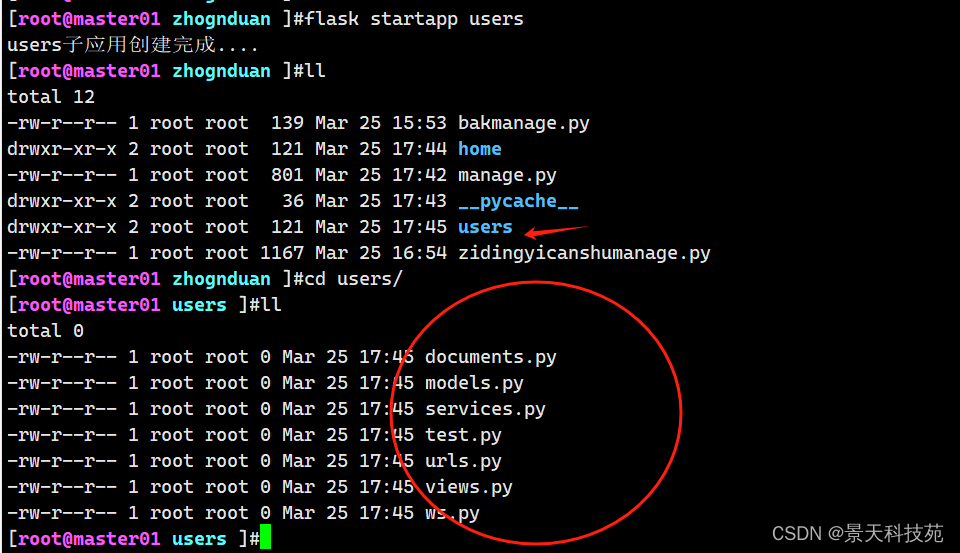

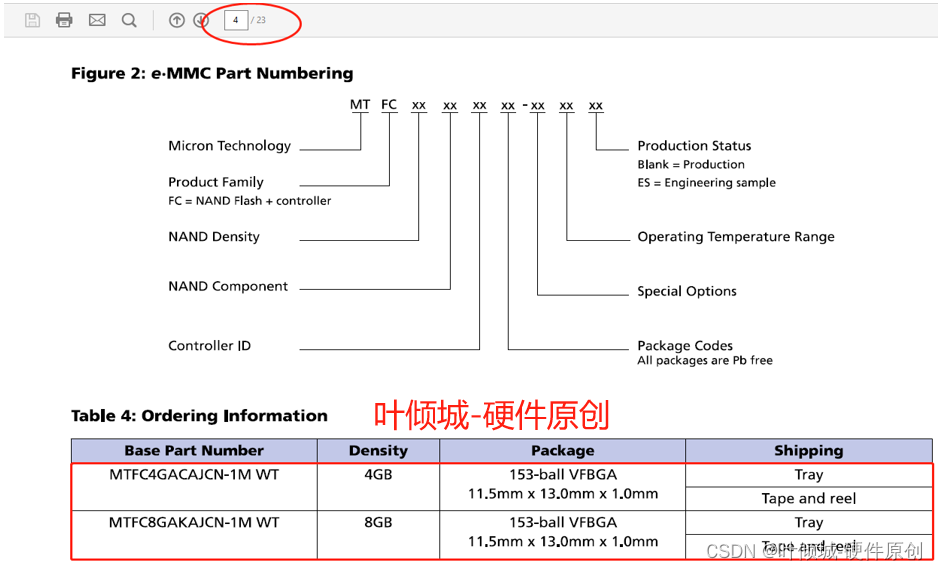

4、eMMC实例(整版以镁光-MTFC8GAKAJCN为例)

4.1、eMMC命名规范

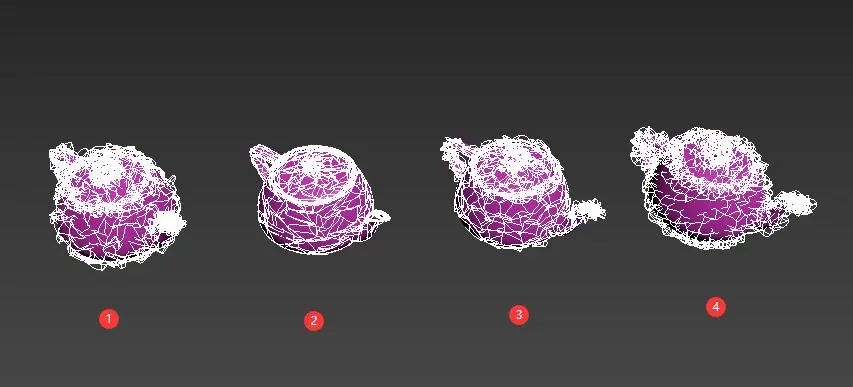

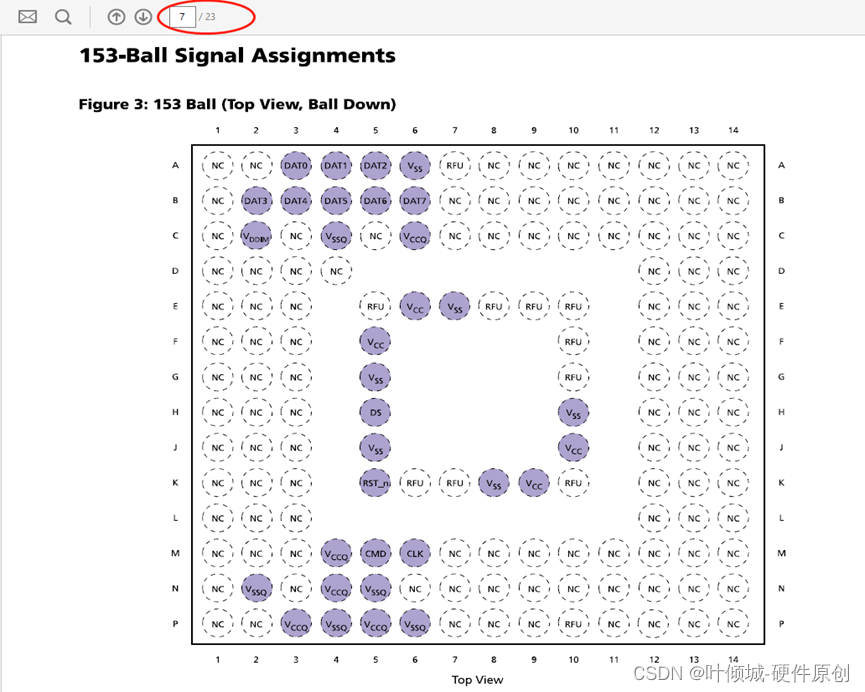

4.2、eMMC封装(153-ball BGA)

5、eMMC框图

6、eMMC工作流程

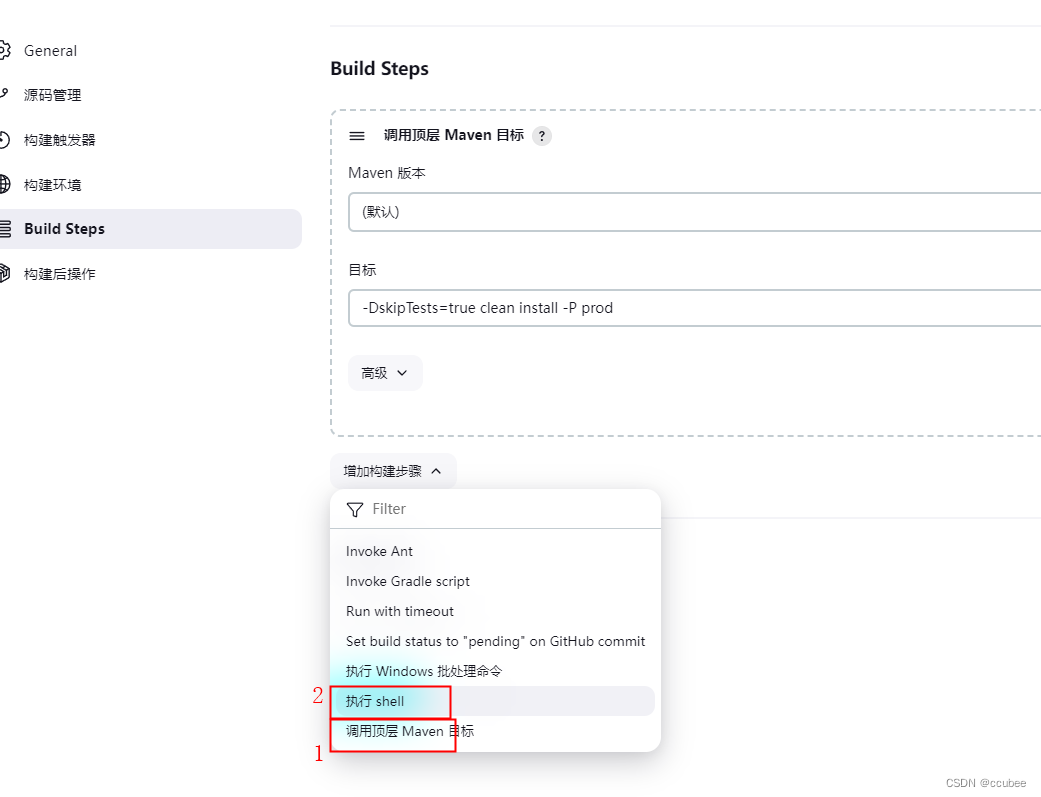

6.1、工作流程

(一)eMMC的初始化

(二)eMMC的读写

6.2、操作模式

主要有5种操作模式:

7、eMMC管脚定义

| 管脚符号 | 类型 | 描述 |

| VCC (VDDF) | Supply | Vcc: NAND interface I/O and NAND Flash power Supply。(Supply voltage for Core) |

| VCCQ (VDD) | Supply | VccQ: eMMC controller core and eMMC I/O power Supply。(Supply voltage for I/O) |

| VSSQ | Supply | VSSQ: eMMC controller core and eMMC I/F ground connection。 (VSS and VSSQ are connected internally。) |

| VSS | Supply | Ground connections。 |

| VDDIM | Internal voltage node。 Do not tie to supply voltage or ground。 |

信号线

| 管脚符号 | 类型 | 描述 |

| DAT[7:0] | I/O | Bidirectional data channels. It operates in push-pull mode。 |

| RST_n | I | Hardware reset signal pin |

| DS (Data Strobe) | O | Data strobe: Generated by the device and used for data output and CRC status response output in HS400 mode。The frequency of this signal follows the frequency of CLK。For data output, each cycle of this signal directs two bits transfer(2X) on the data , one bit for the positive edge and the other bit for the negative edge。For CRC status response output,the CRC status is latched on the positive edge only, and is “Don’t Care ”on the negative edge。 |

| CLK | I | Clock input |

| CMD | I/O | A bidirectional signal used for device initialization and command transfers. Command operates in two modes, open-drain for initialization and push-pull for fast command transfer. |

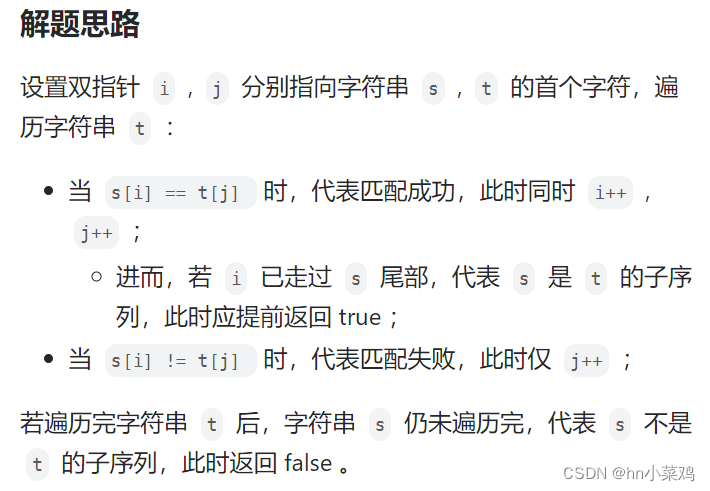

各个信号的用途如下所示:

CLK:用于同步的时钟信号

Data Strobe:此信号是从Device端输出的时钟信号,频率和CLK信号相同,用于同步从Device端输出的数据。该信号在eMMC 5.0中引入。

CMD:此信号用于发送Host的command和Device的response。

DAT0-7:用于传输数据的8bit总线。

Host与eMMC之间的通信都是Host以一个Command开始发起的。针对不同的Command,Device会做出不同的响应。

DAT[7:0] 8根

CLK 1根

RST_n 1根

DS 1根

CMD 1根

NC 109根

RFU 11根

VCC 4根

VCCQ 5根

VDDIM 1根

VSS 6根

VSSQ 5根

合计:12+120+21=153