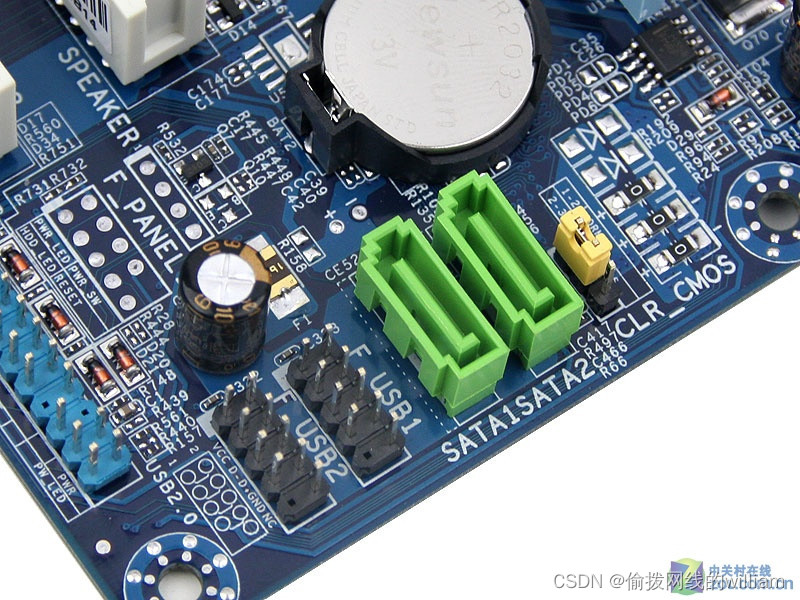

IP设置

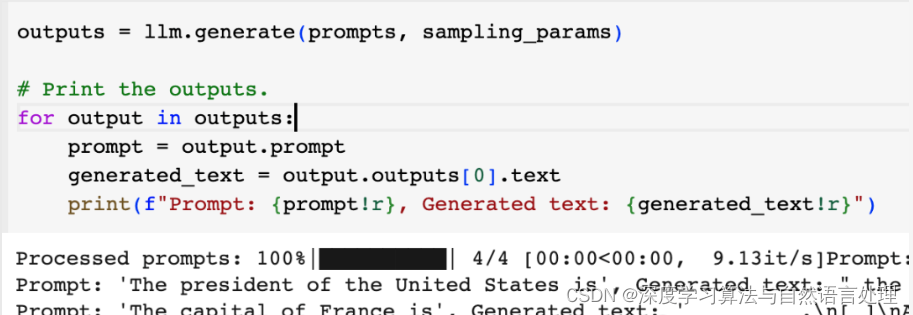

代码

aurora_8b10b aurora_8b10b_inst (

/**********************************************************************************///axi_stream tx

.s_axi_tx_tdata(s_axi_tx_tdata), // input wire [0 : 31] s_axi_tx_tdata

.s_axi_tx_tkeep(s_axi_tx_tkeep), // input wire [0 : 3] s_axi_tx_tkeep

.s_axi_tx_tlast(s_axi_tx_tlast), // input wire s_axi_tx_tlast

.s_axi_tx_tvalid(s_axi_tx_tvalid), // input wire s_axi_tx_tvalid

.s_axi_tx_tready(s_axi_tx_tready), // output wire s_axi_tx_tready

/**********************************************************************************///ufc no use tx frame

.s_axi_ufc_tx_tvalid(s_axi_ufc_tx_tvalid), // input wire s_axi_ufc_tx_tvalid

.s_axi_ufc_tx_tdata(s_axi_ufc_tx_tdata), // input wire [0 : 2] s_axi_ufc_tx_tdata

.s_axi_ufc_tx_tready(s_axi_ufc_tx_tready), // output wire s_axi_ufc_tx_tready

/**********************************************************************************///axi_stream rx

.m_axi_rx_tdata(m_axi_rx_tdata), // output wire [0 : 31] m_axi_rx_tdata

.m_axi_rx_tkeep(m_axi_rx_tkeep), // output wire [0 : 3] m_axi_rx_tkeep

.m_axi_rx_tlast(m_axi_rx_tlast), // output wire m_axi_rx_tlast

.m_axi_rx_tvalid(m_axi_rx_tvalid), // output wire m_axi_rx_tvalid

/**********************************************************************************///ufc no use rx frame

.m_axi_ufc_rx_tdata(m_axi_ufc_rx_tdata), // output wire [0 : 31] m_axi_ufc_rx_tdata

.m_axi_ufc_rx_tkeep(m_axi_ufc_rx_tkeep), // output wire [0 : 3] m_axi_ufc_rx_tkeep

.m_axi_ufc_rx_tlast(m_axi_ufc_rx_tlast), // output wire m_axi_ufc_rx_tlast

.m_axi_ufc_rx_tvalid(m_axi_ufc_rx_tvalid), // output wire m_axi_ufc_rx_tvalid

/**********************************************************************************///

.hard_err(hard_err), // output wire hard_err

.soft_err(soft_err), // output wire soft_err

.frame_err(frame_err), // output wire frame_err

/**********************************************************************************///error

.channel_up(channel_up), // output wire channel_up

.lane_up(lane_up), // output wire [0 : 0] lane_up

.txp(txp), // output wire [0 : 0] txp

.txn(txn), // output wire [0 : 0] txn

/**********************************************************************************///reset

.reset(reset), // input wire reset

.gt_reset(gt_reset), // input wire gt_reset

/**********************************************************************************///

.loopback(3'b000), // input wire [2 : 0] loopback

.rxp(rxp), // input wire [0 : 0] rxp

.rxn(rxn), // input wire [0 : 0] rxn

/**********************************************************************************///crc

.crc_valid(crc_valid), // output wire crc_valid

.crc_pass_fail_n(crc_pass_fail_n), // output wire crc_pass_fail_n //1 is pass ,0 is fail

/**********************************************************************************///dynamic setup

.drpclk_in(drpclk_in), // input wire drpclk_in

.drpaddr_in(drpaddr_in), // input wire [8 : 0] drpaddr_in

.drpen_in(1'b0), // input wire drpen_in

.drpdi_in(drpdi_in), // input wire [15 : 0] drpdi_in

.drprdy_out(drprdy_out), // output wire drprdy_out

.drpdo_out(drpdo_out), // output wire [15 : 0] drpdo_out

.drpwe_in(1'b0), // input wire drpwe_in

/**********************************************************************************///power down mode

.power_down(1'b0), // input wire power_down

/**********************************************************************************///

.tx_lock(tx_lock), // output wire tx_lock

.tx_resetdone_out(tx_resetdone_out), // output wire tx_resetdone_out

.rx_resetdone_out(rx_resetdone_out), // output wire rx_resetdone_out

.link_reset_out(link_reset_out), // output wire link_reset_out

/**********************************************************************************///initial clk signle

.init_clk_in(init_clk_in), // input wire init_clk_in

/**********************************************************************************///user clk

.user_clk_out(user_clk_out), // output wire user_clk_out

.pll_not_locked_out(pll_not_locked_out), // output wire pll_not_locked_out

/**********************************************************************************///high en

.sys_reset_out(sys_reset_out), // output wire sys_reset_out

/**********************************************************************************///pin refclk

.gt_refclk1_p(gt_refclk1_p), // input wire gt_refclk1_p

.gt_refclk1_n(gt_refclk1_n), // input wire gt_refclk1_n

.sync_clk_out(sync_clk_out), // output wire sync_clk_out

.gt_reset_out(gt_reset_out), // output wire gt_reset_out

.gt_refclk1_out(gt_refclk1_out), // output wire gt_refclk1_out

.gt0_pll0refclklost_out(gt0_pll0refclklost_out), // output wire gt0_pll0refclklost_out

.quad1_common_lock_out(quad1_common_lock_out), // output wire quad1_common_lock_out

.gt0_pll0outclk_out(gt0_pll0outclk_out), // output wire gt0_pll0outclk_out

.gt0_pll1outclk_out(gt0_pll1outclk_out), // output wire gt0_pll1outclk_out

.gt0_pll0outrefclk_out(gt0_pll0outrefclk_out), // output wire gt0_pll0outrefclk_out

.gt0_pll1outrefclk_out(gt0_pll1outrefclk_out) // output wire gt0_pll1outrefclk_out

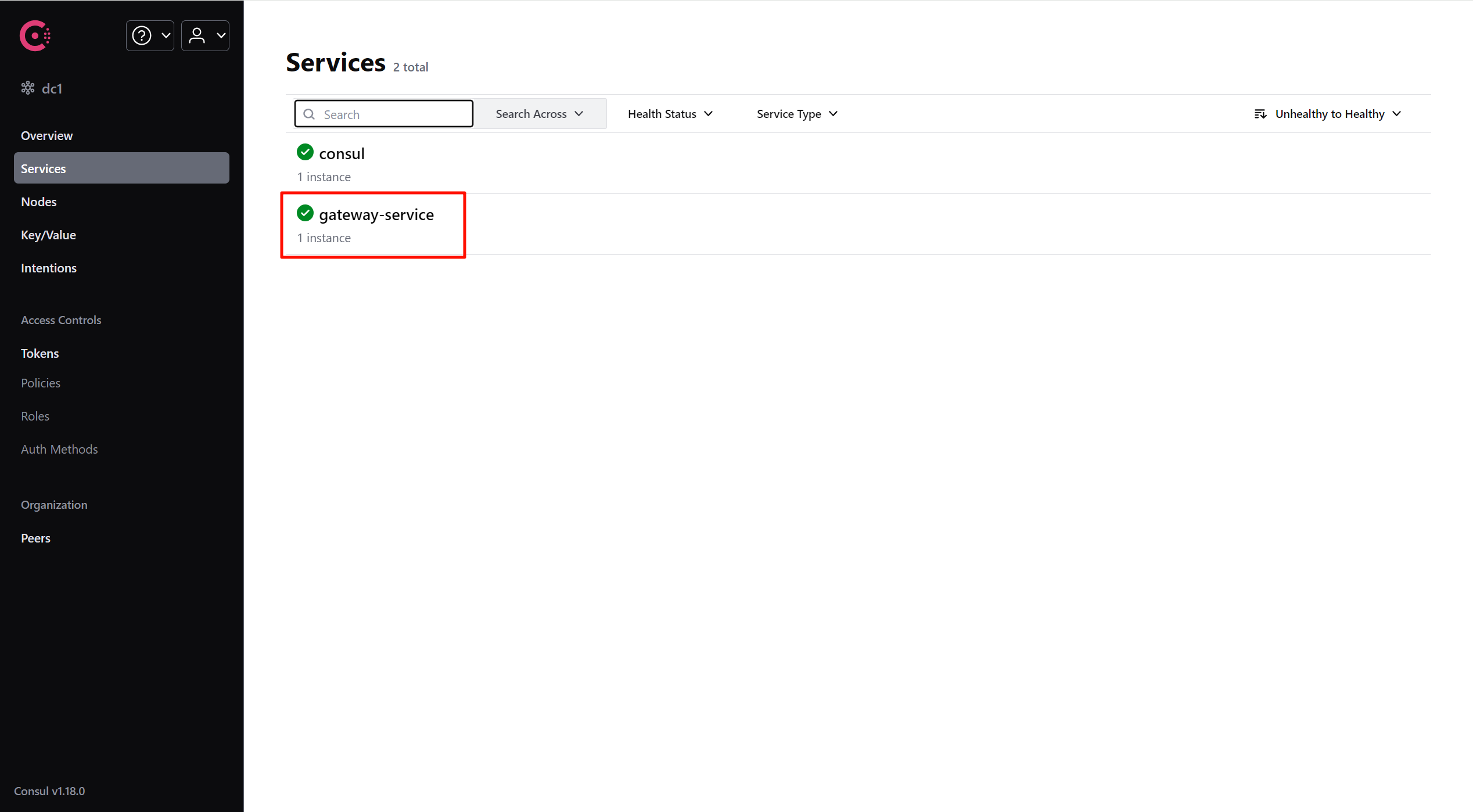

);channel up

lane up

在仿真的时候大概需要700us才会有效,不然数据一直处于复位状态。

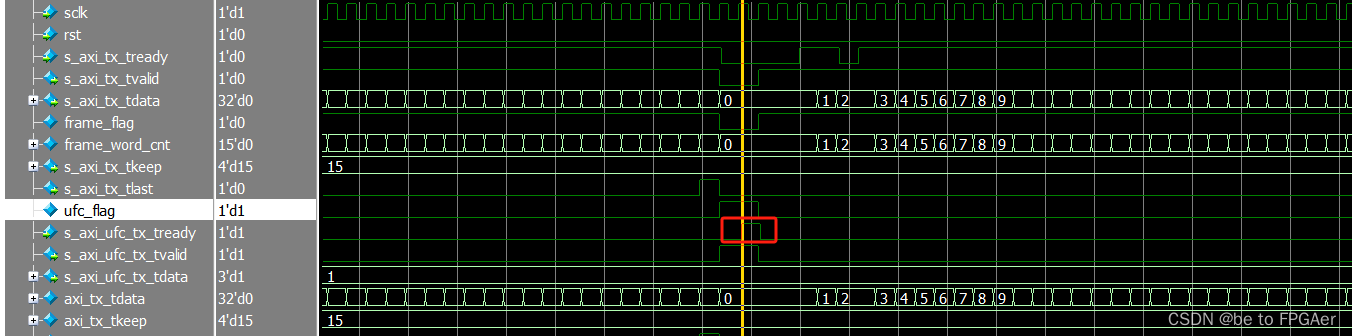

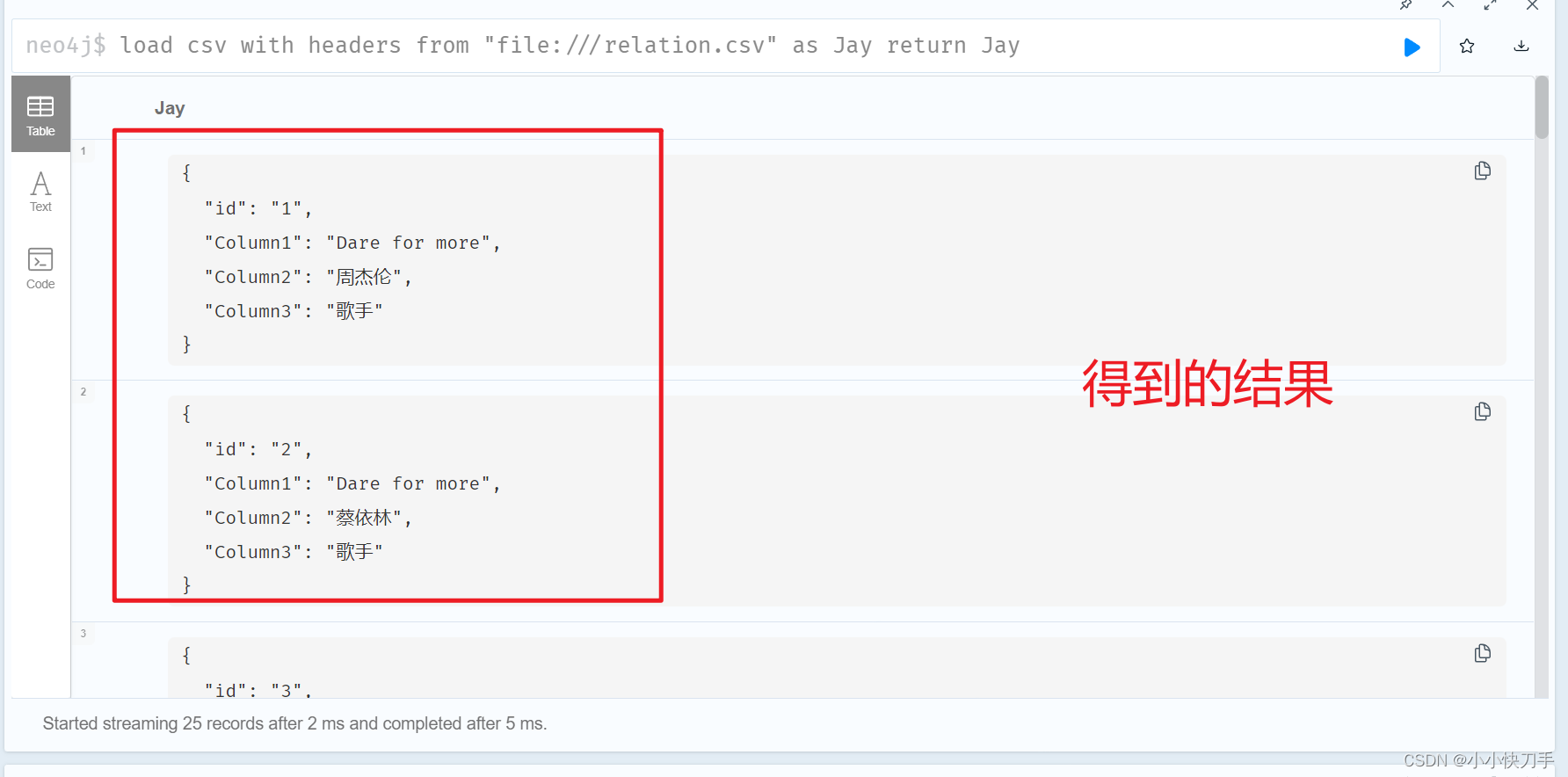

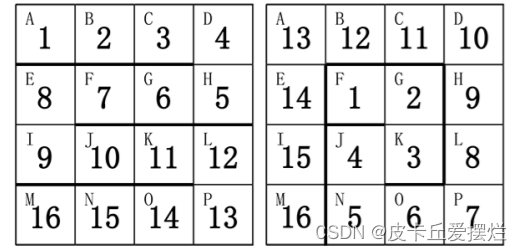

ufc在没帧之后有一个周期的发送,(设置为一周期4byte,发送32bit)