Avalon总线学习

avalon总线可以分为:

-

Avalon clock interface

-

Avalon reset interface

-

Avalon Memory mapped interface

-

Avalon iterrupt interface

-

Avalon streaming interface

-

Avalon tri-state conduit interface

-

Avalon conduit interface

1、Avalon clock interface

这是一个时钟接口,所有的avalon接口都是同步的,都需要有一个时钟,在qsys中,我们每添加一个新的IP核,都需要将它与时钟连接上。自定义IP核时,可以定义一个时钟接口,也可以定义多个时钟接口,时钟接口可以时输入,也可以是输出,就比如PLL锁相环,有输入时钟,又有输出时钟。下图是锁相环的接口图

我们重点关注clock sink输入接口和clock source输出接口。

1)clock sink信号类型:

| 信号 | 宽度 | 方向 | 是否必选 | 描述 |

|---|---|---|---|---|

| clk | 1 | input | 是 | 一时钟信号,为内部逻辑和其他接口提供同步 |

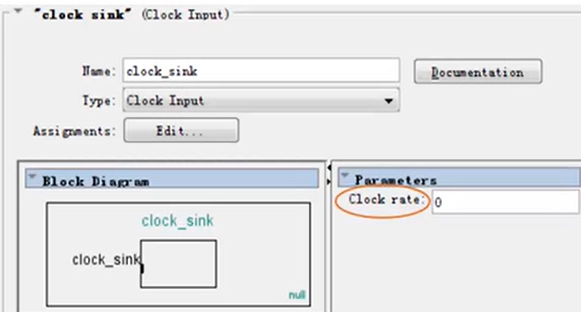

在qsys中clock sink的属性:

只有一个clock rate,如果为0,那么clock rate无效,如果不为0并且连接的时钟源不是指定的频率,那么qsys则发出警告,一般我们这里采用默认设置就可以了。

2)clock source信号类型

| 信号 | 宽度 | 方向 | 是否必选 | 描述 |

|---|---|---|---|---|

| clk | 1 | output | 是 | 一个输出时钟信号 |

clock sink是用于整个内部逻辑和其他接口的时序

clock source就是用于外部逻辑和其他接口的时序。

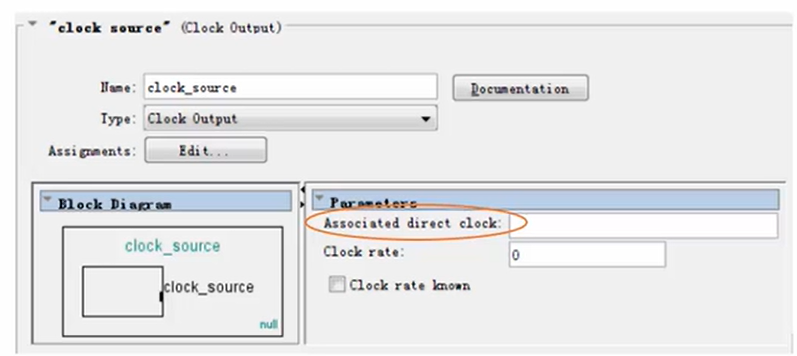

属性如下:

-

associaated direct clock

任何一个同步的接口都要依附一个时钟,那么这个依附的时钟就是associaated direct clock ,比如双口fifo,我们的输入端口依附的时钟就是输入时钟,我们的输出端口依附的就是输出时钟。

-

clock rate

表示频率,使用默认设置即可

- clock rate known

表示时钟频率是否已经知道,如果已经知道,这个信息在系统中可以用于自定义其他 组件

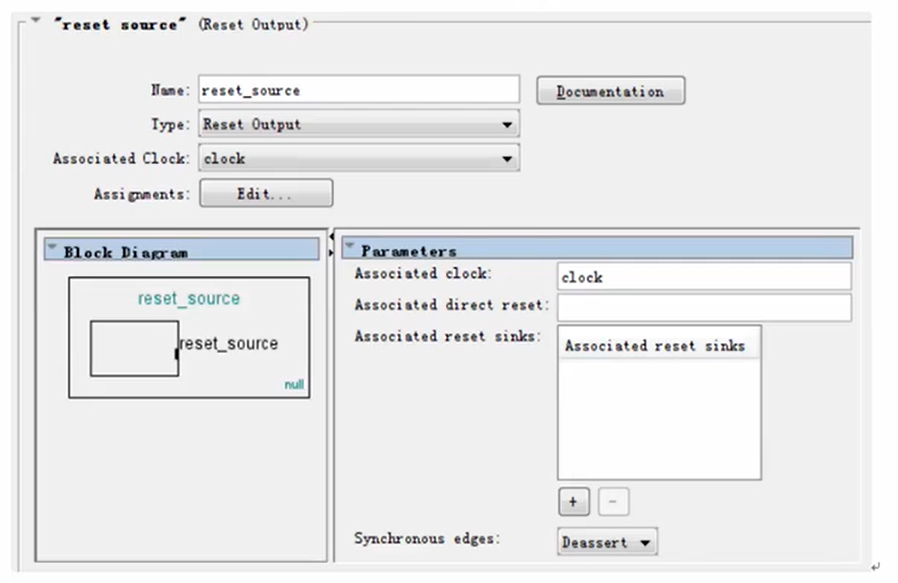

2、Avalon reset interface

这是又给复位接口,avlaon接口他们的复位都是连接在一起的,只要nios ii处理器复位了,那么所有的ip也会一起复位。和时钟接口一样可以分为reset sink和reset source。

信号类型

| 信号 | 宽度 | 方向 | 是否必选 | 描述 |

|---|---|---|---|---|

| reset、reset_n | 1 | input | 必选 | 复位信号,reset高电平有效,reset_n低电平有效 |

| reset_req | 1 | input | 可选 | 复位请求信号 |

信号属性

1)reset sink的信号属性:

associateed clock

关联的同步信号,如果我们自定义IP核将输入时钟接口命名为clk,那么此时同步到该接口的时钟名称就是clk,如果我们命名为clock那么此时同步到该接口的时钟名称就是clock。

- synchronous edges

表示reset输入需要同步类型,none选项表示不服位;deassert选项表示异步复位;both选项表示同步复位。

2)reset source

| 信号 | 宽度 | 方向 | 是否必选 | 描述 |

|---|---|---|---|---|

| reset、reset_n | 1 | output | 必选 | 复位信号,reset高电平有效,reset_n低电平有效 |

| reset_req | 1 | output | 可选 | 复位请求信号 |

属性:和reset sink差不多

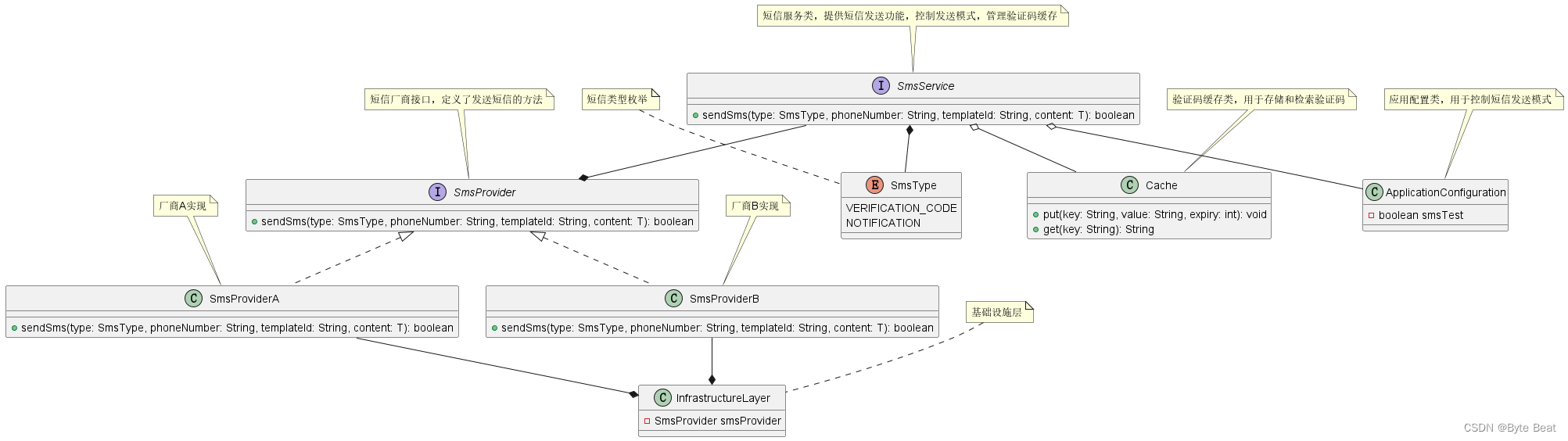

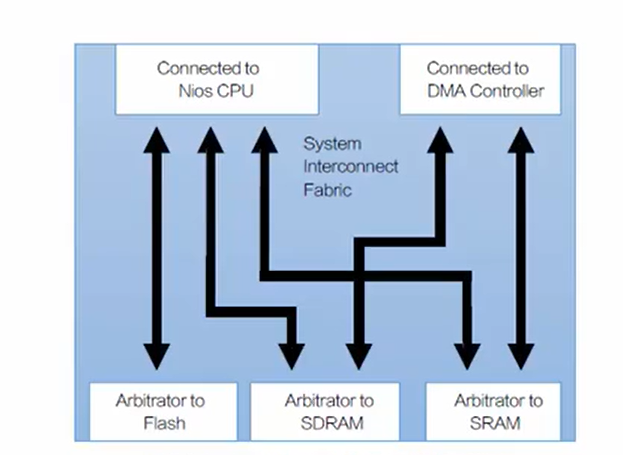

3、Avalon Memory mapped interface

也就是Avalon-MM,它是一个地址映射接口,可以通过地址读写数据,这个接口非常的常用,也是一个非常重要的接口,疑问我们后面自定义用户外设的化,也是基于这个接口去构建的。采用全同步时序。

Avalon-MM总线是一种主从式的传输方式,由一个主控端外设发起并控制传输的过程,而从属端外设响应经由总线模块发来的信号完成整个传输。Avalon-MM总线不会因为总线被占据而延误传输的时间,有逻辑仲裁,可以遵循先来后到的规则,也可以遵循谁重要谁先访问的规则。

也就是nios cpu可以跟多个外设建立一个单独的通道,当多个主机访问同一个slave时,由仲裁模块决定谁先访问.

信号类型以及信号流向:

Avalon-MM信号可以分为主端口信号和从端口,每个单独的主端口或从端口使用的信号类型由外设的设计决定.

属性:

| 属性名称 | 描述 |

|---|---|

| address units | 为地址信号指定单位 |

| associated clock | 同步到该接口的时钟名称 |

| associated reset | 同步到该接口的复位名称 |

| Bits per symbol | 定义每个符号位的位数 |

| Burstcount ubits | 为burstcount信号指定单位 |

| Explicit address span | 明确地址范围 |

| setup | 数据建立时间 |

| read wait | 读取等待时间 |

| write wait | 写入等待时间 |

| Hold | 数据保持时间 |

| Timing units | 为setup,hold,write wait和read wait指定单位 |

| Read latenccy | 读延时 |

| Maximum pending read transactions | 在从设备中:这个参数是从设备在等候未读的队列最大数。在主设备中:表示主设备生成的未解决的读事件数量 |

| Burst on rurst boundaries only | 写信号 |

| LineWrap Bursts | 写进来的数据 |

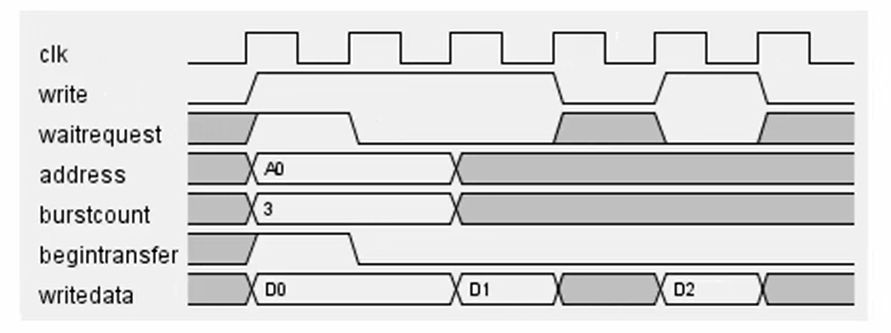

传输方式有:基本传输、流水线传输、突发传输的。流水线传输地址需要多次发送,而突发传输只需要发送1次(首地址)。

Avalon-MM的传输时序:

同种类型的主端口与从端口传输在时序上基本是一致的,其区别仅在于主端口传输时由主端口外设驱动总线模块,而从端口传输是由总线模块驱动从端口外设。

-

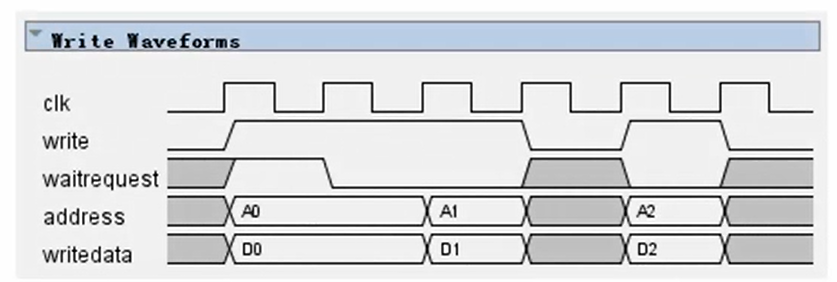

Avalon-MM从端口固定延时的写基本传输时序图

当时钟的上升沿到来的时候,拉高write信号,同时给出写地址address和要写的数据writedata。信号的流向可以参考上图:信号类型以及信号流向

将write wait设置为2,就变成下图,write信号延迟了2个时钟周期,可以给外设充分的响应时间。

当waitrequest信号为低时,且write为高时,在时钟上升沿地址和数据才能被传输。

-

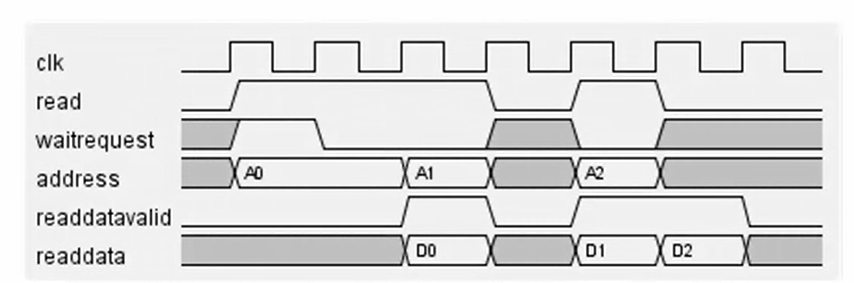

流水线传输时序

下面时序是主机读取从机的数据,主机将read拉高,从机发送低电平的waitrequest信号给主机时,主机将地址address信号传输给从机,从机返还数据给主机的同时把readdatavalid信号拉高,代表数据有效。

在流水线时序传输时序中,需亚奥设置Maximum pending read transactions信号属性,这个属性时表示这个模块最大能接受的流水量。

-

读突发传输

read:主机->从机,拉高,同时将address地址和burstcount突发长度给从机,告诉从机从哪里开始读取数据,读取几个数据。

readdatavali:从机–>主机,拉高时,代表从机返还数据给主机,主机可以开始接收数据了。

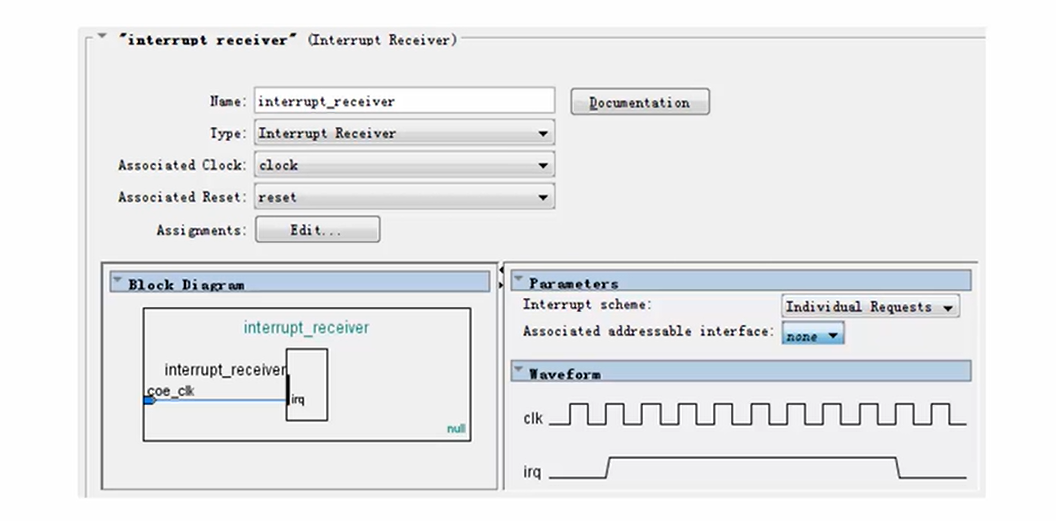

4、Avalon interrupt interface

这一一个中断接口,自定义外设组件中需要使用中断功能的时候,我们就可以通过这个接口来实现。

1)输入:interrupt receiver

| 信号类型 | 位宽 | 是否必选 | 描述 | 方向 |

|---|---|---|---|---|

| irq | 1-32 | 是 | irq是n位的矢量,每个位直接对应一个IRQ发送器,没有优先级在内的呈现 | 输入 |

- 属性

2)输出:interrupt sender

| 信号类型 | 位宽 | 是否必选 | 描述 | 方向 |

|---|---|---|---|---|

| irq、irq_n | 1 | 中断请求信号。当从器件需要接收时使irq有效 | output |

- 属性:

中断号0的最高,然后是1,依次递推。

5、Avalon streaming interface

它是一个流接口,streaming就是流水的意思,它支持单向数据流,包括数据包,dsp数据等等,avalon-st接口与avalon-mm接口的区别是非常明显的,avalon-mm接口主要用于sopc控制流传输或者简单的数据流传输,而avalon-st接口则主要用于sopc设计中高速数据流的传输,二者可以说是相辅相成的,搭配使用可以清晰的分离系统内的控制流核数据流,显著地提高系统整体地可靠性核运行效率。Avalon-ST是一种单向点对点的高速接口。

| Avalon-MM | 用于qsys控制流传输或者简单的数据流传输 |

|---|---|

| Avalon-ST | 适用于一些传递速度要求较高,没有地址要求的应用方面 |

Avalon-MM包含两种接口source端口和sink端口,数据流向

- 信号类型:

- 属性:

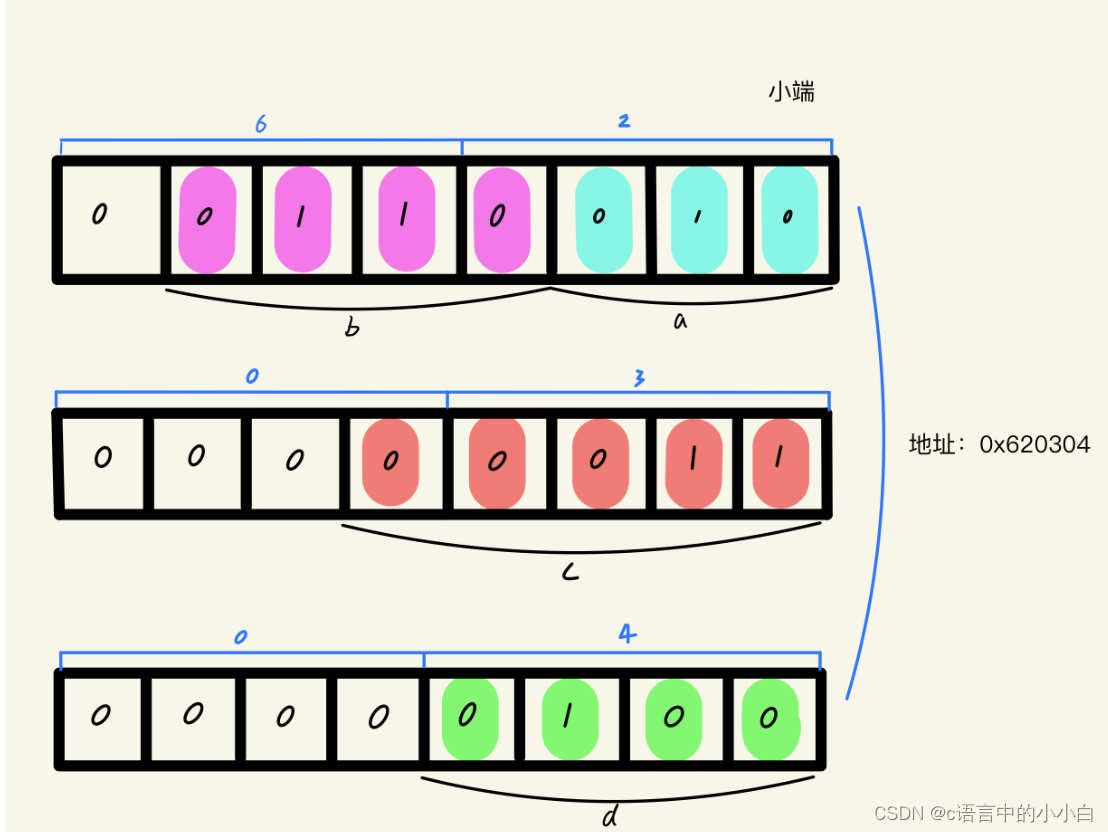

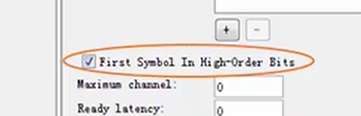

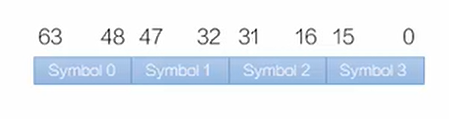

注意first symbol in high-order bits选项:

解释一下这个选项的含义:

假设data bits per symbol=16,将它分为symbol0、symble1、symbol2和symbol3四组,如果选中了first symbol in high-order bits,那么symbol0就在最高位,如果没有选中,那么symbol0就会在最低位。

-

Avalon-ST的传输时序

分为基本传输和包传输。

1)基本传输:

基本传输无反馈信号连接示意图:source接口发送数据,sink接口接收数据。valid信号表示数据是否有效。

时序图:valid信号为高就可以采集数据了,此时数据有效。

有反馈信号ready的基本传输连接示意图:

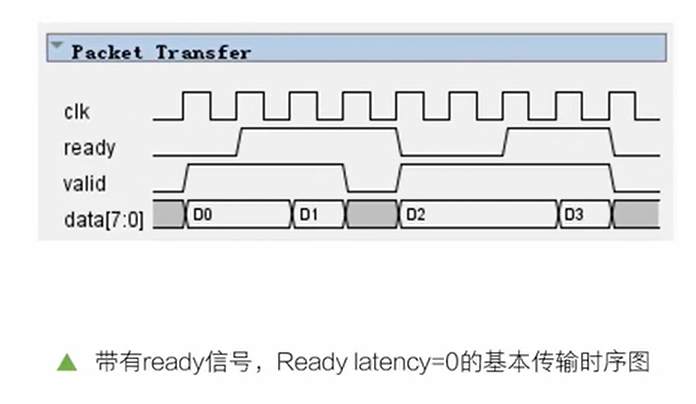

因为有ready信号,我们就可以使用到于ready信号相配合使用的ready latency信号属性。如下图,当ready为低的时候,sink是不接受数据的,只有当ready、

valid同时为高是,sink接口才可以接收数据。

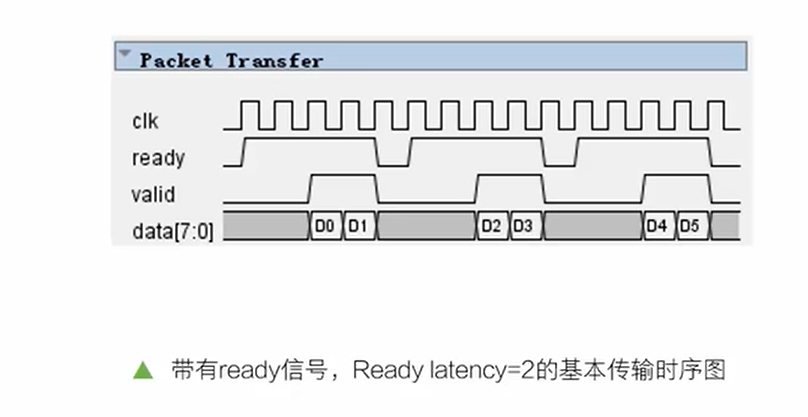

再看一个例子:当ready信号有效时,valid信号等待了2个时钟周期才有效,此时sink才会接收source发送的数据。

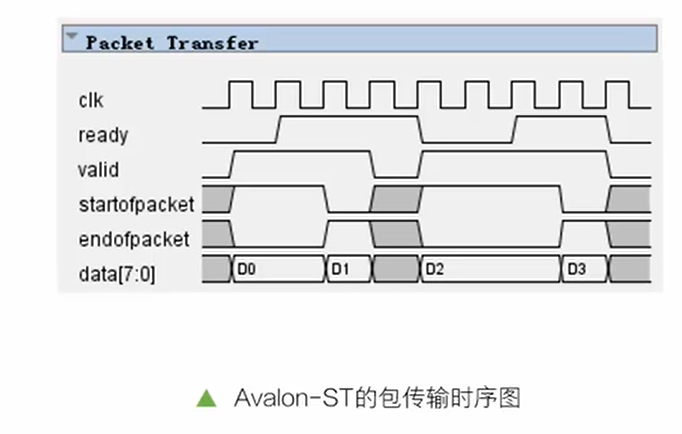

2)包传输

在Avalon-ST中,我们使用SOP和EOP来指示一个包。sop就是start of packet ,eop就是end of packet。

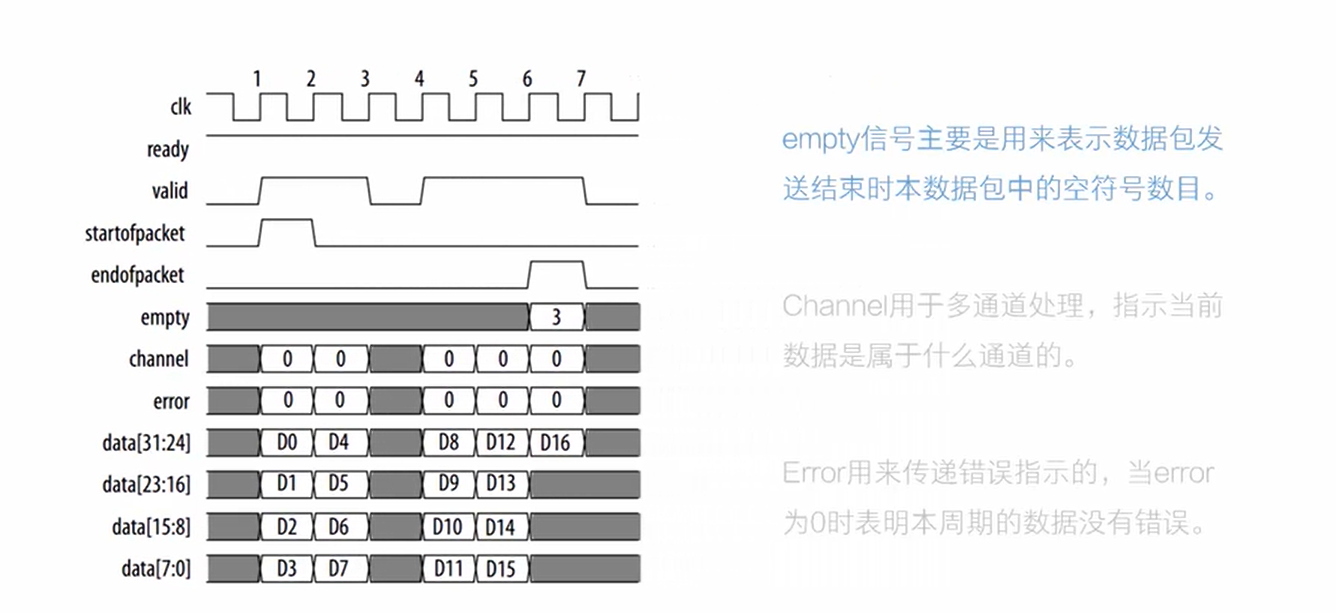

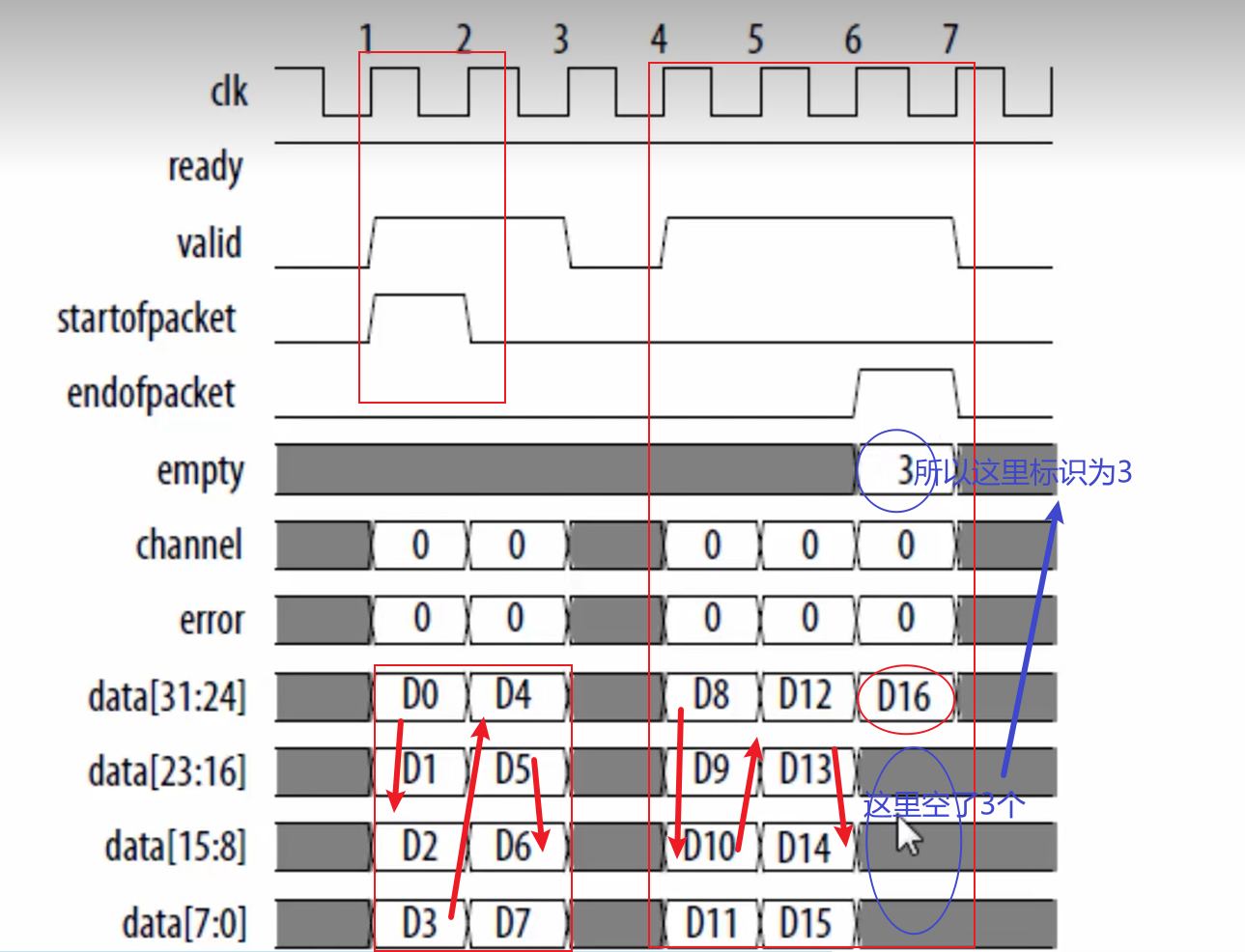

时序图:

startofpacket和endofpacket的值仅在valid信号拉高时有意义。当startofpacket为高时,数据就开始传输,当endofpacket为高时,数据包停止传输。当两次包传输之间没有空闲期时,startofpacket信号可以紧跟一次包传输的endofpacket信号。注意当ready信号和valid信号同时为高时才开始传输数据。

在看一下其他信号:empty\channel\error

由于使用了channel信号,所以需要设置maximun channel信号属性。maxinmum channel就是用来说明数据接口支持的最大通道数。

6、Avalon tri-state conduit interface

简称Avalon-TC,它是一个三态导管接口。是为了驱动外围组件地片上控制器而设计地。由于多重外围设备可以通过该接口共享数据,地址核控制引脚,因此它能节约FPGA引脚。一个点到点的接口。

altera提供的关于avalon三态导管接口的IP核:

generic tri-state controller、tri-state conduit bridege、tri-state conduit bridge translator、tri-state conduit pin shaarer

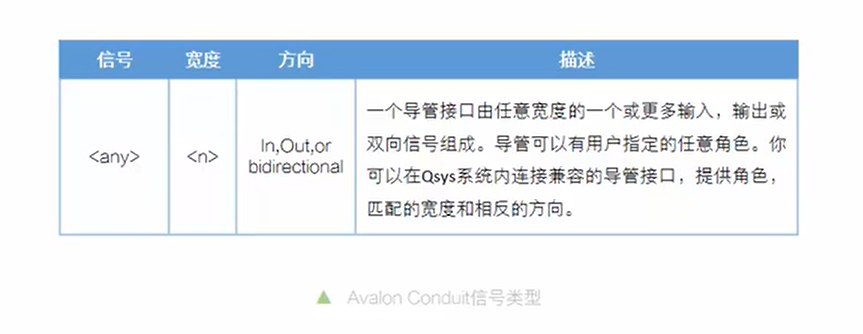

7、Avalon conduit interface

它是一个单纯地导管接口,该接口可以将Qsys系统中地信号或者信号组连接到设计中的其他模块或者FPGA的管教上,比如我们将PIO IP核的引脚引出Qsys系统,然后分配给LED管脚,或者其他FPGA管脚。

属性

--晓凡 2024年3月14日于武汉书