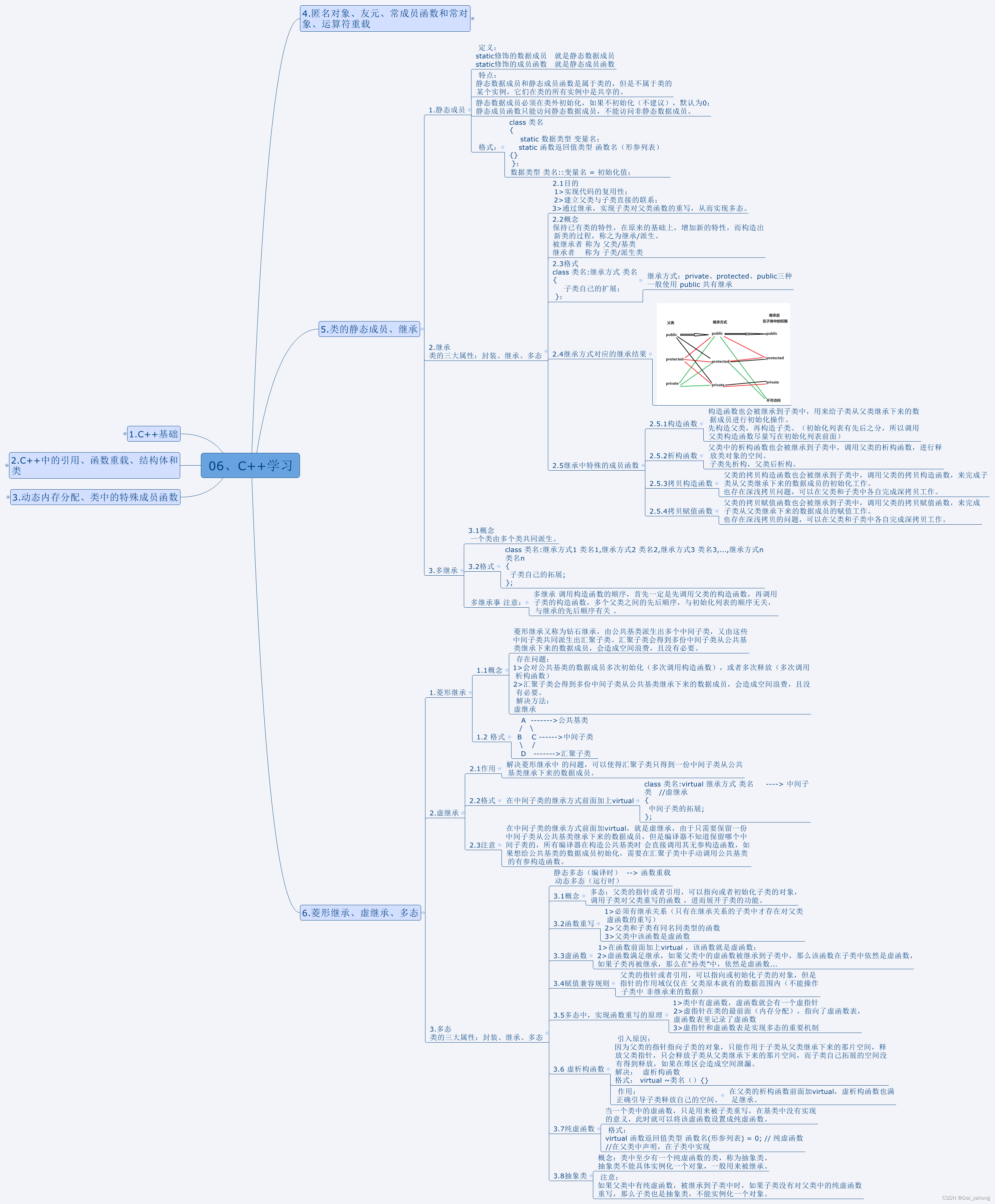

概述

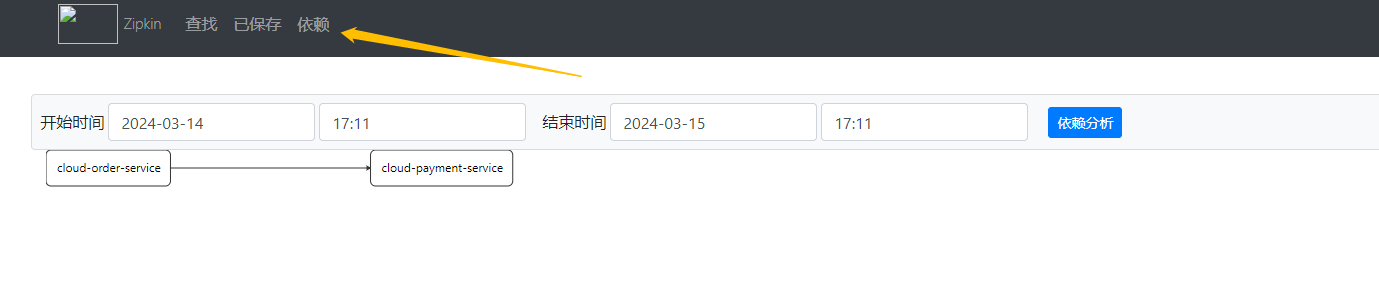

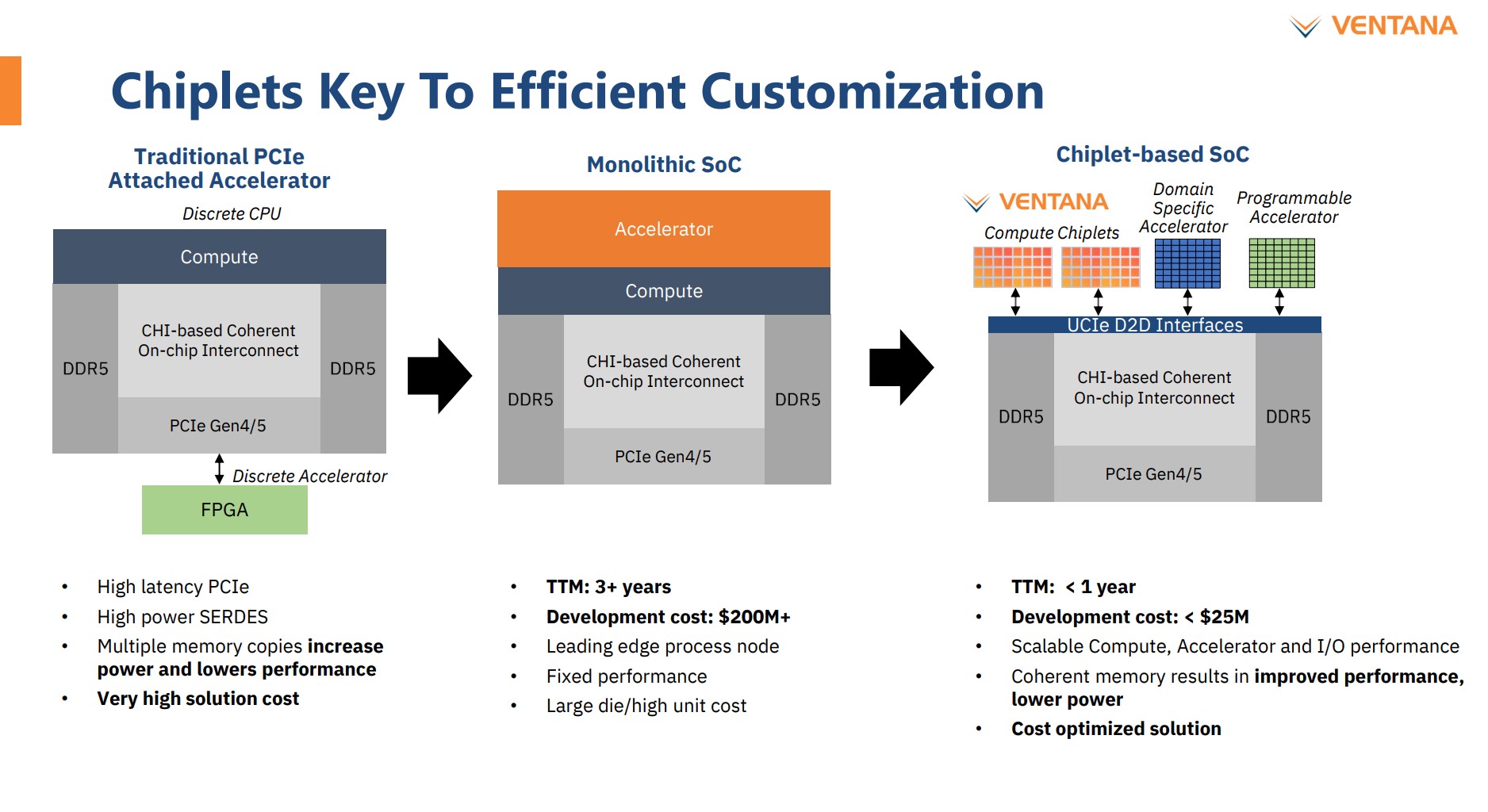

Ventana的产品策略

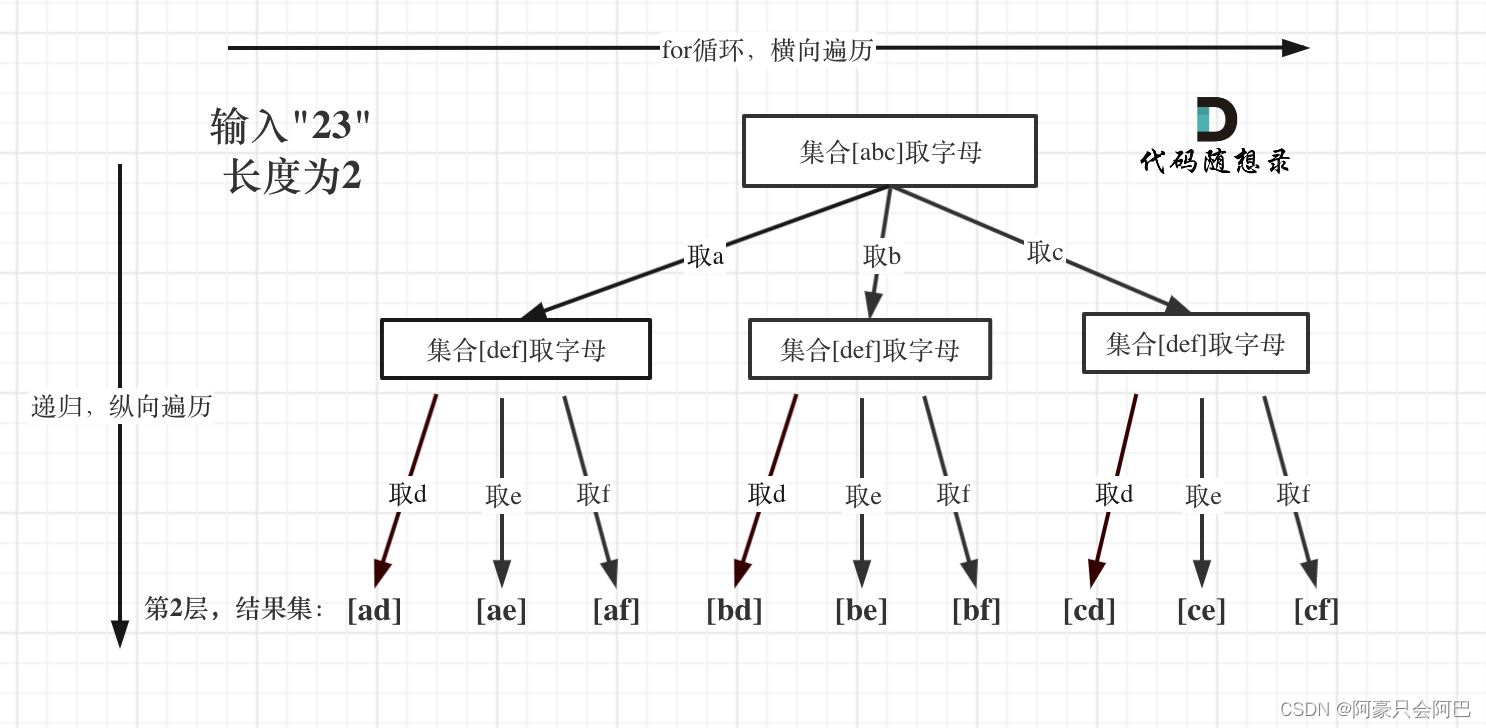

计算die + IO die(友商产品/用户自定义^^)

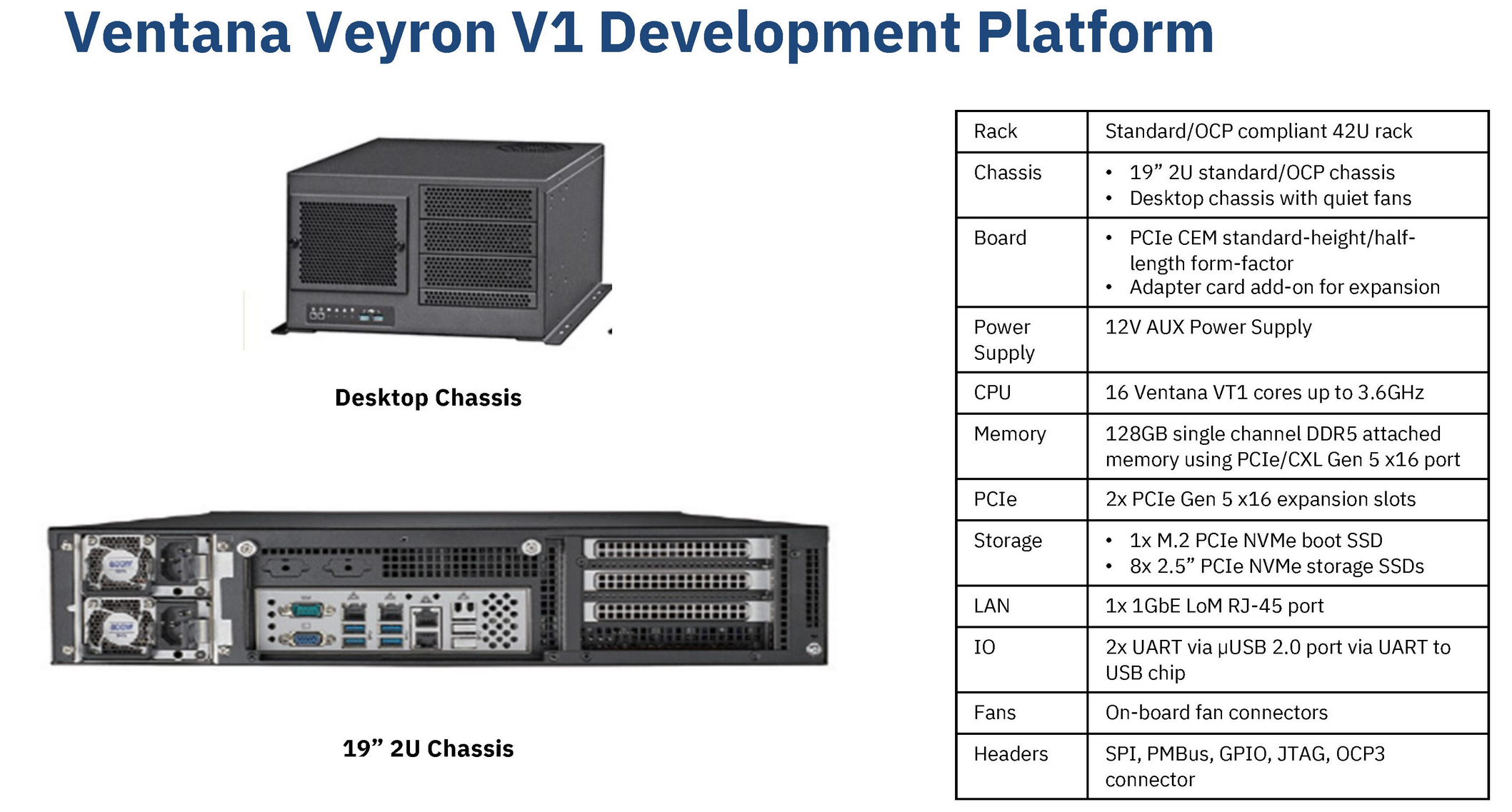

Veyron V1

2022年12月发布,Ventana发布了全球首款基于RISC-V架构的服务器CPU——Veyron V1,号称性能可超越AMD EPYC 7763。

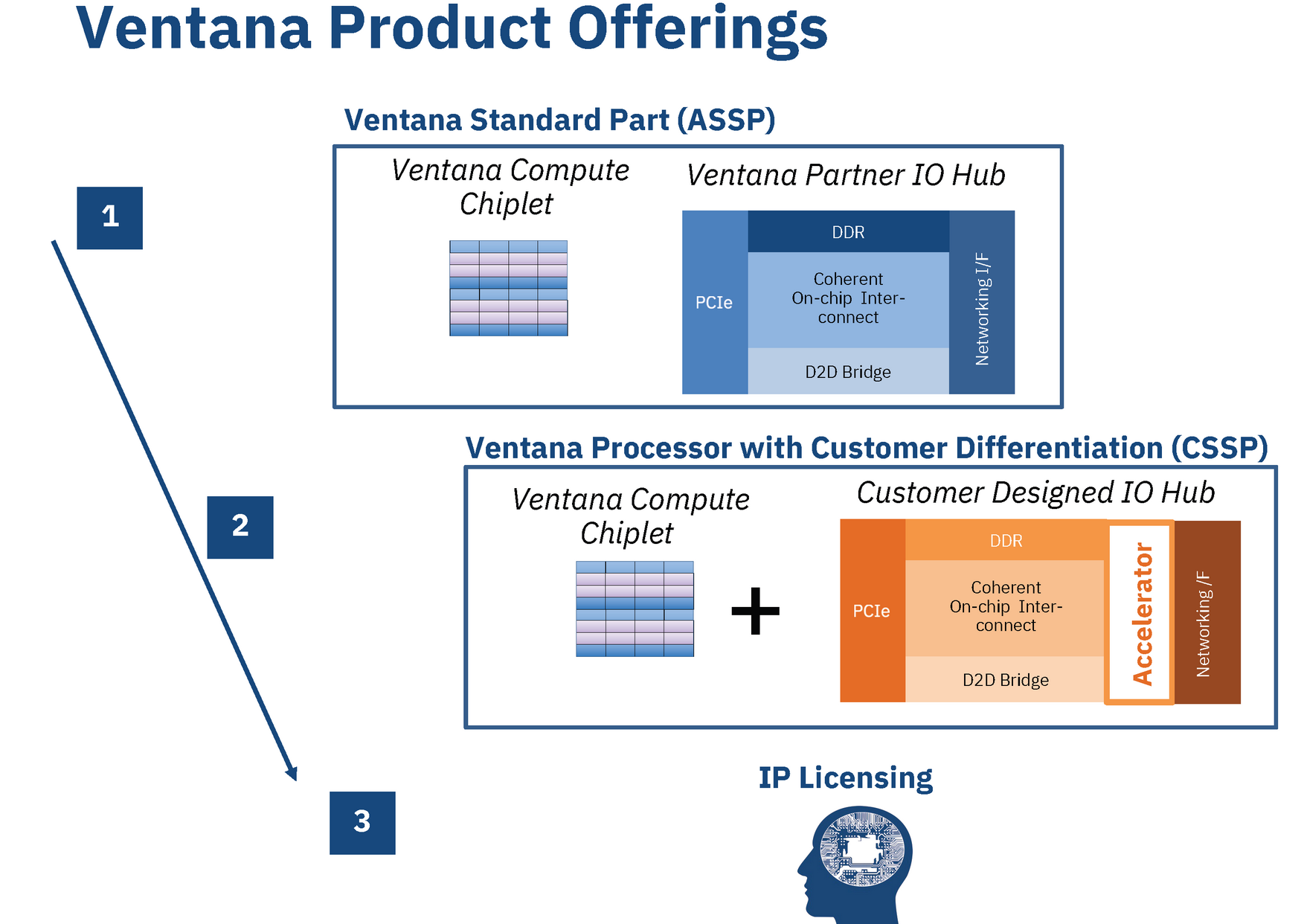

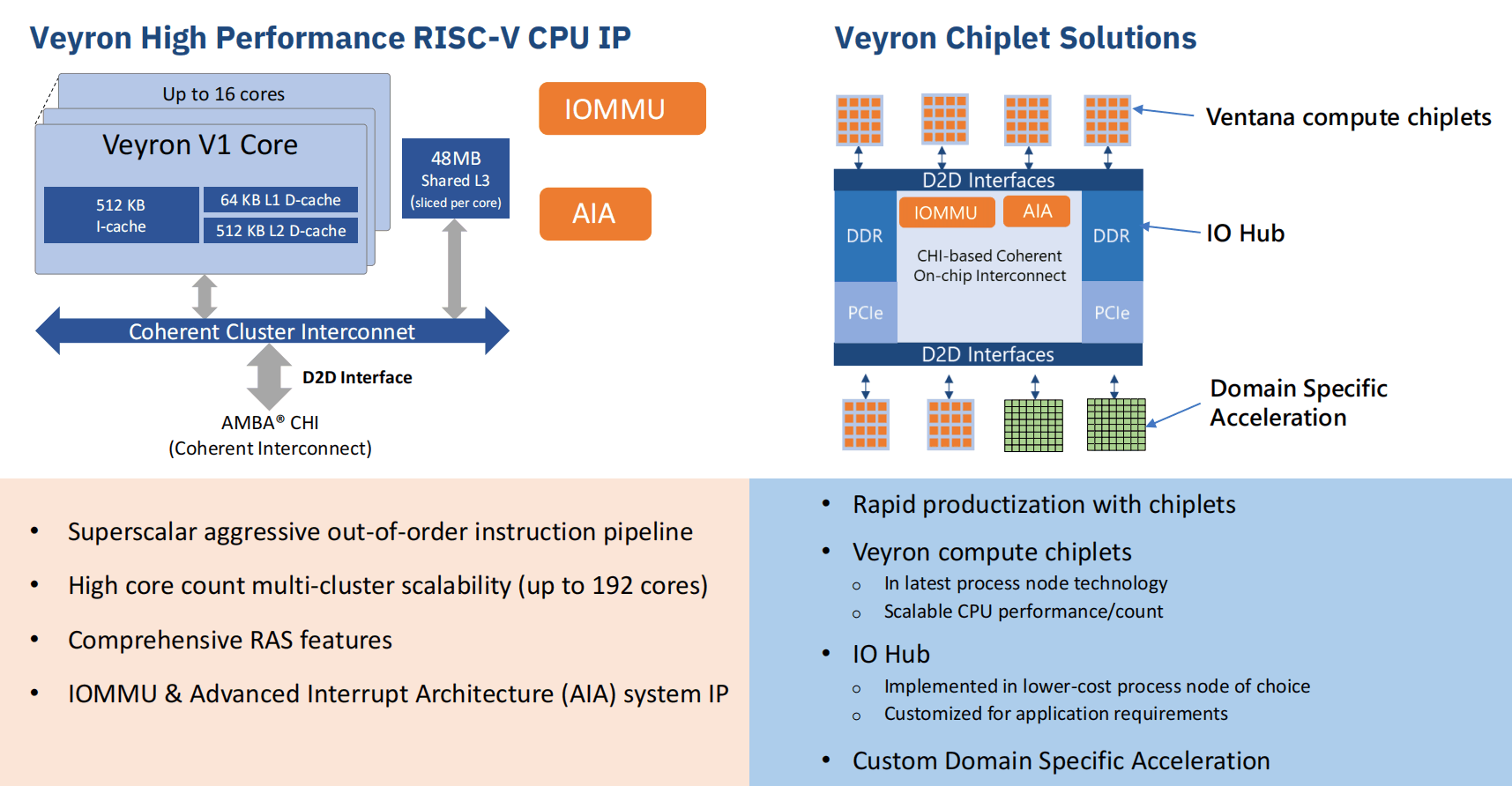

服务器级别的CPU IP + chiplets解决方案

高性能的RISC-V处理器核和chiplet

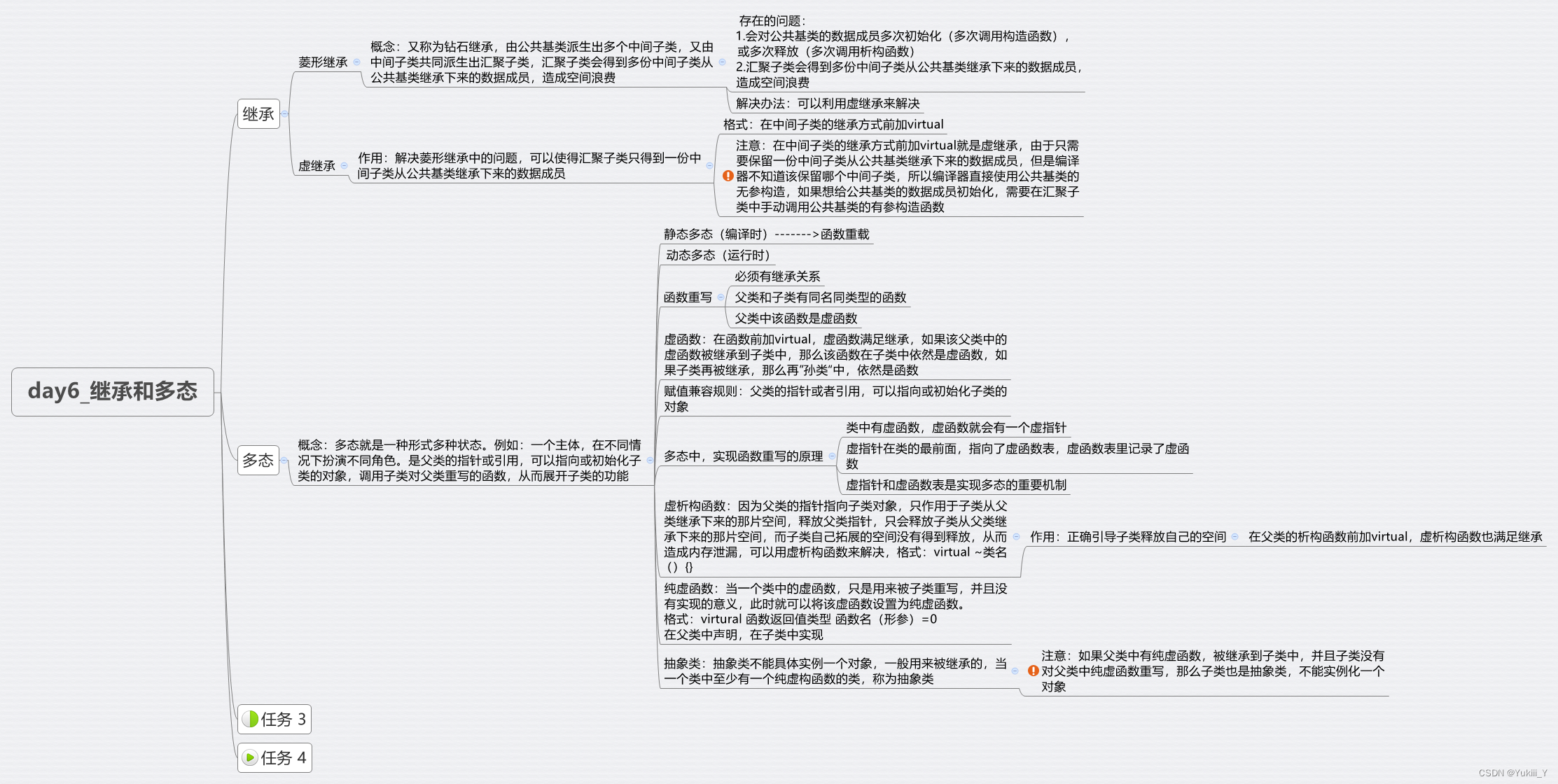

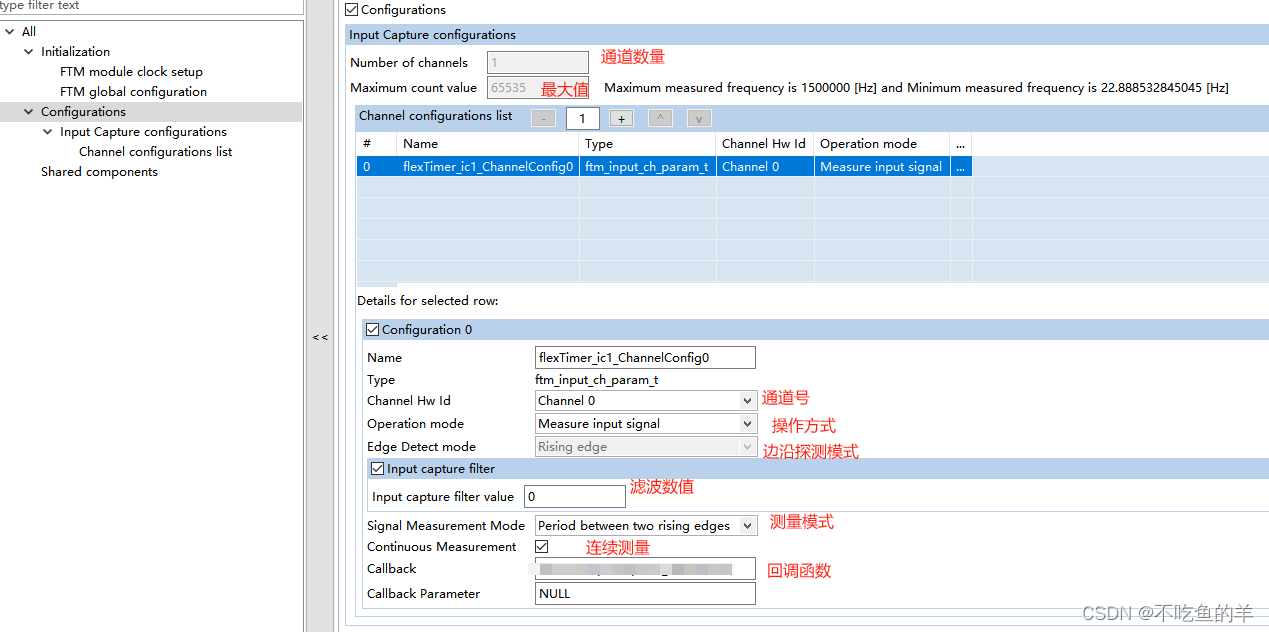

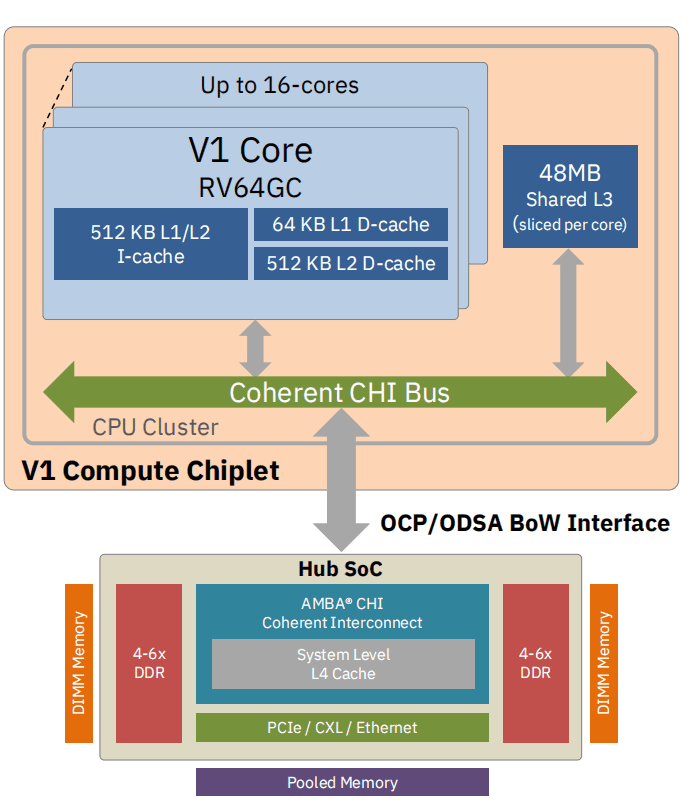

计算die架构

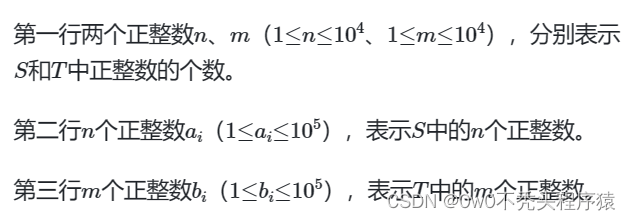

- 16个高性能的RISC-V core

- 每个周期可以译码、分派、执行八条指令

- 高性能的cache架构

- 每个core 1MB L2

- 48MB 每个集群的L3

- 互联接口

- 协议层:一致性的CHI系统集成

- 物理层:BoW D2D IP 、每个方向1Tbps、延迟 <2ns(PHY-to-PHY)、能效<0.5pj/bit

- 先进封装:8-2-8 基板封装,130um microbump

- die面积 62mm2 @TSMC N5

- 高级侧信道攻击缓解措施、IOMMU和高级中断架构(AIA)

- 全面的RAS功能、自上而下的软件性能调整方法

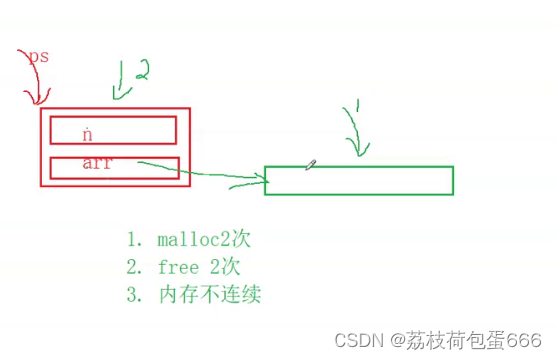

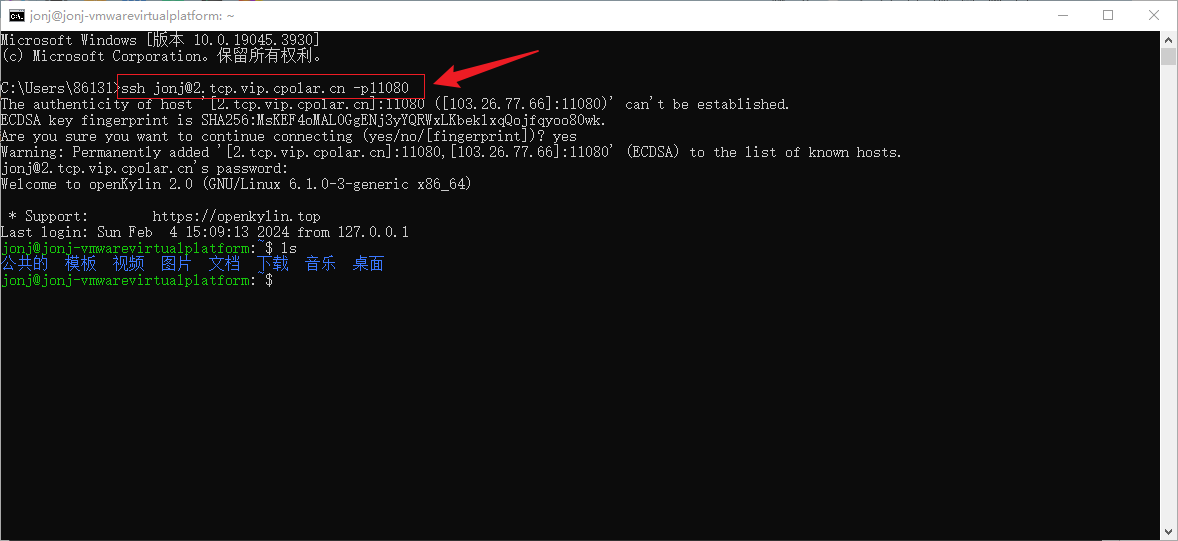

die间互连采用CHI+BoW的协议层物理层的接口

Ventana采用对BoW进行了定制化的设计形成了自己的D2D IP

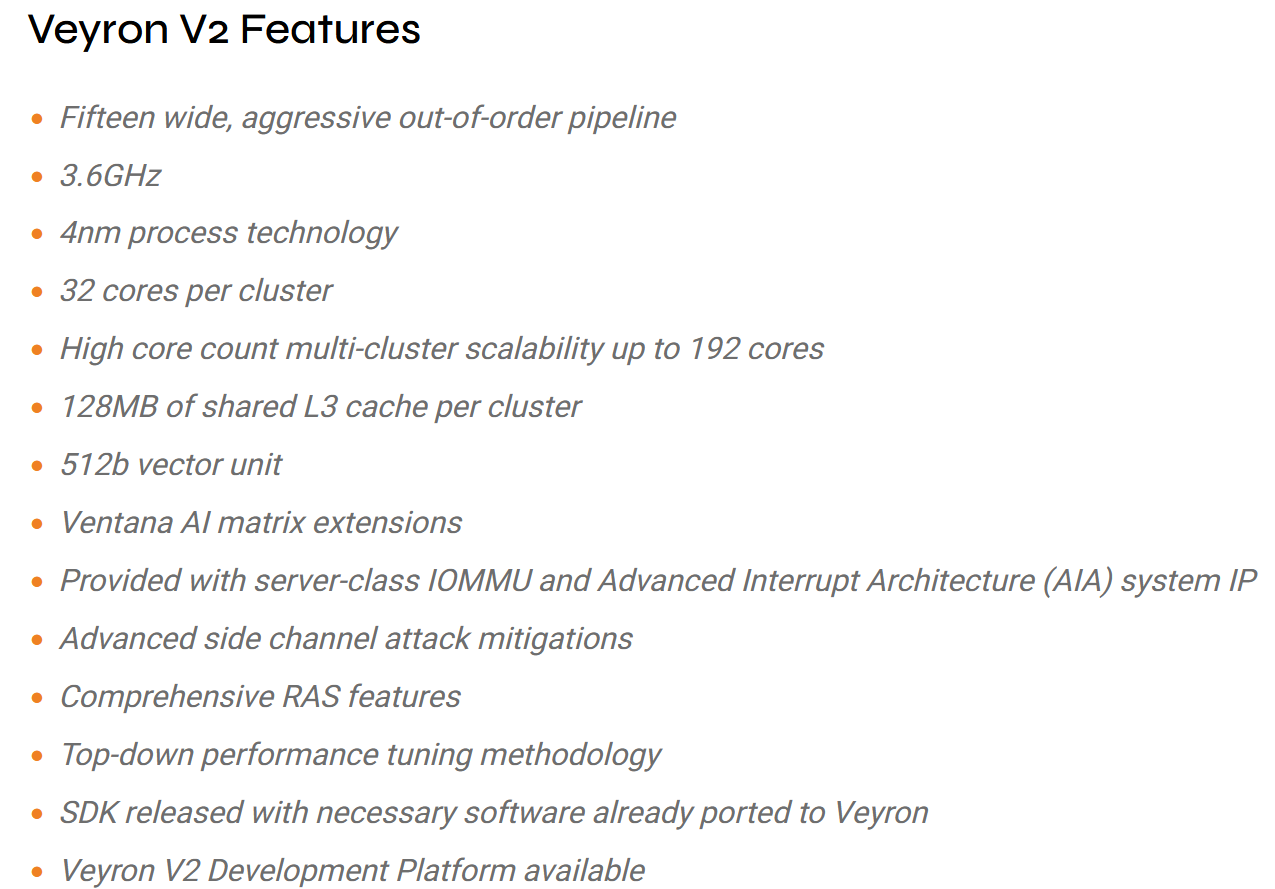

Veyron V2

2023年11月发布,Ventana的第二代riscv高性能CPU,旨在用于数据中心、边缘计算和其他通用计算领域,号称可匹敌AMD Epyc 9754。

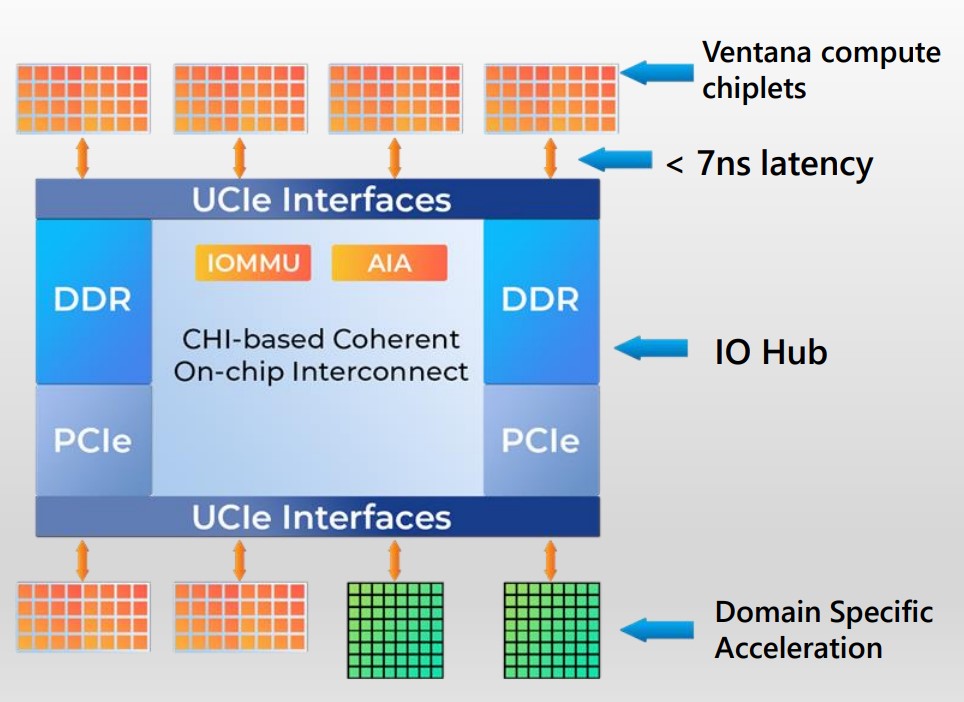

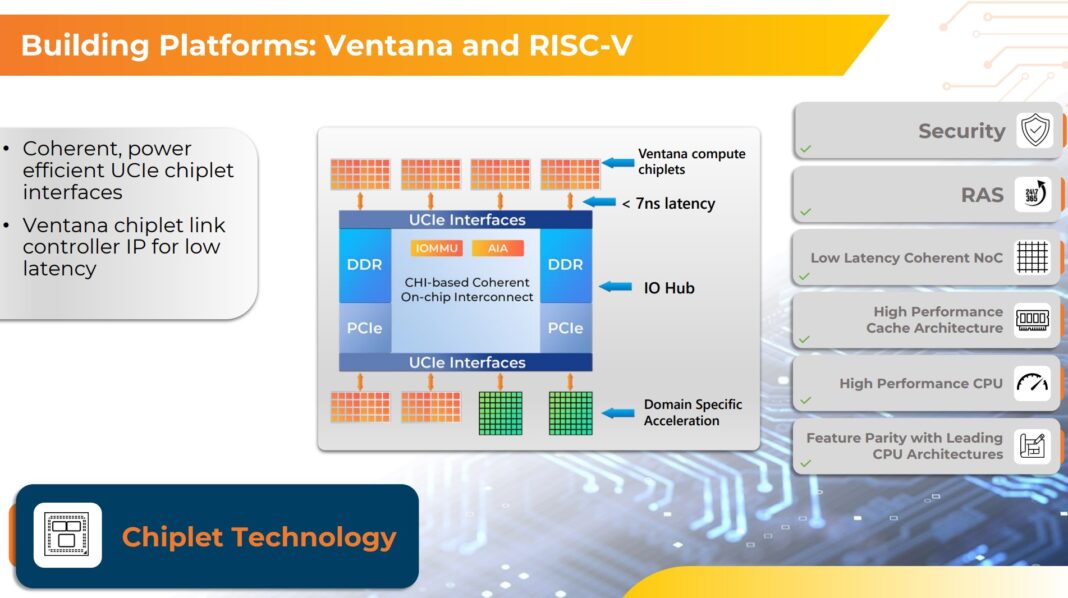

计算die + IO hub的chiplet互联架构

6个计算die叠加IOD可构建192核系统

计算die架构

- 32 cores/单die

- 通过一致性的mesh网络互联,core/io/memory间带宽可达5 TB/s

- 相比V1增加了RISC-V向量扩展,对生成式AI或推理工作负载有很大帮助

- 每个时钟周期可以解码和调度多达15条指令

- 由于其IOMMU设计和高级中断体系结构(AIA),Veyron V2核心可以支持类型1和类型2的服务器虚拟化管理程序以及嵌套虚拟化

- TSMC 4nm

- 互联接口

- 相比上一代,V2采用UCIe,加快拥抱生态(V2在V1后很快推出有此原因6)

chiplet解决方案

参考文献

- Veyron V1 Data Center-Class RISC-V Processor

- Semianalysis: Ventana RISC-V CPUs Beating Next Generation Intel Sapphire Rapids!

- 芯智讯:最强RISC-V服务器芯片发布:4nm,192核,性能超越AMD Epyc 9754!

- Ventana Veyron V2 发布PPT讲解

- 芝能智芯:Ventana Veyron V1 Core分析

- Ventana Launches Veyron V2 RISC-V Into The Datacenter