文档版本:

Video Timing Controller v6.2

PG016 February 26, 2021

IP Facts

Introduction

Xilinx® LogiCORE™ IP Video Timing Controller core是一种通用的视频时序生成器和检测器。该核心通过全面详尽的寄存器集高度可编程,允许控制各种时序生成参数。这种可编程性与一套全面详尽的中断位相结合,这些中断位为实时的处理器系统集成提供了便捷的控制。The Video Timing Controller提供了一个可选的符合AXI4-Lite标准的接口。

Features

- 支持逐行或隔行视频,帧尺寸最高可达16,384 x 16,384。

- 直接再生输出时序信号,具有独立的时序和极性反转。

- 自动检测和生成水平和垂直视频时序信号。

- 支持多种消隐或同步信号组合。

- 自动检测输入视频控制信号的极性。

- 支持检测和生成垂直空白/同步的水平延迟。

- 可编程输出视频信号极性。

- 最多可生成16个额外的独立输出帧同步信号。

- 可选的AXI4-Lite处理器接口。

- 大量的中断和状态寄存器,便于系统控制和集成。

1. Overview

1.1 Navigating Content by Design Process

1.2 Core Overview

所有视频系统都需要管理视频时序信号,这些信号用于同步各个处理过程。视频时序控制器的功能是检测和生成这些时序信号。

该核心的输入侧自动检测水平和垂直同步脉冲、极性、消隐时序和活动视频像素。而在输出侧,它生成与标准视频系统一起使用的水平垂直消隐和同步脉冲,包括支持可编程脉冲极性。这个核心通常与“视频输入至AXI4流”(Video in to AXI4-Stream) 核心一起使用,以检测传入视频数据的格式和时序,或者与“AXI4流至视频输出”(AXI4-Stream to Video out) 核心一起使用,以为下游接收器(如视频显示器)生成输出视频时序。

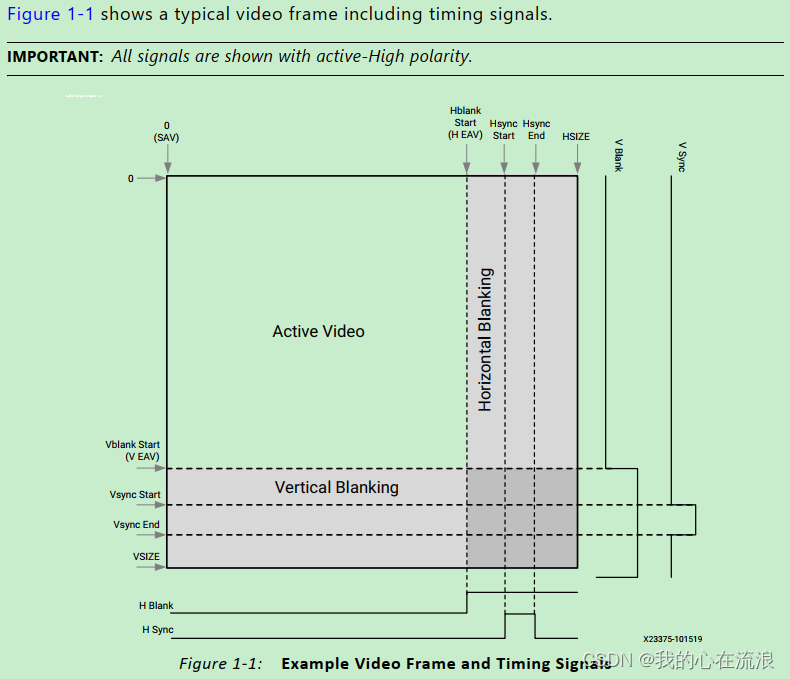

视频帧可以通过少数几个定义在时序上完全描述。一个视频帧包括活动视频和消隐期。垂直和水平同步信号描述了视频帧时序,其中包括活动和消隐数据。此外,帧同步信号可以用来同步视频系统中一个组件到另一个组件的视频数据。还有一些额外的信号也可以用于控制视频系统,例如用于区分有效色度样本的信号。

视频系统可能会利用不同组合的消隐、同步或活动信号以及各种极性来同步处理和控制视频数据。Video Timing Controller通过提供一个高度可编程和灵活的核心,简化了与视频时序信号的工作,它允许在视频系统内检测和生成各种时序信号。

1.3 Feature Summary

Video Timing Controller核心支持AXI4-Lite接口和固定模式接口。AXI4-Lite接口允许该核心被轻松地纳入到Vivado项目中。固定模式接口利用图形用户界面(GUI)可配置的核心参数来设置核心进行固定模式操作。这些可配置选项允许Video Timing Controller核心轻松地与基于AXI4的处理器系统集成,通过一些额外的逻辑也能与非AXI4兼容的处理器系统集成,甚至在没有处理器的系统中也能集成。

Video Timing Controller核心支持检测最大为8192时钟×8192线的视频帧尺寸(包括水平和垂直消隐)。检测通常需要三到五帧输入视频才能完成检测并锁定。Video Timing Controller核心会自动检测与水平/垂直消隐和同步相关的时序。活动视频和活动色度信号的时序也会被检测。这允许用户通过核心寄存器(AXI4-Lite)接口轻松确定视频帧尺寸。用于检测的最小信号集可以是垂直消隐、水平消隐和活动视频,或者是垂直同步、水平同步和活动视频。每个输入信号的极性也会被检测,并通过寄存器接口报告,以便在已知极性后轻松使用每个信号。

该核心还支持生成和重新生成(与检测到的输入匹配)最大为8192时钟×8192线的视频帧尺寸(包括消隐时间)。输出可以是与检测到的输入相同的格式,也可以是不同的格式。这允许检测一个格式并生成另一个不同的格式。输出还可以与检测到的输入同步,并且具有单独的信号极性设置。这允许重新生成具有不同信号极性的输入,或者进行轻微的时序调整(例如延迟或缩短的活动视频)。

Video Timing Controller核心支持多达16个帧同步输出信号。这些信号在每帧期间的一个时钟周期内切换为高电平。这些帧同步信号允许在帧的不同时间触发时序关键的硬件处理过程。

1.4 Applications

1.5 Licensing and Ordering

2. Product Specification

2.1 Standards

视频时序控制器核心符合AXI4-Lite互连标准。

2.2 Performance

2.2.1 Maximum Frequencies

本节包含目标设备的典型时钟频率。可达到的最高时钟频率可能会有所不同。最高可实现的时钟频率和所有资源计数可能会受到其他工具选项、FPGA设备中的额外逻辑、使用不同版本的Xilinx工具以及其他因素的影响。

• Virtex®-7, Kintex®-7, Zynq®-7000(XC7Z030, XC7Z045)设备:225 MHz

• Artix®-7, Zynq-7000(XC7Z010, XC7Z020)设备:150 MHz

• Kintex UltraScale™, Kintex UltraScale+™(XKU035, XCKU15P)设备:400 MHz

• Zynq® UltraScale+™ MPSoC系列:400 MHz

2.2.2 Latency

Video Timing Controller核心不读取或生成数据,因此没有特定的数据延迟。

Video Timing Controller核心监视并生成控制信号。输出控制信号可以配置为与输入相同,同时没有延迟,或者输出信号可以配置为产生多个时钟周期或多行的延迟。

2.2.3 Throughput

Video Timing Controller核心不读取或生成数据,因此没有特定的吞吐量。

2.3 Resource Utilization

2.4 Core Interfaces and Register Space

2.4.1 Port Descriptions

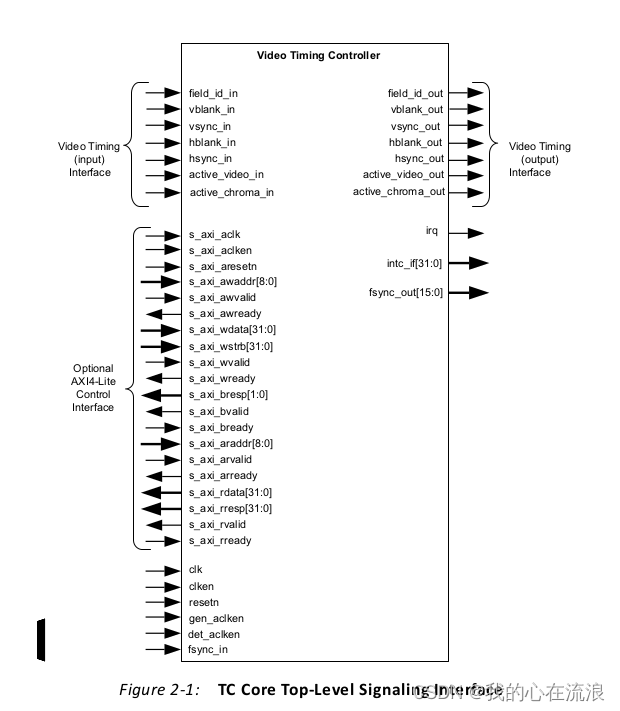

视频时序控制器(VTC)核心使用AXI4-Lite行业标准控制接口连接到其他系统组件。以下部分描述了该核心可用的各种接口。某些信号是可选的,并非在所有核心配置中都存在。仅当通过GUI配置核心并启用AXI4-Lite控制接口时,AXI4-Lite接口和IRQ引脚才会出现。仅当通过GUI配置核心并启用INTC接口时,INTC_IF接口才会出现。图2-1展示了VTC核心的I/O图。

Core Interfaces

Control Interface

视频系统通常使用集成处理器系统来动态控制系统内的参数。当多个独立的图像处理核心集成到一个单独的FPGA中时,这一点尤为重要。视频时序控制器核心可以通过AXI4-Lite接口进行配置。

Common I/O Signals

未包含在AXI4-Lite接口中的信号在表2-1中指定。

clk、clken和resetn、det_clken以及gen_clken信号在核心与视频时序接口之间共享。AXI4-Lite控制接口有其自己的一套时钟、时钟使能和复位引脚:S_AXI_ACLK、S_AXI_ACLKEN和S_AXI_ARESETn。

The clk Pin

视频时序接口必须与核心时钟信号clk同步。所有视频时序接口输入信号都在clk的上升沿采样。所有视频时序输出信号的变化都发生在clk的上升沿之后。如果clk信号没有运行,AXI4-Lite接口会对所有地址断言从错误响应(0x2)。clken引脚是一个高电平有效的同步时钟使能输入,与视频时序接口相关。将clken置为低(取消断言)会停止核心的操作,尽管clk引脚上有上升沿。内部状态会被保持,输出信号电平会维持直到clken再次被断言。当clken被取消断言时,核心输入不会被采样,除了resetn,它优先于clken。这个时钟必须运行才能读取和/或写入AXI4-Lite寄存器,因为所有核心寄存器都位于核心时钟域内。这个时钟使能必须被断言为高电平才能读取和/或写入AXI4-Lite寄存器,因为所有核心寄存器都位于核心时钟域内。如果时钟使能被取消断言,AXI4-Lite接口会对所有地址断言从错误响应(0x2)。

The det_clken Pin

det_clken引脚是一个高电平有效的同步时钟使能,与视频时序控制器检测器(输入)接口相关。这个时钟使能允许独立于生成器暂停检测器。内部检测器时钟使能是clken和det_clken输入的逻辑“与”结果。控制检测器子核心时钟使能的内部逻辑在图2-2中展示。

The gen_clken Pin

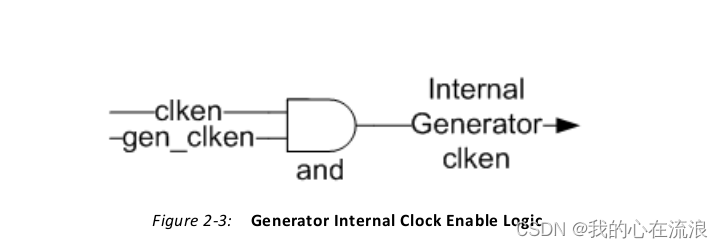

gen_clken引脚是一个高电平有效的同步时钟使能,与视频时序控制器生成器(输出)接口相关。这个时钟使能允许独立于检测器暂停生成器。内部生成器时钟使能是clken和gen_clken输入的逻辑“与”结果。例如,要启用检测器同时暂停生成器,将clken驱动为'1',det_clken驱动为'1',gen_clken驱动为'0'。控制生成器子核心时钟使能的内部逻辑在图2-3中展示。

The resetn Pin

resetn引脚是一个低电平有效的同步复位输入,仅与视频时序接口相关。resetn优先于clken,当resetn设置为0时,即使clken被取消断言,核心也会在下一个clk的上升沿复位。resetn信号必须与clk同步,并且必须至少保持32个最慢时钟周期的低电平。这个复位必须被断言为高电平才能读取和/或写入AXI4-Lite寄存器,因为所有核心寄存器都位于核心时钟域内。如果复位被断言为低电平,AXI4-Lite接口会对所有地址断言从错误响应(0x2)。

The fsync_in Pin

fsync_in引脚是一个高电平有效输入。如果使用,视频时序生成器将与fsync_in输入同步。fsync_in应该每帧只在一个时钟周期内被驱动为高电平。这将重置所有内部生成器计数器,并开始生成与此输入同步的帧时序。在内部,fsync_in引脚与内部帧同步det_fsync逻辑上“或”组合,后者由检测器产生。内部帧同步det_fsync由视频时序检测器生成,可用于将生成器时序与检测器时序同步。其内部逻辑如图2-4所示。如果使用fsync_in输入,则必须禁用检测器。同样,如果使用检测器,则必须将fsync_in引脚驱动为'0'。可以在运行时更改外部fsync_in引脚和检测器的使用,但重要的是fsync_in和det_fsync绝不能同时被断言。

AXI4-Lite Interface

AXI4-Lite接口创建了一个可作为处理器外设轻松添加到Vivado项目中的核心。本节描述了与视频时序控制器AXI4-Lite接口相关的输入/输出信号。

2.4.2 AXI4-Lite Register Set (P19-P38 不再翻译)

AXI4-Lite接口为核心内的所有可编程寄存器提供了内存映射接口。除非另有说明,所有寄存器默认值为核心GUI页面2中指定的值。除非特别指出,所有其他位在上电/复位时默认为0x00000000。

注意:映射概览和完整的寄存器描述包含在下方的表2-4至表2-37中。

3. Designing with the Core

3.1 Basic Architecture

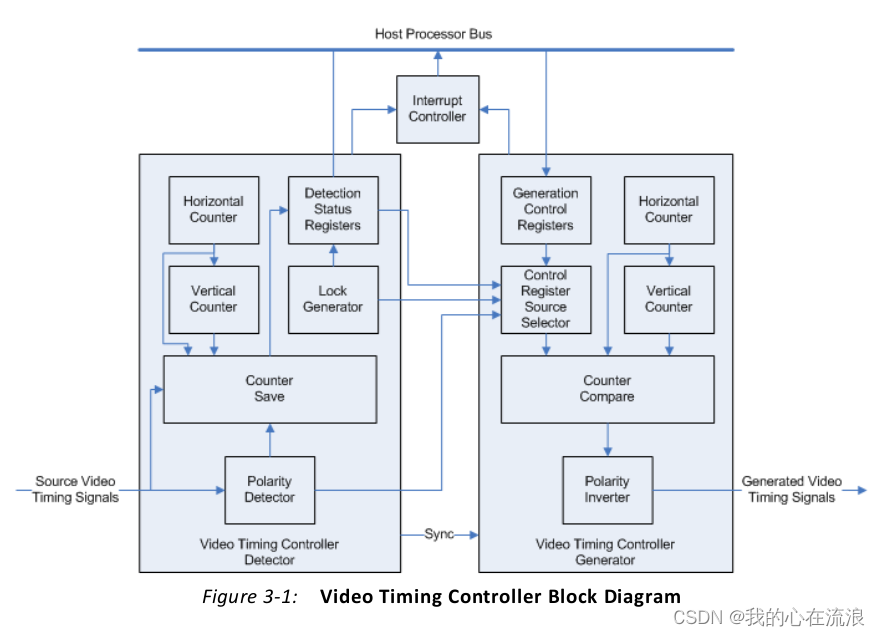

视频时序控制器核心包含三个模块:视频时序检测器、视频时序生成器和中断控制器。见图3-1

在通过GUI实例化时,可以禁用检测器或生成器模块以节省资源。

3.2 Control Signals and Timing

视频时序控制器的输入和输出在以下部分进行讨论,并通过时序图展示。

消隐和有效视频周期的定义在第1章概述中讨论过。除了这些定义外,从消隐开始(或有效视频结束)到同步开始的时期被称为前沿。从同步结束到消隐结束(或有效视频开始)的时期被称为后沿。总的水平周期(包括消隐和有效视频)也可以定义,类似地还有总的垂直周期。

图3-2显示了水平前沿的开始(Hblank Start)、同步(Hsync Start)、后沿(Hsync End)和有效视频(SAV)。它还显示了垂直前沿的开始(Vblank Start)、同步(Vsync Start)、后沿(Vsync End)和有效视频(SAV)。水平时钟周期的总数是HSIZE,行数的总数是VSIZE。

这些视频帧周期的定义用于视频时序检测和视频时序生成。

重要说明:请注意,在视频时序控制器中不存在视频数据和视频时序的每时钟像素数。视频数据总线只有一组定时信号。这意味着水平时序设置只能检测和生成系统配置中每时钟像素数的倍数。例如,给定一个有效行为1920的视频格式,系统配置有一个以4像素/时钟运行的视频数据总线,那么检测到和生成的有效行时序将是(1920像素 / 4像素/时钟)= 480时钟周期。同样,所有其他水平分量(即hsync, hblank)也会受到影响,而垂直分量不会改变。

3.2.1 Video Timing Detection

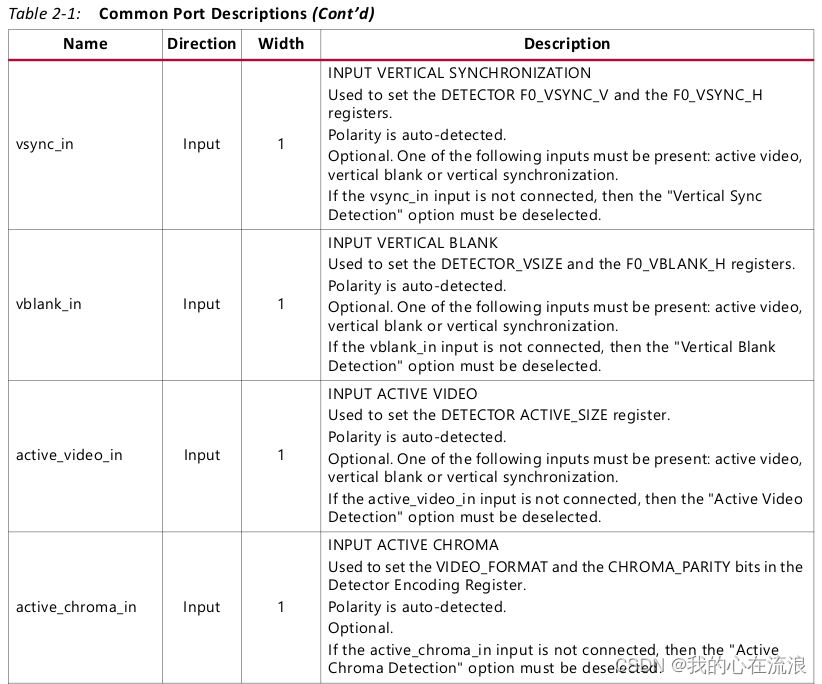

视频时序控制器有六个可选输入,用于检测输入视频信号的时序:垂直消隐、垂直同步、水平消隐、水平同步、有效视频和活动色度。检测所需的最小输入集是垂直消隐、水平消隐和有效视频,或者垂直同步、水平同步和有效视频。要启用检测,必须设置“启用检测”GUI参数,并且控制寄存器的第1位也必须设置。GUI参数允许节省FPGA资源。控制寄存器允许运行时的灵活性。其他GUI参数可以被设置来选择性地禁用一个或多个输入视频时序信号的检测。

每个输入信号的检测极性由检测极性寄存器(地址偏移0x2C)的位0-5显示。高表示高电平有效极性,低表示低电平有效极性。检测编码寄存器的位8和位9显示了每条活动色度线之间跳过的线条数。位8为高表示每两条线跳过一条(4:2:0),位8为低表示没有跳过任何线(4:4:4或4:2:2)。位9为高表示每个像素跳过一个,位9为低表示没有跳过任何像素。

如果任何输入(vblank_in, vsync_in, hblank_in, hsync_in, active_video_in, active_chroma_in)没有被驱动或没有连接,那么必须禁用该输入的检测。要禁用一个输入的检测,请在GUI中取消选择相应的选项(“垂直消隐检测”,“垂直同步检测”等)。

为了使核心能够正确检测输入时序并重新生成,必须提供一组最小信号集。您必须在核心接口的时序检测部分选择这些信号,并在连接核心时提供这些信号。您可以使用活动色度选项与下面列出的任何组合。如果您提供以下输入,该选项可以重新生成垂直消隐、水平消隐和有效视频:

• 垂直同步、水平同步和有效视频

• 垂直消隐、水平消隐、垂直同步、水平同步和有效视频

3.2.2 Video Timing Generation

视频时序控制器能够生成多达六个输出视频信号:垂直消隐、垂直同步、水平消隐、水平同步、有效视频和活动色度。要启用这些信号的生成,必须设置“启用生成”GUI参数,并且控制寄存器的位0或位2也必须设置。其他GUI参数可以被设置来选择性地禁用一个或多个视频时序信号的生成。

每个输出信号的极性可以通过生成器极性寄存器(地址偏移0x006C)的位0-5来设置。高表示高电平有效极性,低表示低电平有效极性。控制寄存器的位8和位9也设置了每条活动色度线之间跳过的线条数。位8为高表示每两条线跳过一条(4:2:0),位8为低表示没有跳过任何线(4:4:4或4:2:2)。位9为高表示每个像素跳过一个,位9为低表示没有跳过任何像素。

视频时序控制器在控制寄存器中有称为源选择的位,用于选择内部检测寄存器或外部输入生成寄存器。这些位允许被检测到的时序(如果启用)控制生成的输出,或者允许主机处理器通过地址偏移0x0060 - 0x0084处的生成寄存器独立地覆盖每个值,如表2-3所述。

表3-1至表3-6显示了输入控制总线的示例设置和结果视频时序输出信号。

不支持在帧的最后一行将VBLANK取消断言与HBLANK同时发生。典型的用例是在HBLANK断言的同时VBLANK取消断言。然而,与此最接近的配置可能会偏离1个时钟周期。您可以配置VBLANK在帧的最后一行HBLANK取消断言前一个时钟周期取消断言。通过设置VBLANK结束来实现这一点:

(F0_VBLANK_HEND) = HFRAME_SIZE - 1

Horizontal Generation Configuration Example

Vertical Generation Configuration Example

Vertical Generation Configuration Example with Active Chroma for YUV 4:2:0

Active for Even Lines

Vertical Generation Configuration Example with Active Chroma for YUV 4:2:0

Active for Odd Lines

Timing Regeneration Example with Selective Signals Overridden

3.2.3 Synchronization

视频时序输出信号的生成可以与检测到的视频时序输入信号同步,或者通过设置控制寄存器中的SYNC_ENABLE字段或选择GUI选项来独立生成,以将发生器与检测器或fsync_in同步。同步允许发生器跟随检测器的相位。将输出同步到输入允许开发者用不同的设置覆盖每个单独的时序信号,例如信号极性或开始时间。例如,可以将活动视频信号重新生成,提前或推迟一个周期。这提供了一种灵活的方法,可以在保持与输入时序同步的同时,用不同的设置重新生成视频时序输出信号。

视频时序控制器还有一个称为自动生成模式的GUI参数,用于根据检测到的输入控制生成输出的行为。当设置了自动生成模式参数时,生成的视频时序输出将基于检测到的输入而变化。如果此参数未设置,那么视频时序输出将仅基于首次检测到的输入格式生成。(如果检测器失去锁定,生成的输出将继续产生。)要在设置了自动生成模式的情况下改变输出时序,必须首先通过清除控制寄存器的位1来禁用时序检测,然后重新启用,如果任何源选择位为低的话。

3.2.4 Frame Syncs

视频时序控制器具有帧同步输出总线。每个位可以被配置为在每个视频帧期间的任何一个时钟周期内切换为高电平。每个位都可以通过帧同步配置寄存器(地址偏移0x0100 - 0x013c)独立配置水平和垂直时钟周期位置。

3.2.5 Interrupts

视频时序控制器有一个名为"irq"的活跃高电平中断输出端口。当中断发生时,此输出被设置为高电平,并在中断事件清除后设置为低电平。视频时序控制器还包含三个32位寄存器,用于配置和报告中断状态:中断状态/清除、中断启用和中断清除寄存器。中断输出被设置为高电平是通过在中断启用寄存器和中断状态寄存器上执行逻辑与操作来实现的。中断清除寄存器用于清除中断状态寄存器。向中断状态寄存器中的某一位写入'1'将清除相应的中断(当设置时)。向已清除的位写入'1'将没有任何效果。

3.3 Use Model

本节说明了Xilinx视频时序控制器核心的可能使用场景。

图3-8展示了视频时序控制器在视频系统中使用的四个特性:

• 源视频帧时序的检测

• 视频时序信号的产生

• 生成两个帧同步信号以控制视频处理器

• 通过AXI4-Lite接口与主机处理器连接

为了检测源视频的时序,时序信号被连接到视频时序控制器检测模块。时序信号的时序和信号极性都被捕获,并且可以被主机处理器轻松读取。

视频时序信号被生成以控制AXI4-Stream到Video-Out模块和外部显示器。这些输出信号的时序由主机处理器控制。视频时序控制器可以实时配置以复制源视频格式,或者在输出上稍微改变格式,例如,在输入信号为正极性而显示器需要负极性同步信号的情况下。视频时序控制器也可以实时重新配置,以输出与输入源完全不同的格式。

两个帧同步输出被生成以控制视频处理器1和视频处理器2。这些输出可以用于控制视频处理器2相对于视频处理器1开始处理的时间。这些帧同步也可以实时重新配置。

在这个例子中,视频时序控制器连接到一个主机处理器。AXI4-Lite接口允许状态/控制寄存器与主机处理器之间轻松连接。此外,视频时序控制器的中断输出也可以用来同步软件与硬件事件。

如果视频系统要求从Video-In To AXI4-Stream core只发送完整的视频帧,则必须配置视频时序控制器以用INTC_IF总线的第8位驱动axis_enable输入。必须通过“Include INTC Interface”来启用这个总线。

图3-9展示了视频时序控制器将时序发生器同步到输入帧同步、垂直同步或垂直消隐信号的能力。这对于生成不存在的时序信号非常有用。例如,如果可以从同步信号生成消隐信号。此外,这允许时序发生器与另一个时序发生器同步。

在这个例子中,底部的时序发生器可以与顶部的时序控制器、单独的vsync或单独的vblank信号同步。这是由多路复用器“Select”信号控制的。

重要:通过配置发生器全局延迟寄存器(地址偏移0x140)可以使时序发生器从输入偏移。

一旦选择了fsync_in输入,就可以使用发生器全局延迟寄存器配置同步发生器的像素或行偏移延迟。

3.4 Clocking

视频时序控制器核心有两个时钟源,CLK和S_AXI_ACLK,分别对应各自的时钟域。视频时序控制器核心还有四个时钟使能源:CLK、DET_CLKEN、GEN_CLKEN以及S_AXI_ACLKEN。

CLK

输入和输出视频时序接口使用CLK时钟信号作为它们共同的时钟参考。

S_AXI_ACLK

AXI4-Lite接口使用S_AXI_ACLK引脚作为其时钟源。CLK引脚并不在AXI4-Lite和视频时序接口之间共享。视频时序控制器核心包含CLK(视频时序)和S_AXI_ACLK(AXI4-Lite)时钟域之间的跨时钟域逻辑。即使视频处理因RESETn、CLKEN或视频时钟不运行而停滞,该核心也会自动确保AXI4-Lite事务的完成。

尽管核心确保了AXI-Lite事务的完成,但更好的设计是尽可能避免这种情况,并且只在有视频时钟存在时才访问AXI-Lite接口。

CLKEN

视频时序控制器核心具有多个启用选项:CLKEN引脚(硬件时钟使能)以及通过AXI4-Lite控制接口提供的软件启用选项(如果存在)。

CLKEN引脚不能在内部确保与视频时序处理的同步,因此长时间的解除断言CLKEN可能会导致生成不完整的帧或延长检测输入视频帧时序所需的周期。

CLKEN引脚促进:

DET_CLKEN

视频时序控制器核心还有一个独立的时钟使能输入引脚来控制检测器。这个时钟使能允许独立于发生器暂停检测器。

GEN_CLKEN

视频时序控制器核心还有一个独立的时钟使能输入引脚来控制发生器。这个时钟使能允许独立于检测器暂停发生器。

S_AXI_ACLKEN

S_AXI_ACLKEN仅是AXI4-Lite接口的时钟使能信号。将此信号驱动为低电平只会影响AXI4-Lite接口,并不会停止CLK时钟域中视频时序处理的运行。

3.5 Resets

视频时序控制器核心有两个复位引脚,RESETn和S_AXI_ARESETn,分别对应于每个时钟域。这两个复位都是低电平有效(active-Low)。

RESETn

视频时序控制器核心有两个复位源:RESETn引脚(硬件复位)和通过AXI4-Lite控制接口提供的软件复位(如果存在)。软件复位可通过地址偏移0x0000处的控制寄存器,位31进行访问。

重要提示:RESETn不会在内部与视频时序处理同步。如果在处理帧时序时解除RESETn的断言,可能导致生成的帧不完整。

外部复位脉冲需要至少保持32个CLK周期以重置核心。RESETn信号仅重置视频时序接口和核心的处理。AXI4-Lite接口不受RESETn信号影响,以便在不停止AXI4-Lite接口的情况下重置视频时序处理核心。然而,如果在AXI4-Lite寄存器读取或写入期间RESETn被置为低电平,AXI4-Lite接口会对所有地址断言从设备错误响应(0x2)。

重要提示:当一个具有多个时钟和相应复位信号的系统正在被重置时,复位发生器必须确保所有信号都被足够长时间地置位/解除置位,以正确重新初始化所有接口和时钟域。

S_AXI_ARESETn

S_AXI_ARESETn信号与S_AXI_ACLK时钟域同步,但在内部与CLK时钟域进行同步。S_AXI_ARESETn信号会复位整个核心,包括AXI4-Lite和视频时序接口。

3.6 Protocol Description

视频时序控制器核心寄存器接口符合AXI4-Lite接口规范。