目录

一 协处理器的作用与功能

1.计数寄存器和比较寄存器

2.Status寄存器

3.Cause寄存器(标号为13)

4.EPC寄存器(标号为14)

5.PRId寄存器(标号为15)

6.Config 寄存器(标号为16)-配置寄存器

二 协处理器的实现

三 协处理器访问指令说明

四 具体实现

1.译码阶段

2.执行阶段

一 协处理器的作用与功能

我们之前实现的指令操作很多都是算术操作,CPU还需要进行一些指令集扩展的操作,比如系统控制与浮点单元计算等。MIPS架构定义了四种协处理器如下:

我们在这里只实现CP0的主要功能中的中断异常处理,它还可以进行工作状态的配置如大小端模式的切换,高速缓存控制,存储管理单元控制等。

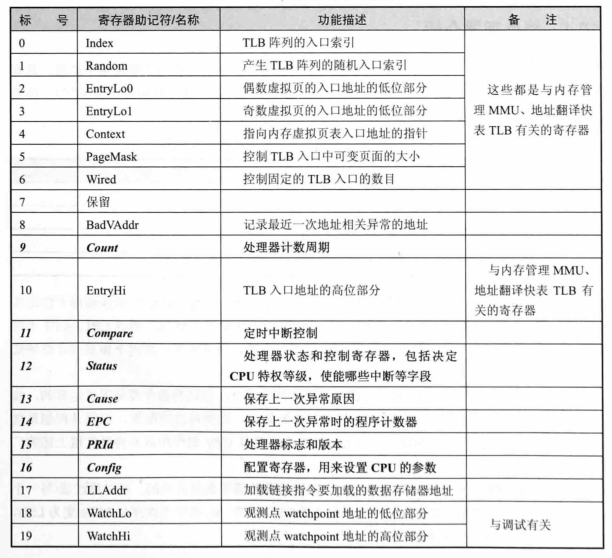

协处理器中为每种功能定义了相应的32个32位的寄存器,主要是通过读写协处理器中的寄存器去实现相关功能。

我们的目标是实现中断异常管理以及最基本的工作状态的配置,只需要关注上面标黑的寄存器即可。

1.计数寄存器和比较寄存器

定时中断的实现是通过Count计数器寄存器和Compare寄存器来实现的。

Count寄存器是一个不停计数的32位寄存器,计数频率一般与CPU时钟频率相同,当计数达到32位无符号数的上限时,会从0开始重新计数。Count 寄存器可读、可写。

Compare寄存器是一个32位的寄存器,与Count寄存器一起完成定时中断功能。 当Count寄存器中的计数值与Compare寄存器中的值一样时, 会产生定时中断。这个中断会一直保持,直到有数据被写入Compare寄存器。Compare 寄存器可读、可写。

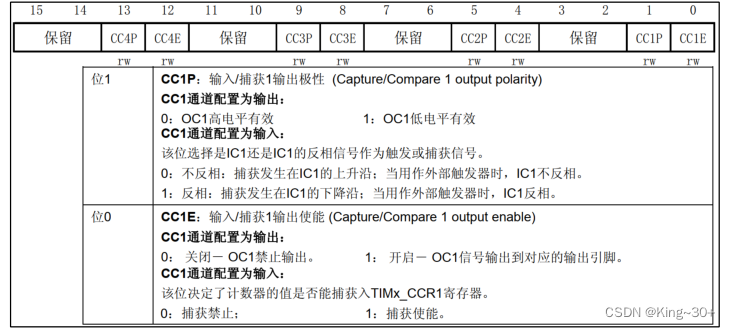

2.Status寄存器

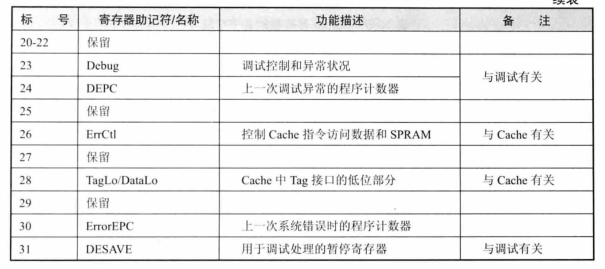

Status寄存器也是一个32位、可读、可写的寄存器,用来控制处理器的操作模式、中断使能以及诊断状态。这里我们主要进行中断使能和基本工作状态的配置。

CU3-CU0表示协处理器是否可用(Coprocessor Usability), 分别控制协处理器CP3、CP2、 CPI、

CP0。为0时,表示相应的协处理器不可用;为1时,表示相应的协处理器可用。对于OpenMIPS

处理器而言,只有协处理器CPO,所以可以设置本字段为4'b0001。

IM7-IM0表示是否屏蔽相应中断(Interrupt Mask), 0表示屏蔽,1 表示不屏蔽,MIPS处理器可以

有8个中断源,对应IM字段的8位,其中6个中断源是处理器外部硬件中断,另外2个是软件中断。

中断是否能够被处理器响应是由Status寄存器与Cause寄存器共同决定的,如果Status寄存器的IM字段(中断源选择)与Cause寄存器的IP字段(外部中断挂是否发生)的相应位都为1,而且Status寄存器的IE字段(全局使能中断)也为1时,处理器才响应相应中断。

EXL表示是否处于异常级(Exception Level), 当异常发生时,会设置本字段为1,表示处理器处于异常级,此时,处理器会进入内核模式下工作,并且禁止中断。

IE表示是否使能中断(Interrupt Enable),这是全局中断使能标志位。为1表示中断使能,为0表示中断禁止。

3.Cause寄存器(标号为13)

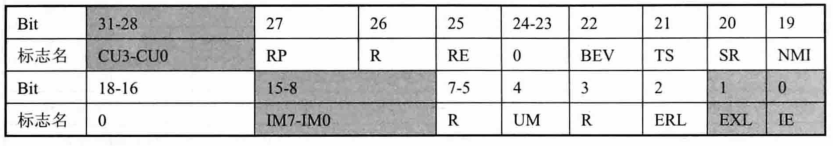

Cause寄存器主要记录最近一次异常发生的原因,也控制软件中断请求。Cause寄存器的各字段如表10-6所示,除了IP[1:0]、 IV和WP,其余字段都是只读的。

4.EPC寄存器(标号为14)

EPC是异常程序计数器(Exception Program Counter),用来存储异常返回地址,一般情况下,存储发生异常的指令的地址,但是,如果发生异常的指令位于延迟槽中,那么EPC存储的是前一条转移指令的地址。因为之前我们定义,延迟槽中的指令就是转移指令之后的指令并且一定执行。所以异常真正发生在转移阶段。

5.PRId寄存器(标号为15)

PRId寄存器是处理器标志( Processor Identifier)寄存器,包含的信息有:制造商信息、处理器类型以及处理器的版本等。各个字段如表10-9所示。其中R是保留字段。

6.Config 寄存器(标号为16)-配置寄存器

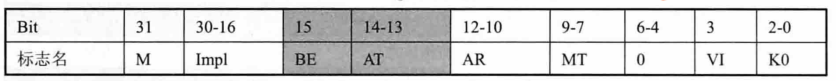

Config寄存器包含了与处理器有关的各种配置和功能信息,其各个字段如下所示,大部分字段由硬件在重启时进行初始化,或定为常量。

BE

其值为1表示处理器工作在大端模式(MSB),为0表示处理器工作在小端模式(LSB)。OpenMIPS处理器工作在大端模式,所以设置本字段为1。

AT

指令集架构类型(Architecture Type)字段,当其值为2'b00时,表示MIPS32架构。

现在我们可以整理一下中断的实现操作:

中断分为外部中断和定时中断

定时中断的实现是通过Count计数器寄存器和Compare寄存器来实现的。

Count寄存器是一个不停计数的32位寄存器,计数频率一般与CPU时钟频率相同,当计数达到32位无符号数的上限时,会从0开始重新计数。Count 寄存器可读、可写。

Compare寄存器是一个32位的寄存器,与Count寄存器一起完成定时中断功能。 当Count寄存器中的计数值与Compare寄存器中的值一样时, 会产生定时中断。这个中断会一直保持,直到有数据被写入Compare寄存器。Compare 寄存器可读、可写。

外部中断是否能够被处理器响应是由Status寄存器与Cause寄存器共同决定的,如果Status寄存器的IM字段(中断源选择)与Cause寄存器的IP字段(外部中断挂是否发生)的相应位都为1,而且Status寄存器的IE字段(全局使能中断)也为1时,处理器才响应相应中断。

二 协处理器的实现

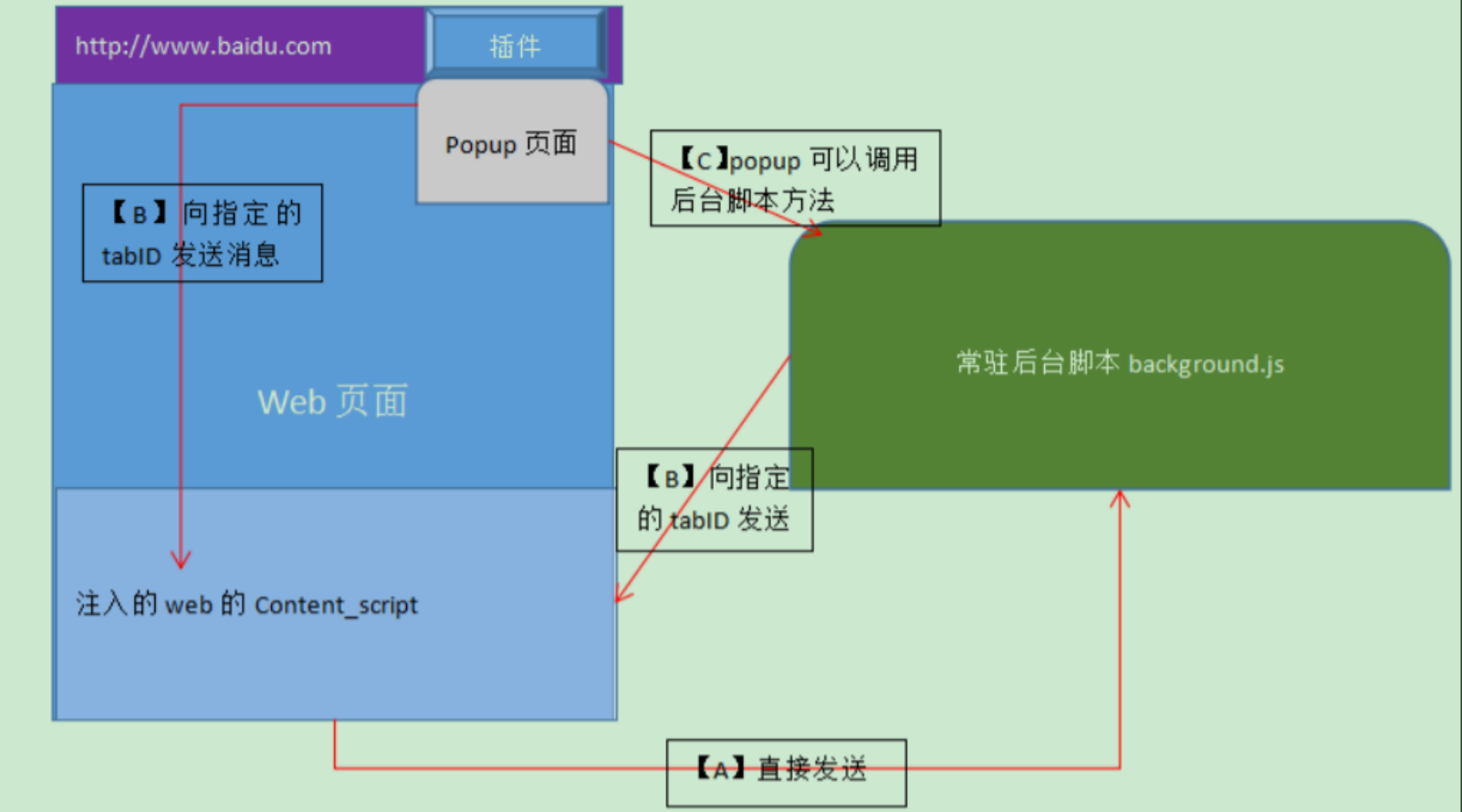

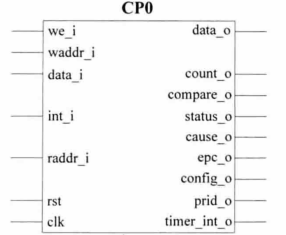

之前说过对协处理器指令实现操作本质就是去读写协处理器,所以接口类似于一个单端口的存储器,包括读写使能,读写地址,输出寄存器和外部中断的输入。

先对寄存器做初始化,主要是对工作状态寄存器进行基本赋值:

读写操作按照读写地址进行赋值,寄存器地址按照之前的表按地址号进行定义。

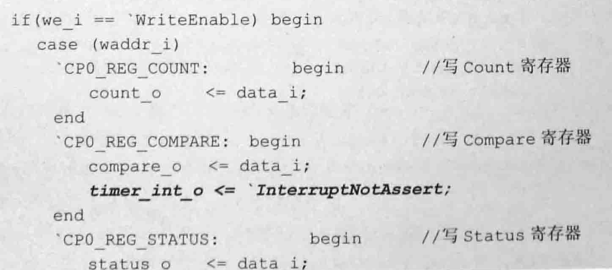

写操作:

对计数器和比较寄存器进行读写之前先实现他们的基本操作定义输出信号,计数器需要一直计数,cause保留外部中断请求,其值与外部中断输入一致,定时中断请求的输出:

需要注意当写入比较寄存器时,定时中断结束。以及有些寄存器并不是可写的。

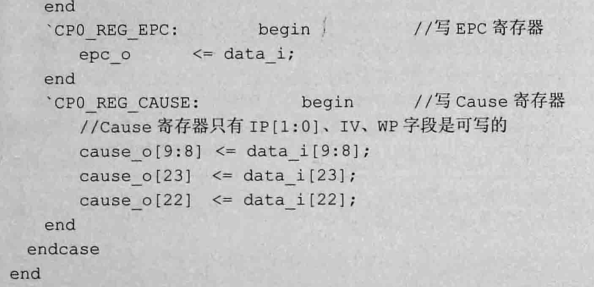

读操作:

三 协处理器访问指令说明

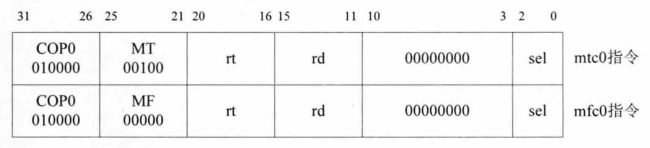

这两个指令一个写一个读:

这2条指令的格式与之前已实现的指令都不同,主要特点是:指令码都为6'b010000,MIPS32 指令集架构定义为COP0类,需要借助于第21~ 25bit的值才能确定具体是哪一条指令。 此外,指令的第3~10bit为0,第0~2bit是sel域,这个域的作用取决于具体的MIPS32架构处理器,对OpenMIPS处理器而言,sel 域没有作用,不用考虑。下面分别说明mtc0、mfc0 两条指令的用法、作用。

●当指令码是6'b010000,且第21~25bit的值为5'"b00100 时,是mtc0指令。

指令用法为:mtc0 rt, rd。

指令作用为: CPR[0, rd] <- GPR[rt],将地址为rt的通用寄存器的值赋给协处理器CP0中地址为rd的寄存器。

●当指令码是 6'b010000,且第21~ 25bit的值为500000时,是mfc0指令。

指令用法为: mfc0 rt, rd。

指令作用为: GPR[rt] <- CPR[0, rd],读出协处理器CPO中地址为rd的寄存器的值,并赋给地址为rt的通用寄存器。

四 具体实现

指令的读写在执行阶段进行定义,读操作需要提前去读CP0寄存器的值并传递回来,而写操作需要把使能以及写入值与地址传递到CP0.此外新引入的寄存器同样会发生数据相关问题,还是使用数据前推进行解决。

1.译码阶段

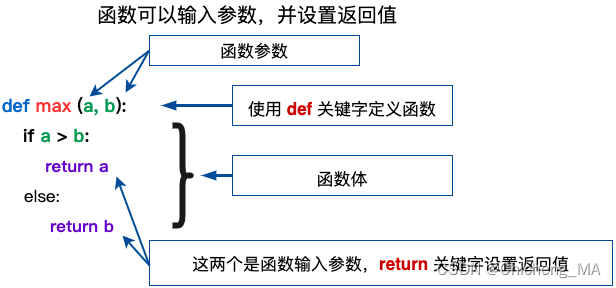

mtc0修改CP0寄存器的值,修改的值在rt里,修改的地址在rd中,所以不需要写通用寄存器,但是需要读rt中的值。

mfc0是读出协处理器CPO中地址为rd的寄存器的值,并赋给地址为rt的通用寄存器。需要写通用寄存器,两个地址都在指令中直接用,不需要读寄存器。

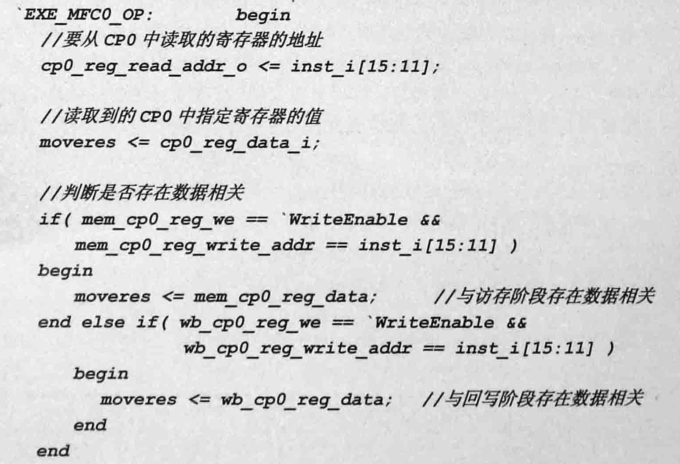

2.执行阶段

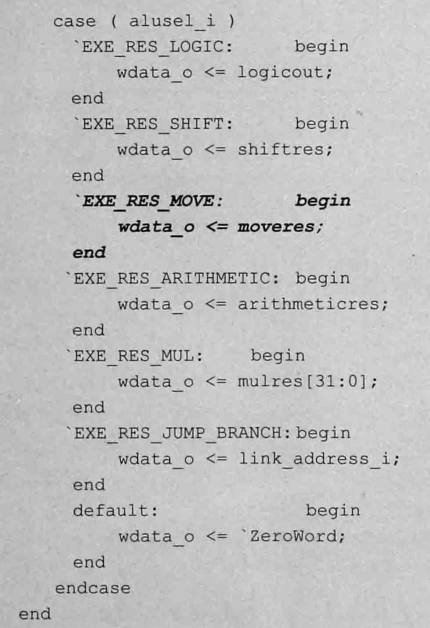

要实现mfc0需要两步,先去读CP0的值,可能不是最新的值所以判断一下数据相关(如果访存和回写阶段需要写回CP0并且写回地址和我们要读的地址一样),如果是把写入的值直接传过来,记为moveres。

然后再写入:

然后再写入:

如果是mtc0 指令,那么给出对CP0中寄存器的写信息:设置写操作信号cp0_ reg_ we. o为WriteEnable、 写入地址为指令中第11~ 15bit的值、写入的值就是译码阶段传递过来的regl_i的值,参考译码阶段可知,该值正是地址为rt的通用寄存器的值。

后面把需要写入寄存器的值一直传递到CP0寄存器就行了。