课程链接:深入浅出计算机组成原理_组成原理_计算机基础-极客时间

目录

一、FPGA

(一)FPGA 的解决方案步骤

1、用存储换功能实现组合逻辑

2、对于需要实现的时序逻辑电路,在 FPGA 里面直接放上 D 触发器,作为寄存器

3、可编程逻辑布线

二、ASIC

(一)选择ASCI还是FPGA

(二)解读TPU--拆解一块ASCI芯片

1、深度学习模型的训练和推断有什么不同

2、TPU的设计

3、TPU的细节优化

一、FPGA

PAL(Programmable Array Logic,可编程阵列逻辑),只能“编程”一次,把预先写好的程序一次性烧录到硬件里面,之后就不能再修改了。

FPGA,现场可编程门阵列(Field-Programmable Gate Array):可以通过编程,来控制硬件电路的芯片。

(一)FPGA 的解决方案步骤

1、用存储换功能实现组合逻辑

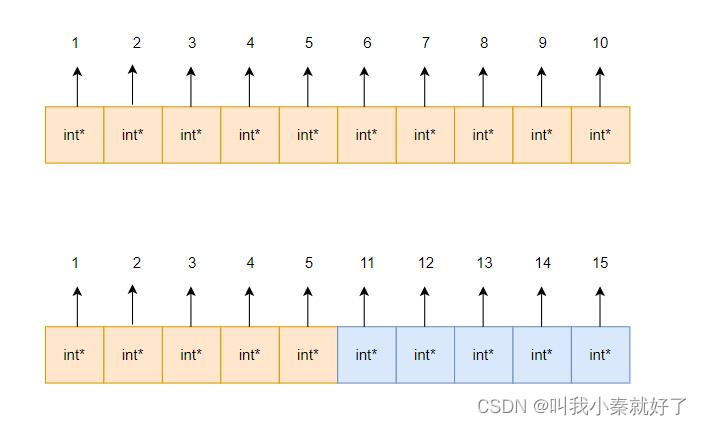

在实现 CPU 的功能的时候需要完成各种各样的电路逻辑。在 FPGA 里,这些基本的电路逻辑,不是采用布线连接的方式进行的,而是预先根据软件里设计的逻辑电路,算出对应的真值表,然后存储到一个叫作 LUT(Look-Up Table,查找表)的电路里面。这个 LUT 呢,其实就是一块存储空间,里面存储了“特定的输入信号下,对应输出 0 还是 1”(存储各种情况下的结果,使用的时候根据实际需要查找结果)。

2、对于需要实现的时序逻辑电路,在 FPGA 里面直接放上 D 触发器,作为寄存器

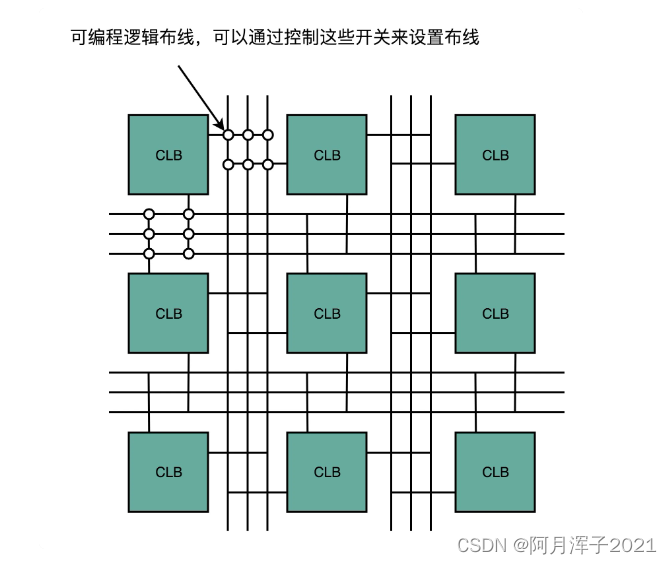

和 CPU 里的触发器没有本质的不同。不过,会把很多个 LUT 的电路和寄存器组合在一起,变成逻辑簇(Logic Cluster)。在 FPGA 里,这样组合了多个 LUT 和寄存器的设备,也被叫做 CLB(Configurable Logic Block,可配置逻辑块)。

3、可编程逻辑布线

通过 LUT 和寄存器,我们能够组合出很多 CLB,FPGA 通过可编程逻辑布线,来连接各个不同的 CLB,最终实现需要实现的芯片功能。

二、ASIC

ASIC(Application-Specific Integrated Circuit),专用集成电路,为专门用途的场景,单独设计的芯片。如手机里专门用在摄像头里的芯片,录音笔里专门处理音频的芯片。

因为 ASIC 是针对专门用途设计的,跟CPU比起来,它的电路更精简,通常能耗也更低,单片的制造成本也更低。

ASIC 的一个典型设计思路,就是把确定的程序指令流程,变成固定的硬件电路。

(一)选择ASCI还是FPGA

FPGA也可以做ASIC的事情,但它在硬件上有点浪费。一个 LUT 电路设计出来之后,既可以实现与门,又可以实现或门,自然用到的晶体管数量,比单纯连死的与门或者或门的要多得多。同时,因为用的晶体管多,它的能耗也比单纯连死的电路要大,单片 FPGA 的生产制造的成本也比 ASIC 要高不少。

FPGA的优点在于,它没有硬件研发成本。ASIC 的电路设计,需要仿真、验证,还需要经过流片(Tape out),变成一个印刷的电路版,最终变成芯片。整个从研发到上市的过程,最低花费也要几万美元,高的话,会在几千万乃至数亿美元。更何况,整个设计还有失败的可能。所以,如果设计的专用芯片,只是要制造几千片,那买几千片现成的 FPGA,可能远比花上几百万美元,来设计、制造 ASIC 要经济得多。

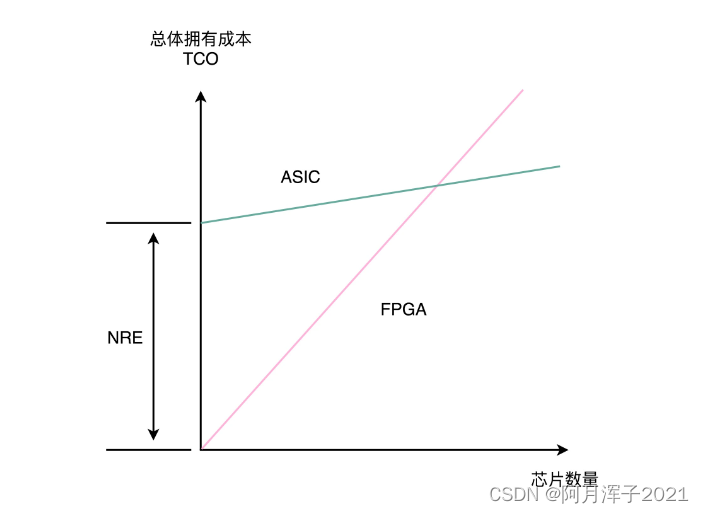

到底使用 ASIC 这样的专用芯片,还是采用 FPGA 这样可编程的通用硬件,核心的决策因素还是成本。不过这个成本,不只是单个芯片的生产制造成本,还要考虑总体拥有成本(Total Cost of Ownership),也就是说,除了生产成本之外,要把研发成本也算进去。如果只制造了一片芯片,那么成本就是“这枚芯片的成本 + 为了这枚芯片建的生产线的成本 + 芯片的研发成本”

单个 ASIC 的生产制造成本比 FPGA 低,ASIC 的能耗也比能实现同样功能的 FPGA 要低。能耗低,意味着长时间运行这些芯片,所用的电力成本也更低。但是,ASIC 有一笔很高的 NRE(Non-Recuring Engineering Cost,一次性工程费用)成本。这个成本,就是 ASIC 实际“研发”的成本。只有需要大量生产 ASIC 芯片的时候,才能摊薄这份研发成本。

(二)解读TPU--拆解一块ASCI芯片

作为过去几年最知名、最具实用价值的ASCI,TPU是在深度学习的热潮里应运而生的。

深度学习中,计算量最大的不是进行深度学习的训练,而是深度学习的推断部分。

推断部分是指完成深度学习训练之后,把训练完成的模型存储下来。这个模型是许许多多个向量组成的参数。根据这些参数计算输入的数据,最终得到一个计算结果。这个推断过程,可能是在互联网广告领域,去推测某一个用户是否会点击特定的广告;也可能是我们在经过高铁站的时候,扫一下身份证进行一次人脸识别,判断一下是不是你本人。

虽然训练一个深度学习的模型需要花的时间不少,但是实际在推断上花的时间要更多。所以,第一代的 TPU,首先优化的不是深度学习的模型训练,而是深度学习的模型推断。

1、深度学习模型的训练和推断有什么不同

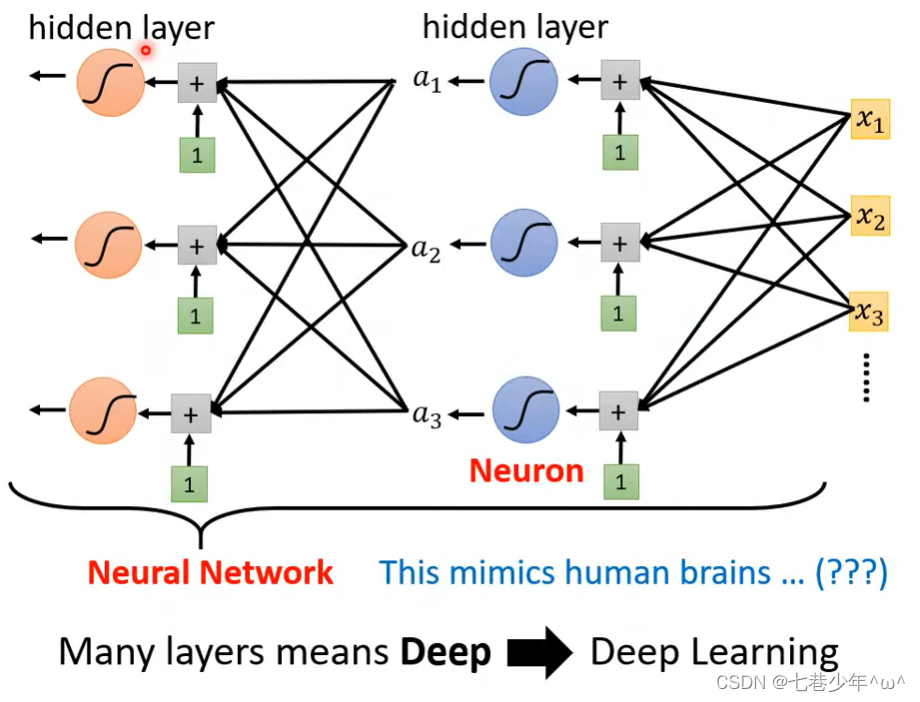

第一,深度学习的推断工作更简单,对灵活性的要求也就更低。模型推断的过程,只需要计算一些矩阵的乘法、加法,调用一些类似Sigmoid 或者 RELU 的激活函数。这样的过程可能需要反复进行很多层,但也只是这些计算过程的简单组合。

第二、推断的性能首先要保障的指标是响应时间。计算机关注的性能指标,有响应时间(Response Time)和吞吐率(Throughput)。模型训练的时候,只需要考虑吞吐率问题就行了。因为一个模型训练少则好几分钟,多的话要几个月。而推断过程,像互联网广告的点击预测,我们往往希望能在几十毫秒乃至几毫秒之内就完成,而人脸识别也不希望会超过几秒钟。很显然,模型训练和推断对于性能的要求是截然不同的。

第三、深度学习的推断工作,希望在功耗上尽可能少一些。深度学习的训练,对功耗没有那么敏感,只是希望训练速度能够尽可能快,多费点电就多费点儿了。而深度学习的推断,要 7×24h 地跑在数据中心里面,对应的芯片要大规模地部署在数据中心。一块芯片减少 5% 的功耗,就能节省大量的电费。而深度学习的训练工作,大部分情况下只是少部分算法工程师用少量的机器进行。很多时候,只是做小规模的实验,尽快得到结果,节约人力成本。少数几台机器多花的电费,比起算法工程师的工资来说,只能算九牛一毛了。

2、TPU的设计

TPU 并没有设计成一个独立的“CPU“,而是设计成一块像显卡一样,插在主板 PCI-E 接口上的板卡,甚至没有设计自己对应的取指令的电路,需要通过 CPU才能向 TPU 发送需要执行的指令。

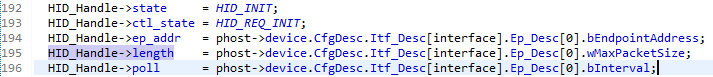

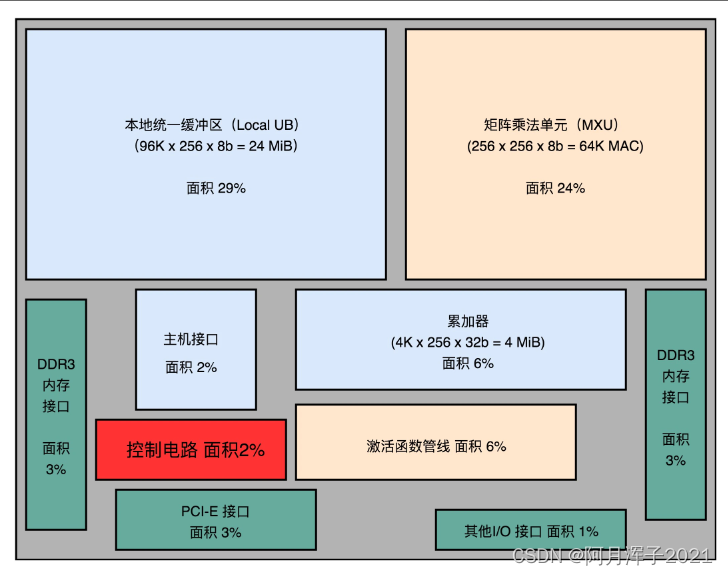

TPU模块图:

芯片模块图里面,有单独的矩阵乘法单元(Matrix Multiply Unit)、累加器(Accumulators)模块、激活函数(Activation)模块和归一化 / 池化(Normalization/Pool)模块。而且,这些模块是顺序串联在一起的。

芯片模块图里面,有单独的矩阵乘法单元(Matrix Multiply Unit)、累加器(Accumulators)模块、激活函数(Activation)模块和归一化 / 池化(Normalization/Pool)模块。而且,这些模块是顺序串联在一起的。

这是因为,一个深度学习的推断过程,是由很多层的计算组成的。而每一个层(Layer)的计算过程,就是先进行矩阵乘法,再进行累加,接着调用激活函数,最后进行归一化和池化。

控制电路(Control)只占了 2%。是因为TPU 的计算过程基本上是一个固定的流程。不像 CPU ,有各种复杂的控制功能,比如冒险、分支预测等等。

比于矩阵乘法单元,累加器、实现激活函数和后续的归一 / 池化功能的激活管线(Activation Pipeline)也用得不多。是因为,在深度学习推断的过程中,矩阵乘法的计算量是最大的,计算也更复杂,所以比简单的累加器和激活函数要占用更多的晶体管。

统一缓冲区(Unified Buffer)由 SRAM 这样高速的存储设备组成。SRAM 一般被直接拿来作为 CPU 的寄存器或者高速缓存,比起内存使用的 DRAM 速度要快上很多,但是因为电路密度小,所以占用的空间要大很多。统一缓冲区之所以使用 SRAM,是因为在整个的推断过程中,它会高频反复地被矩阵乘法单元读写,来完成计算。

3、TPU的细节优化

除了整个 TPU 的模块设计和芯片布局之外,TPU 在各个细节上也充分考虑了自己的应用场景。譬如矩阵乘法单元(Matrix Multiply Unit),矩阵乘法单元没有用 32 Bits 来存放一个浮点数,而是只用了一个 8 Bits 来存放浮点数。是因为在实践的机器学习应用中,会对数据做归一化(Normalization)和正则化(Regularization)的处理。这两个操作会使得深度学习里面操作的数据都不会变得太大。通常来说呢,能控制在 -3 到 3 这样的范围之内。

课程链接:深入浅出计算机组成原理_组成原理_计算机基础-极客时间