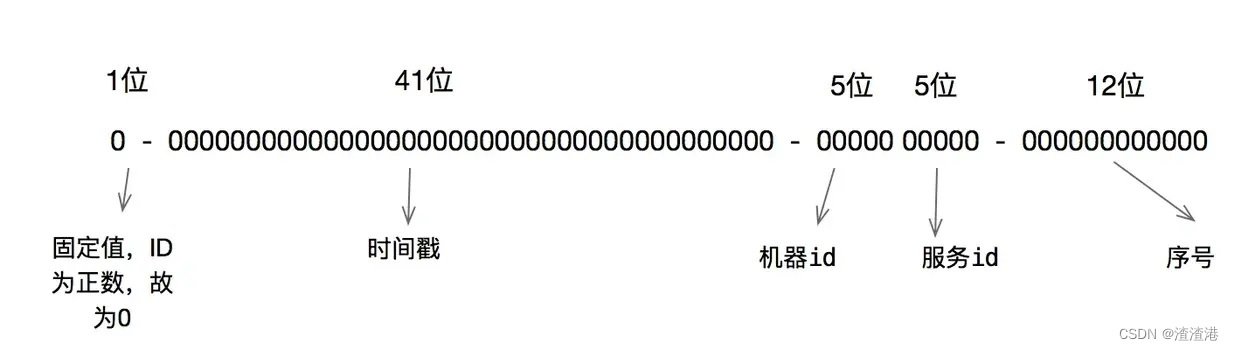

基于XCZU21DR-2FFVD1156E开发,本文介绍对PL DDR4的读写操作,代码全部经过上板测试。

目录

添加DDR4 IP

Basic

Mode and Interface & Clocking

Controller Options

Advanced Clocking

VIO IP配置

ILA IP配置

General Options

Probe_Ports(0..7)

Probe_Ports(8..15)

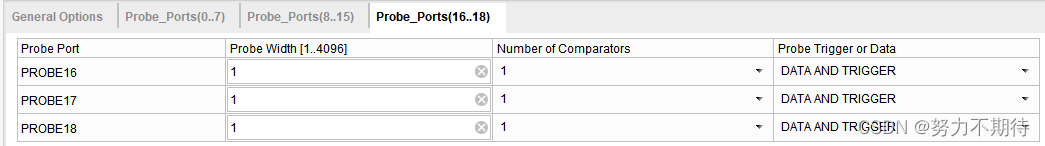

Probe_Ports(16..18)

top代码

ddr4_rw代码

top.xdc内容

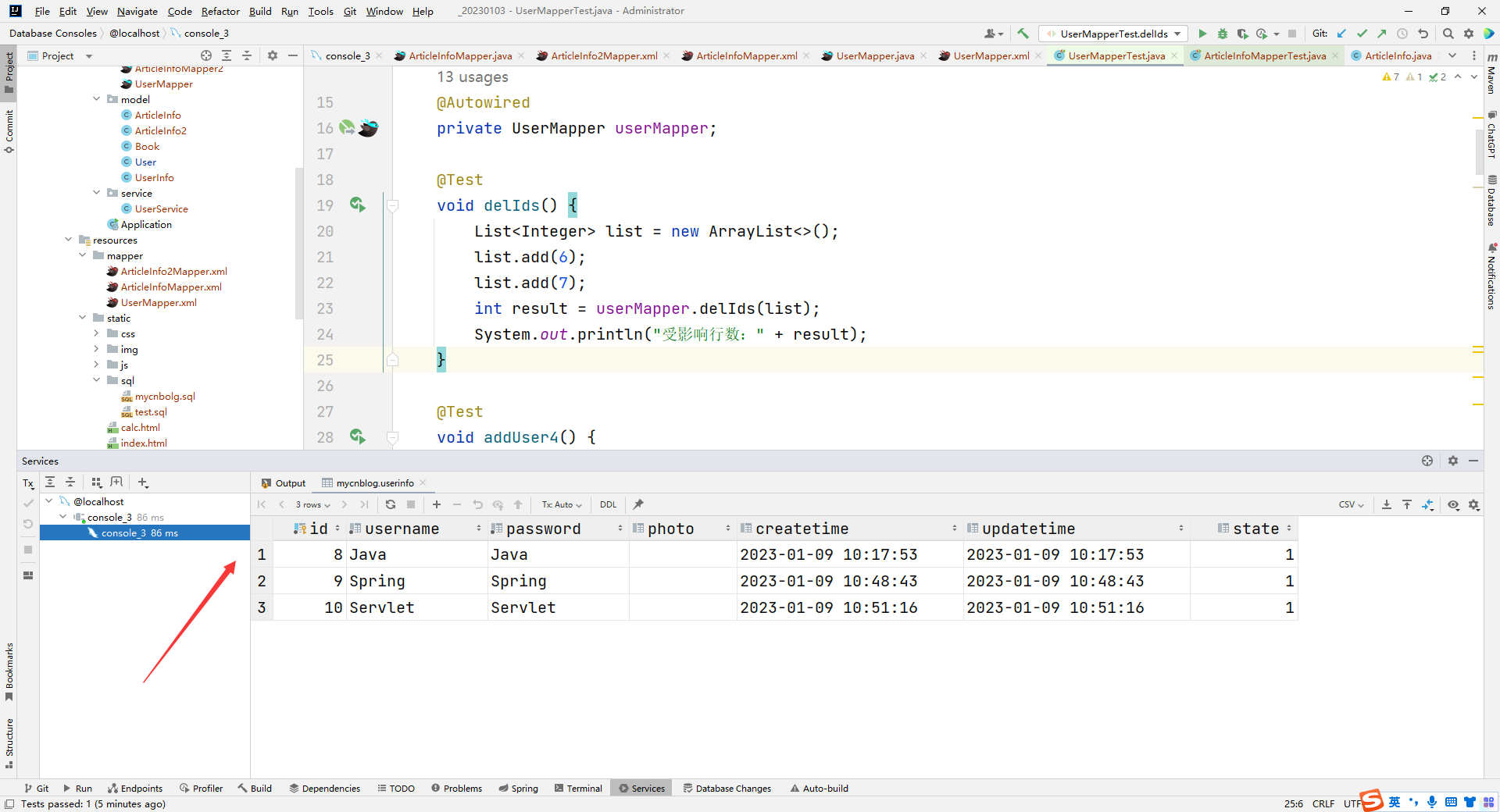

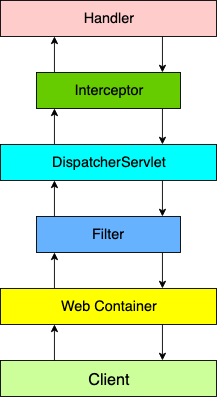

系统框图如下:

添加DDR4 IP

DDR4颗粒采用MT40A2G8VA-062E IT,配置如下:

Basic

Mode and Interface & Clocking

Controller Options

Advanced Clocking

VIO IP配置

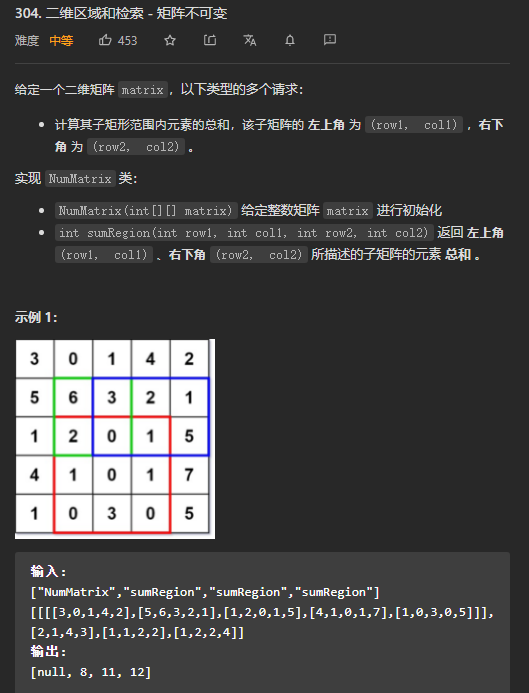

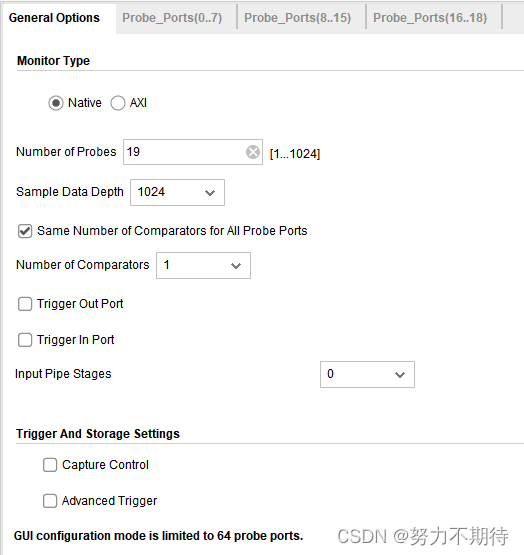

ILA IP配置

General Options

Probe_Ports(0..7)

Probe_Ports(8..15)

Probe_Ports(16..18)

top代码

module ddr4_rw_top(

output c0_ddr4_act_n ,

output [16:0] c0_ddr4_adr ,

output [1:0] c0_ddr4_ba ,

output [1:0] c0_ddr4_bg ,

output [0:0] c0_ddr4_cke ,

output [0:0] c0_ddr4_odt ,

output [0:0] c0_ddr4_cs_n ,

output [0:0] c0_ddr4_ck_t ,

output [0:0] c0_ddr4_ck_c ,

output c0_ddr4_reset_n ,

inout [7:0] c0_ddr4_dm_dbi_n,

inout [63:0] c0_ddr4_dq ,

inout [7:0] c0_ddr4_dqs_c ,

inout [7:0] c0_ddr4_dqs_t ,

//Differential system clocks

input c0_sys_clk_p,

input c0_sys_clk_n,

output led,

input sys_rst_n

);

//wire define

wire error_flag;

wire c0_ddr4_ui_clk ;

wire c0_ddr4_ui_clk_sync_rst ;

wire c0_ddr4_app_en ;

wire c0_ddr4_app_hi_pri ;

wire c0_ddr4_app_wdf_end ;

wire c0_ddr4_app_wdf_wren ;

wire c0_ddr4_app_rd_data_end ;

wire c0_ddr4_app_rd_data_valid ;

wire c0_ddr4_app_rdy ;

wire c0_ddr4_app_wdf_rdy ;

wire [27 : 0] c0_ddr4_app_addr ;

wire [2 : 0] c0_ddr4_app_cmd ;

wire [127 : 0] c0_ddr4_app_wdf_data;

wire [15 : 0] c0_ddr4_app_wdf_mask ;

wire [127 : 0] c0_ddr4_app_rd_data ;

wire c0_init_calib_complete;

wire addn_ui_clkout1;

wire ui_clk_sync_rst; //用户复位信号

wire init_calib_complete; //校准完成信号

wire [20:0] rd_cnt; //实际读地址计数

wire [1 :0] state; //状态计数器

wire [23:0] rd_addr_cnt; //用户读地址计数器

wire [23:0] wr_addr_cnt; //用户写地址计数器

wire out_sys_rst_n;

wire probe_out0_n;

//读写模块

ddr4_rw u_ddr4_rw(

.ui_clk (c0_ddr4_ui_clk),

.ui_clk_sync_rst (c0_ddr4_ui_clk_sync_rst),

.init_calib_complete (c0_init_calib_complete),

.app_rdy (c0_ddr4_app_rdy),

.app_wdf_rdy (c0_ddr4_app_wdf_rdy),

.app_rd_data_valid (c0_ddr4_app_rd_data_valid),

.app_rd_data (c0_ddr4_app_rd_data),

.app_addr (c0_ddr4_app_addr),

.app_en (c0_ddr4_app_en),

.app_wdf_wren (c0_ddr4_app_wdf_wren),

.app_wdf_end (c0_ddr4_app_wdf_end),

.app_cmd (c0_ddr4_app_cmd),

.app_wdf_data (c0_ddr4_app_wdf_data),

.state (state),

.rd_addr_cnt (rd_addr_cnt),

.wr_addr_cnt (wr_addr_cnt),

.rd_cnt (rd_cnt),

.error_flag (error_flag),

.led (led)

);

ddr4_0 u_ddr4_0 (

.c0_init_calib_complete(c0_init_calib_complete), // 初始化完成信号

.dbg_clk(),

.c0_sys_clk_p(c0_sys_clk_p), // 系统差分时钟p

.c0_sys_clk_n(c0_sys_clk_n), // 系统差分时钟n

.dbg_bus(),

.c0_ddr4_adr(c0_ddr4_adr), // 行列地址

.c0_ddr4_ba(c0_ddr4_ba), // bank地址

.c0_ddr4_cke(c0_ddr4_cke), // 时钟使能

.c0_ddr4_cs_n(c0_ddr4_cs_n), // 片选信号

.c0_ddr4_dm_dbi_n(c0_ddr4_dm_dbi_n), // 数据掩码

.c0_ddr4_dq(c0_ddr4_dq), // 数据线

.c0_ddr4_dqs_c(c0_ddr4_dqs_c), // inout wire [7 : 0] c0_ddr4_dqs_c

.c0_ddr4_dqs_t(c0_ddr4_dqs_t), // inout wire [7 : 0] c0_ddr4_dqs_t

.c0_ddr4_odt(c0_ddr4_odt), // output wire [0 : 0] c0_ddr4_odt

.c0_ddr4_bg(c0_ddr4_bg), // output wire [1 : 0] c0_ddr4_bg

.c0_ddr4_reset_n(c0_ddr4_reset_n), // output wire c0_ddr4_reset_n

.c0_ddr4_act_n(c0_ddr4_act_n), // output wire c0_ddr4_act_n

.c0_ddr4_ck_c(c0_ddr4_ck_c), // output wire [0 : 0] c0_ddr4_ck_c

.c0_ddr4_ck_t(c0_ddr4_ck_t), // output wire [0 : 0] c0_ddr4_ck_t

//user interface

.c0_ddr4_ui_clk(c0_ddr4_ui_clk), // output wire c0_ddr4_ui_clk 用户时钟

.c0_ddr4_ui_clk_sync_rst(c0_ddr4_ui_clk_sync_rst), // output wire c0_ddr4_ui_clk_sync_rst 用户复位

.c0_ddr4_app_en(c0_ddr4_app_en), // input wire c0_ddr4_app_en

.c0_ddr4_app_hi_pri(1'b0), // input wire c0_ddr4_app_hi_pri

.c0_ddr4_app_wdf_end(c0_ddr4_app_wdf_end), // input wire c0_ddr4_app_wdf_end

.c0_ddr4_app_wdf_wren(c0_ddr4_app_wdf_wren), // input wire c0_ddr4_app_wdf_wren

.c0_ddr4_app_rd_data_end(c0_ddr4_app_rd_data_end), // output wire c0_ddr4_app_rd_data_end

.c0_ddr4_app_rd_data_valid(c0_ddr4_app_rd_data_valid), // output wire c0_ddr4_app_rd_data_valid

.c0_ddr4_app_rdy(c0_ddr4_app_rdy), // output wire c0_ddr4_app_rdy

.c0_ddr4_app_wdf_rdy(c0_ddr4_app_wdf_rdy), // output wire c0_ddr4_app_wdf_rdy

.c0_ddr4_app_addr(c0_ddr4_app_addr), // input wire [27 : 0] c0_ddr4_app_addr

.c0_ddr4_app_cmd(c0_ddr4_app_cmd), // input wire [2 : 0] c0_ddr4_app_cmd

.c0_ddr4_app_wdf_data(c0_ddr4_app_wdf_data), // input wire [127 : 0] c0_ddr4_app_wdf_data

.c0_ddr4_app_wdf_mask(16'b0), // input wire [15 : 0] c0_ddr4_app_wdf_mask

.c0_ddr4_app_rd_data(c0_ddr4_app_rd_data), // output wire [127 : 0] c0_ddr4_app_rd_data

.addn_ui_clkout1(addn_ui_clkout1), // output wire addn_ui_clkout1

.sys_rst(~sys_rst_n) // input wire sys_rst

//.sys_rst(~probe_out0_n) // input wire sys_rst

);

vio_0 vio_0_inst (

.clk(addn_ui_clkout1), // input wire clk

.probe_in0(error_flag), // input wire [0 : 0] probe_in0

.probe_out0(probe_out0_n) // output wire [0 : 0] probe_out0

);

endmoduleddr4_rw代码

module ddr4_rw (

input ui_clk, //用户时钟

input ui_clk_sync_rst, //复位,高有效

input init_calib_complete, //DDR4初始化完成

input app_rdy, //MIG 命令接收准备好标致

input app_wdf_rdy, //MIG数据接收准备好

input app_rd_data_valid, //读数据有效

input [127:0] app_rd_data, //用户读数据

output reg [27:0] app_addr, //DDR4地址

output app_en, //MIG IP发送命令使能

output app_wdf_wren, //用户写数据使能

output app_wdf_end, //突发写当前时钟最后一个数据

output [2:0] app_cmd, //MIG IP核操作命令,读或者写

output reg [127:0] app_wdf_data, //用户写数据

output reg [1 :0] state, //读写状态

output reg [23:0] rd_addr_cnt, //用户读地址计数

output reg [23:0] wr_addr_cnt, //用户写地址计数

output reg [20:0] rd_cnt, //实际读地址标记

output reg error_flag, //读写错误标志

output reg led //读写测试结果指示灯

);

//parameter define

parameter TEST_LENGTH = 1000;

parameter L_TIME = 25'd25_000_000;

parameter IDLE = 2'd0; //空闲状态

parameter WRITE = 2'd1; //写状态

parameter WAIT = 2'd2; //读到写过度等待

parameter READ = 2'd3; //读状态

//reg define

reg [24:0] led_cnt; //led计数

//wire define

wire error; //读写错误标记

wire rst_n; //复位,低有效

assign rst_n = ~ui_clk_sync_rst;

//读信号有效,且读出的数不是写入的数时,将错误标志位拉高

assign error = (app_rd_data_valid && (rd_cnt!=app_rd_data));

//在写状态MIG IP 命令接收和数据接收都准备好,或者在读状态命令接收准备好,此时拉高使能信号,

assign app_en = ((state == WRITE && (app_rdy && app_wdf_rdy))

||(state == READ && app_rdy)) ? 1'b1:1'b0;

//在写状态,命令接收和数据接收都准备好,此时拉高写使能

assign app_wdf_wren = (state == WRITE && (app_rdy && app_wdf_rdy)) ? 1'b1:1'b0;

//由于DDR4芯片时钟和用户时钟的分频选择4:1,突发长度为8,故两个信号相同

assign app_wdf_end = app_wdf_wren;

//处于读的时候命令值为1,其他时候命令值为0

assign app_cmd = (state == READ) ? 3'd1 :3'd0;

//DDR4读写逻辑实现

always @(posedge ui_clk or negedge rst_n) begin

if((~rst_n)||(error_flag)) begin

state <= IDLE;

app_wdf_data <= 128'd0;

wr_addr_cnt <= 24'd0;

rd_addr_cnt <= 24'd0;

app_addr <= 28'd0;

end

else if(init_calib_complete)begin //MIG IP核初始化完成

case(state)

IDLE:begin

state <= WRITE;

app_wdf_data <= 128'd0;

wr_addr_cnt <= 24'd0;

rd_addr_cnt <= 24'd0;

app_addr <= 28'd0;

end

WRITE:begin

if(wr_addr_cnt == TEST_LENGTH - 1 &&(app_rdy && app_wdf_rdy))

state <= WAIT; //写到设定的长度跳到等待状态

else if(app_rdy && app_wdf_rdy)begin //写条件满足

app_wdf_data <= app_wdf_data + 1; //写数据自加

wr_addr_cnt <= wr_addr_cnt + 1; //写地址自加

app_addr <= app_addr + 8; //DDR4地址加8

end

else begin //写条件不满足,保持当前值

app_wdf_data <= app_wdf_data;

wr_addr_cnt <= wr_addr_cnt;

app_addr <= app_addr;

end

end

WAIT:begin

state <= READ; //下一个时钟,跳到读状态

rd_addr_cnt <= 24'd0; //读地址复位

app_addr <= 28'd0; //DDR4读从地址0开始

end

READ:begin //读到设定的地址长度

if(rd_addr_cnt == TEST_LENGTH - 1 && app_rdy)

state <= IDLE; //则跳到空闲状态

else if(app_rdy)begin //若MIG已经准备好,则开始读

rd_addr_cnt <= rd_addr_cnt + 1'd1; //用户地址每次加一

app_addr <= app_addr + 8; //DDR4地址加8

end

else begin //若MIG没准备好,则保持原值

rd_addr_cnt <= rd_addr_cnt;

app_addr <= app_addr;

end

end

default:begin

state <= IDLE;

app_wdf_data <= 128'd0;

wr_addr_cnt <= 24'd0;

rd_addr_cnt <= 24'd0;

app_addr <= 28'd0;

end

endcase

end

end

//对DDR4实际读数据个数编号计数

always @(posedge ui_clk or negedge rst_n) begin

if(~rst_n)

rd_cnt <= 0; //若计数到读写长度,且读有效,地址计数器则置0

else if(app_rd_data_valid && rd_cnt == TEST_LENGTH - 1)

rd_cnt <= 0; //其他条件只要读有效,每个时钟自增1

else if (app_rd_data_valid )

rd_cnt <= rd_cnt + 1;

end

//寄存状态标志位

always @(posedge ui_clk or negedge rst_n) begin

if(~rst_n)

error_flag <= 0;

else if(error)

error_flag <= 1;

else

error_flag <= 0;

end

//led指示效果控制

always @(posedge ui_clk or negedge rst_n) begin

if((~rst_n) || (~init_calib_complete )) begin

led_cnt <= 25'd0;

led <= 1'b0;

end

else begin

if(~error_flag) //读写测试正确

led <= 1'b1; //led灯常亮

else begin //读写测试错误

led_cnt <= led_cnt + 25'd1;

if(led_cnt == L_TIME - 1'b1) begin

led_cnt <= 25'd0;

led <= ~led; //led灯闪烁

end

end

end

end

ila_0 ila_0_inst (

.clk(ui_clk), // input wire clk

.probe0(app_rd_data_valid), // input wire [0:0] probe0

.probe1(app_rd_data), // input wire [127:0] probe1

.probe2(app_addr), // input wire [27:0] probe2

.probe3(app_cmd), // input wire [2:0] probe3

.probe4(app_wdf_data), // input wire [127:0] probe4

.probe5(state), // input wire [1:0] probe5

.probe6(rd_addr_cnt), // input wire [23:0] probe6

.probe7(wr_addr_cnt), // input wire [23:0] probe7

.probe8(rd_cnt), // input wire [20:0] probe8

.probe9(error_flag), // input wire [0:0] probe9

.probe10(led), // input wire [0:0] probe10

.probe11(ui_clk_sync_rst), // input wire [0:0] probe11

.probe12(init_calib_complete), // input wire [0:0] probe12

.probe13(app_rdy), // input wire [0:0] probe13

.probe14(app_wdf_rdy), // input wire [0:0] probe14

.probe15(app_wdf_end), // input wire [0:0] probe15

.probe16(app_en), // input wire [0:0] probe16

.probe17(app_wdf_wren), // input wire [0:0] probe17

.probe18(error) // input wire [0:0] probe18

);

endmoduletop.xdc内容

set_property PACKAGE_PIN L14 [get_ports led]

set_property PACKAGE_PIN T3 [get_ports sys_rst_n]

set_property IOSTANDARD LVCMOS33 [get_ports sys_rst_n]

set_property PACKAGE_PIN AK1 [get_ports {c0_ddr4_adr[16]}]

set_property PACKAGE_PIN AH6 [get_ports {c0_ddr4_adr[6]}]

set_property PACKAGE_PIN AG3 [get_ports {c0_ddr4_adr[11]}]

set_property PACKAGE_PIN AK2 [get_ports {c0_ddr4_adr[12]}]

set_property PACKAGE_PIN AJ3 [get_ports {c0_ddr4_adr[10]}]

set_property PACKAGE_PIN AG2 [get_ports {c0_ddr4_adr[2]}]

set_property PACKAGE_PIN AH2 [get_ports {c0_ddr4_adr[4]}]

set_property PACKAGE_PIN AP3 [get_ports {c0_ddr4_adr[0]}]

set_property PACKAGE_PIN AP4 [get_ports {c0_ddr4_adr[8]}]

set_property PACKAGE_PIN AN4 [get_ports {c0_ddr4_adr[3]}]

set_property PACKAGE_PIN AN5 [get_ports {c0_ddr4_adr[7]}]

set_property PACKAGE_PIN AP2 [get_ports {c0_ddr4_adr[15]}]

set_property PACKAGE_PIN AN2 [get_ports {c0_ddr4_adr[14]}]

set_property PACKAGE_PIN AM2 [get_ports {c0_ddr4_adr[9]}]

set_property PACKAGE_PIN AM3 [get_ports {c0_ddr4_adr[13]}]

set_property PACKAGE_PIN AH7 [get_ports {c0_ddr4_adr[5]}]

set_property PACKAGE_PIN AG1 [get_ports {c0_ddr4_adr[1]}]

set_property PACKAGE_PIN AH1 [get_ports {c0_ddr4_ba[1]}]

set_property PACKAGE_PIN AM4 [get_ports {c0_ddr4_ba[0]}]

set_property PACKAGE_PIN AJ2 [get_ports {c0_ddr4_bg[1]}]

set_property PACKAGE_PIN AL4 [get_ports {c0_ddr4_bg[0]}]

set_property PACKAGE_PIN AK6 [get_ports {c0_ddr4_ck_t[0]}]

set_property PACKAGE_PIN AL1 [get_ports {c0_ddr4_cke[0]}]

set_property PACKAGE_PIN AL6 [get_ports {c0_ddr4_cs_n[0]}]

set_property PACKAGE_PIN C5 [get_ports {c0_ddr4_dm_dbi_n[7]}]

set_property PACKAGE_PIN F6 [get_ports {c0_ddr4_dm_dbi_n[6]}]

set_property PACKAGE_PIN J5 [get_ports {c0_ddr4_dm_dbi_n[5]}]

set_property PACKAGE_PIN M7 [get_ports {c0_ddr4_dm_dbi_n[4]}]

set_property PACKAGE_PIN AA3 [get_ports {c0_ddr4_dm_dbi_n[3]}]

set_property PACKAGE_PIN AA6 [get_ports {c0_ddr4_dm_dbi_n[2]}]

set_property PACKAGE_PIN AD8 [get_ports {c0_ddr4_dm_dbi_n[1]}]

set_property PACKAGE_PIN AE1 [get_ports {c0_ddr4_dm_dbi_n[0]}]

set_property PACKAGE_PIN A9 [get_ports {c0_ddr4_dq[63]}]

set_property PACKAGE_PIN B4 [get_ports {c0_ddr4_dq[62]}]

set_property PACKAGE_PIN B9 [get_ports {c0_ddr4_dq[61]}]

set_property PACKAGE_PIN A6 [get_ports {c0_ddr4_dq[60]}]

set_property PACKAGE_PIN A8 [get_ports {c0_ddr4_dq[59]}]

set_property PACKAGE_PIN A5 [get_ports {c0_ddr4_dq[58]}]

set_property PACKAGE_PIN B8 [get_ports {c0_ddr4_dq[57]}]

set_property PACKAGE_PIN A4 [get_ports {c0_ddr4_dq[56]}]

set_property PACKAGE_PIN E5 [get_ports {c0_ddr4_dq[55]}]

set_property PACKAGE_PIN E8 [get_ports {c0_ddr4_dq[54]}]

set_property PACKAGE_PIN F5 [get_ports {c0_ddr4_dq[53]}]

set_property PACKAGE_PIN D9 [get_ports {c0_ddr4_dq[52]}]

set_property PACKAGE_PIN E7 [get_ports {c0_ddr4_dq[51]}]

set_property PACKAGE_PIN C6 [get_ports {c0_ddr4_dq[50]}]

set_property PACKAGE_PIN C7 [get_ports {c0_ddr4_dq[49]}]

set_property PACKAGE_PIN C9 [get_ports {c0_ddr4_dq[48]}]

set_property PACKAGE_PIN F8 [get_ports {c0_ddr4_dq[47]}]

set_property PACKAGE_PIN J7 [get_ports {c0_ddr4_dq[46]}]

set_property PACKAGE_PIN G8 [get_ports {c0_ddr4_dq[45]}]

set_property PACKAGE_PIN H9 [get_ports {c0_ddr4_dq[44]}]

set_property PACKAGE_PIN G6 [get_ports {c0_ddr4_dq[43]}]

set_property PACKAGE_PIN G7 [get_ports {c0_ddr4_dq[42]}]

set_property PACKAGE_PIN G9 [get_ports {c0_ddr4_dq[41]}]

set_property PACKAGE_PIN J8 [get_ports {c0_ddr4_dq[40]}]

set_property PACKAGE_PIN L6 [get_ports {c0_ddr4_dq[39]}]

set_property PACKAGE_PIN K6 [get_ports {c0_ddr4_dq[38]}]

set_property PACKAGE_PIN M8 [get_ports {c0_ddr4_dq[37]}]

set_property PACKAGE_PIN J10 [get_ports {c0_ddr4_dq[36]}]

set_property PACKAGE_PIN L8 [get_ports {c0_ddr4_dq[35]}]

set_property PACKAGE_PIN J9 [get_ports {c0_ddr4_dq[34]}]

set_property PACKAGE_PIN L10 [get_ports {c0_ddr4_dq[33]}]

set_property PACKAGE_PIN K10 [get_ports {c0_ddr4_dq[32]}]

set_property PACKAGE_PIN V1 [get_ports {c0_ddr4_dq[31]}]

set_property PACKAGE_PIN AB1 [get_ports {c0_ddr4_dq[30]}]

set_property PACKAGE_PIN W3 [get_ports {c0_ddr4_dq[29]}]

set_property PACKAGE_PIN AB2 [get_ports {c0_ddr4_dq[28]}]

set_property PACKAGE_PIN W2 [get_ports {c0_ddr4_dq[27]}]

set_property PACKAGE_PIN Y1 [get_ports {c0_ddr4_dq[26]}]

set_property PACKAGE_PIN V2 [get_ports {c0_ddr4_dq[25]}]

set_property PACKAGE_PIN AA1 [get_ports {c0_ddr4_dq[24]}]

set_property PACKAGE_PIN Y5 [get_ports {c0_ddr4_dq[23]}]

set_property PACKAGE_PIN W7 [get_ports {c0_ddr4_dq[22]}]

set_property PACKAGE_PIN Y7 [get_ports {c0_ddr4_dq[21]}]

set_property PACKAGE_PIN W9 [get_ports {c0_ddr4_dq[20]}]

set_property PACKAGE_PIN Y6 [get_ports {c0_ddr4_dq[19]}]

set_property PACKAGE_PIN W5 [get_ports {c0_ddr4_dq[18]}]

set_property PACKAGE_PIN W4 [get_ports {c0_ddr4_dq[17]}]

set_property PACKAGE_PIN W8 [get_ports {c0_ddr4_dq[16]}]

set_property PACKAGE_PIN AB6 [get_ports {c0_ddr4_dq[15]}]

set_property PACKAGE_PIN AC6 [get_ports {c0_ddr4_dq[14]}]

set_property PACKAGE_PIN AD9 [get_ports {c0_ddr4_dq[13]}]

set_property PACKAGE_PIN AB7 [get_ports {c0_ddr4_dq[12]}]

set_property PACKAGE_PIN AB4 [get_ports {c0_ddr4_dq[11]}]

set_property PACKAGE_PIN AC7 [get_ports {c0_ddr4_dq[10]}]

set_property PACKAGE_PIN AA4 [get_ports {c0_ddr4_dq[9]}]

set_property PACKAGE_PIN AC9 [get_ports {c0_ddr4_dq[8]}]

set_property PACKAGE_PIN AE5 [get_ports {c0_ddr4_dq[7]}]

set_property PACKAGE_PIN AC1 [get_ports {c0_ddr4_dq[6]}]

set_property PACKAGE_PIN AD5 [get_ports {c0_ddr4_dq[5]}]

set_property PACKAGE_PIN AC4 [get_ports {c0_ddr4_dq[4]}]

set_property PACKAGE_PIN AD4 [get_ports {c0_ddr4_dq[3]}]

set_property PACKAGE_PIN AD2 [get_ports {c0_ddr4_dq[2]}]

set_property PACKAGE_PIN AE2 [get_ports {c0_ddr4_dq[1]}]

set_property PACKAGE_PIN AC2 [get_ports {c0_ddr4_dq[0]}]

set_property PACKAGE_PIN Y3 [get_ports {c0_ddr4_dqs_t[3]}]

set_property PACKAGE_PIN Y8 [get_ports {c0_ddr4_dqs_t[2]}]

set_property PACKAGE_PIN AB9 [get_ports {c0_ddr4_dqs_t[1]}]

set_property PACKAGE_PIN AD3 [get_ports {c0_ddr4_dqs_t[0]}]

set_property PACKAGE_PIN B7 [get_ports {c0_ddr4_dqs_t[7]}]

set_property PACKAGE_PIN D8 [get_ports {c0_ddr4_dqs_t[6]}]

set_property PACKAGE_PIN H7 [get_ports {c0_ddr4_dqs_t[5]}]

set_property PACKAGE_PIN K8 [get_ports {c0_ddr4_dqs_t[4]}]

set_property PACKAGE_PIN AL3 [get_ports {c0_ddr4_odt[0]}]

set_property PACKAGE_PIN AJ7 [get_ports c0_ddr4_act_n]

set_property PACKAGE_PIN AK3 [get_ports c0_ddr4_reset_n]

set_property PACKAGE_PIN G12 [get_ports c0_sys_clk_p]

set_property IOSTANDARD SSTL12_DCI [get_ports {c0_ddr4_cke[0]}]

####################################################################################

# Constraints from file : 'bd_9054_microblaze_I_0.xdc'

####################################################################################

current_instance u_ddr4_0/inst

set_property LOC MMCM_X0Y2 [get_cells -hier -filter {NAME =~ */u_ddr4_infrastructure/gen_mmcme*.u_mmcme_adv_inst}]

set_property CLOCK_DEDICATED_ROUTE BACKBONE [get_pins -hier -filter {NAME =~ */u_ddr4_infrastructure/gen_mmcme*.u_mmcme_adv_inst/CLKIN1}]

current_instance -quiet

set_property INTERNAL_VREF 0.84 [get_iobanks 67]

set_property INTERNAL_VREF 0.84 [get_iobanks 66]

set_property INTERNAL_VREF 0.84 [get_iobanks 65]

set_property BITSTREAM.GENERAL.COMPRESS TRUE [current_design]

set_property IOSTANDARD LVCMOS18 [get_ports led]

set_property C_CLK_INPUT_FREQ_HZ 300000000 [get_debug_cores dbg_hub]

set_property C_ENABLE_CLK_DIVIDER false [get_debug_cores dbg_hub]

set_property C_USER_SCAN_CHAIN 1 [get_debug_cores dbg_hub]

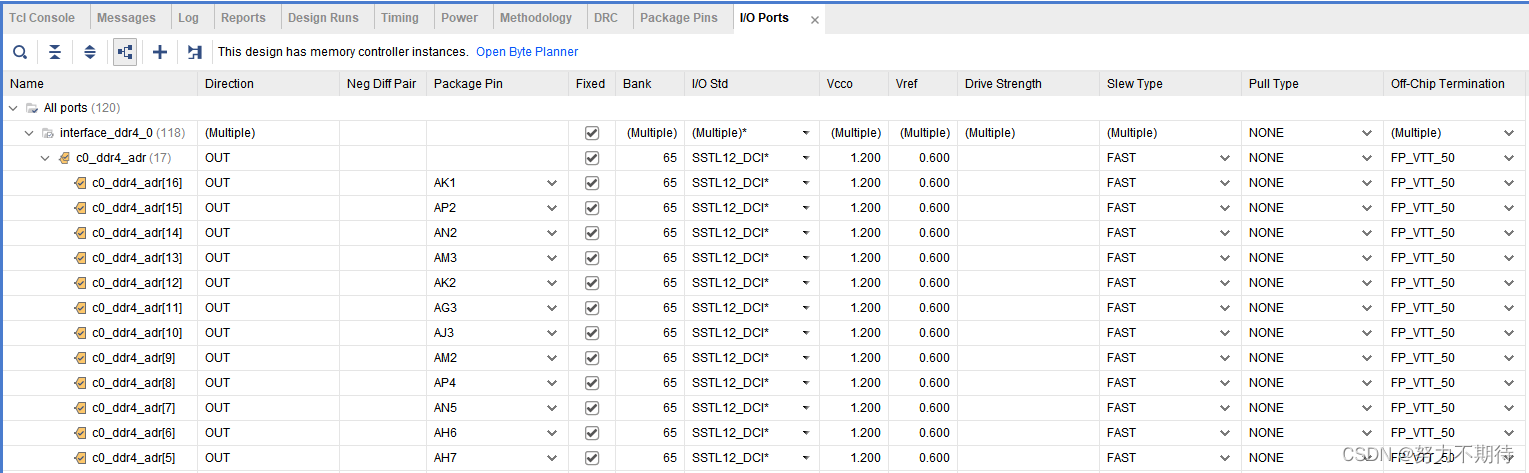

connect_debug_port dbg_hub/clk [get_nets clk]约束文件无需手动填入约束代码,在执行Open Implemented Design后, 在I/O Ports中填入引脚位置和电平约束,Ctrl+S后自动保存到xdc中。

以上代码经过上板测试通过。

本文完。