声明:本系列博客参考有关专业书籍,截图均为自己实操,仅供交流学习!

引入

脉冲宽度调制(PWM)是一种对模拟信号进行数字编码的方法,硬件原理是根据相应载荷的变化来调制晶体管栅极或基极的偏置,来实现开关稳压电源输出晶体管或晶体管导通时间的改变。

一个重要理论:冲量相等而形状不同的窄脉冲加在具有惯性的环节上时,其效果基本相同。

以此为理论基础,对半导体开关元件的导通和关断进行控制得到一系列幅值相等而宽度不相等的脉冲,用这些PWM脉冲来等效正弦波或其他各种波形。按一定规则对各脉冲的宽度进行调制,既可改变逆变电路输出电压大小,也可改变输出功率。

TMS320F28069有19路脉宽调制输出引脚(需要软件进行配置,与普通GPIO类似),包括16路增强型PWM(ePWM)和3路普通PWM(ECap模块复用),其中16路ePWM中有8路可配置为高分辨率的PWM(HRPWM)。

除了19路输出引脚,还有8组PWM模块,每组分2路PWM,分别为PWMA和PWMB(对应16路ePWM)。一个ePWM模块包括:时基模块、计数器比较模块、比较方式预设模块、死区模块、斩波模块、事件触发模块、行程区模块7个模块。

ePWM模块在电机控制、电源管理和其他需要精确时间控制的应用中非常有用!

一、ePWM单路输出

1、ePWM模块可以配置为单路输出模式,这意味着它可以生成一个独立的PWM信号。

2、在单路输出模式下,ePWM模块可以根据预设的周期、占空比和其他参数生成PWM波形。

3、用户可以通过配置ePWM模块的相关寄存器来调整PWM信号的各种参数,如周期、占空比、相位等。

4、ePWM模块还具有死区时间生成功能,可以防止上下桥臂的功率开关管同时导通,从而避免短路。

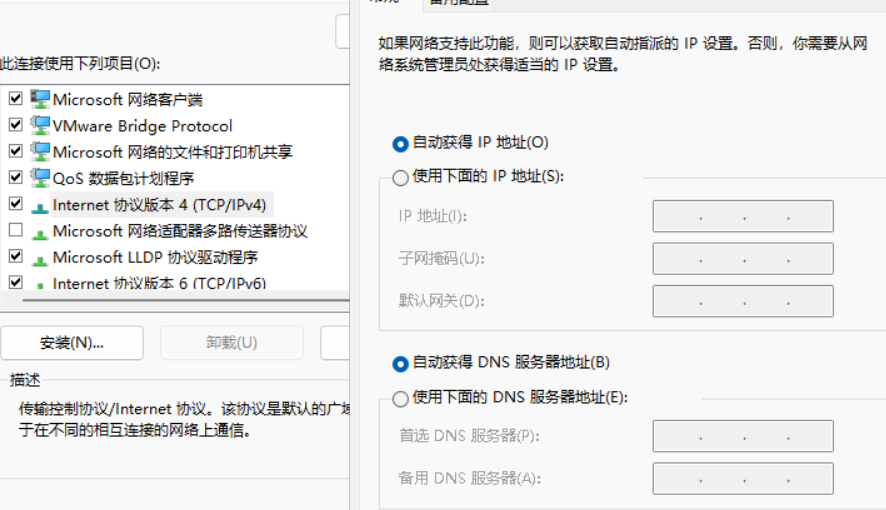

ePWM模块的输入时钟来自系统时钟,可根据需要调节分频系数。选择ePWM模块进行如下配置:

TBCLK = SYSCLKOUT/(HSPCLKDIV*CLKDIV)

这个公式表示了如何从一个系统的主时钟 (SYSCLKOUT) 导出另一个时钟 (TBCLK)。

让我们分解这个公式:

SYSCLKOUT:这是系统的主时钟输出频率。这通常是微控制器或处理器的核心时钟频率。

HSPCLKDIV:这是高速预分频器的值。预分频器通常用于降低时钟频率。例如,如果HSPCLKDIV的值为2,那么时钟频率就会被除以2。

CLKDIV:这是另一个分频器的值。和预分频器一样,分频器也用于降低时钟频率。

所以,TBCLK 是由 SYSCLKOUT 经过两次分频后得到的。首先,SYSCLKOUT 被 HSPCLKDIV 分频,然后再被 CLKDIV 分频。最后得到的时钟频率就是 TBCLK。

举个例子,如果 SYSCLKOUT 是 100 MHz,HSPCLKDIV 是 2,CLKDIV 是 4,那么 TBCLK 将会是:

(TBCLK = \frac{100 MHz}{(2 * 4)})

(TBCLK = 12.5 MHz)

这意味着从 SYSCLKOUT 得到的 TBCLK 是 12.5 MHz。本次使用的系统主时钟SYSCLKOUT为80MHz,取HSPCLKDIV为4分频,CLKDIV取2,则TBCLK为10MHz,设置周期寄存器值10000(如上配置图),则ePWM1的输出频率10MHz/10000=1kHz。

在配置框使能ePWMA,当计数等于0时不动作,等于CAU的值时复位,等于CAD的值时置高,其他时间不动作。ePWM、死区时间、事件触发以及错误联防均不配置。

最后配置Counter Compare,CMPA值50,即占空比为50%。

二、ePWM双路互补输出

1、ePWM模块还支持双路互补输出模式,

这种模式常用于电机控制中的H桥驱动。

2、在双路互补输出模式下,ePWM模块可以生成两个

互补的PWM信号,分别用于控制H桥的上下两个开关管。

3、这两个互补的PWM信号具有相同的周期和占空比,

但相位相差180度,从而确保H桥的两个开关管不会同时导通。

4、通过合理配置ePWM模块的参数,可以实现电机的正反转、调速等功能。首先对于Genaral和ePWMA的配置如上单路输出,双路输出还需配置ePWMB,与ePWMA的配置相反。

对于Counter Compare的配置如下:

三、ePWM中断

1、ePWM模块还支持中断功能,这意味着当ePWM模块的状态发生变化或满足某些条件时,

可以触发一个中断请求。

2、中断功能可以帮助用户实时监控ePWM模块的状态和性能,

从而及时采取相应的措施。

3、例如,当ePWM模块的输出状态发生变化时,可以触发一个中断请求,

然后在中断服务程序中执行相应的操作,如调整PWM参数、记录日志等。在前面配置的基础上改动,在配置框Event Trigger选项中,使能ePWM中断,并配置为第一个事件发生时就进入中断,其他保持默认:

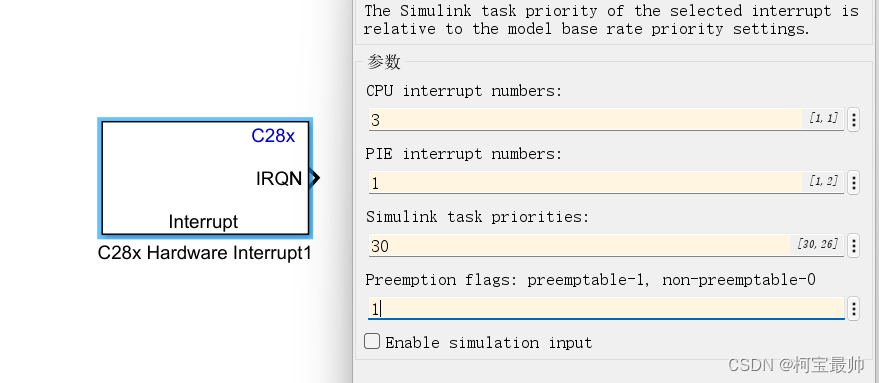

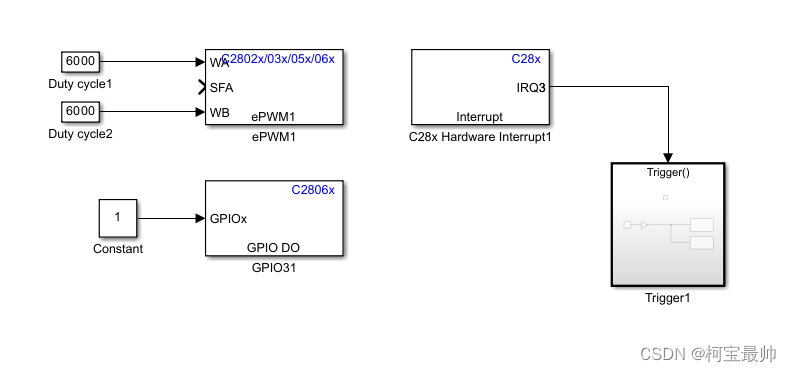

然后使用Simulink的C28x Hardware Interrupt模块,设置好PWM1中断的CPU中断号3和PIE级中断号1写入。

如下是ePWM中断实现的实现图:(右下角为中断函数,可根据需要添加逻辑,可使用StateFlow模块进搭建逻辑图)

StateFlow是一个基于有限状态机和流程图来构建组合和时序逻辑决策模型并进行仿真的环境。它由MathWorks公司开发,并作为Simulink的一个附加模块提供。StateFlow可以用于设计有关监控、任务调度以及故障管理应用程序的逻辑。

StateFlow的主要特点包括:

基于状态机的建模:StateFlow允许用户创建和管理复杂的状态机模型,这些模型可以描述系统在不同状态下的行为和转换。

图形化设计界面:StateFlow提供了一个直观的图形界面,使用户可以轻松地创建状态图、流程图和数据流图来描述系统的行为。

强大的仿真功能:StateFlow支持实时仿真和离线仿真,可以对模型进行详细的仿真分析和验证。

与Simulink的无缝集成:StateFlow可以直接嵌入到Simulink模型中,与Simulink的算法设计和代码生成环境完美集成。

丰富的控制流功能:StateFlow提供了丰富的控制流功能,包括顺序、分支和循环等,以支持复杂的逻辑设计。

写到这里有点学不下去了,呜呜呜,没硬件有点没着力点!请允许我浅浅纸上谈兵,可能学到后面的系统级仿真会有趣点,希望我可以坚持写下去吧!

往期精彩

STM32专栏(付费9.9)![]() http://t.csdnimg.cn/E2F88

http://t.csdnimg.cn/E2F88

OpenCV-Python专栏(付费9.9)![]() http://t.csdnimg.cn/zK1jV

http://t.csdnimg.cn/zK1jV

AI底层逻辑专栏(付费9.9)![]() http://t.csdnimg.cn/zic0f

http://t.csdnimg.cn/zic0f

机器学习专栏(免费)![]() http://t.csdnimg.cn/FaXzAFreeRTOS专栏(免费)

http://t.csdnimg.cn/FaXzAFreeRTOS专栏(免费)![]() http://t.csdnimg.cn/SjIqU电机控制专栏(免费)

http://t.csdnimg.cn/SjIqU电机控制专栏(免费)![]() http://t.csdnimg.cn/FNWM7

http://t.csdnimg.cn/FNWM7