忆阻器Crossbar阵列是一种先进的神经网络硬件实现技术,它利用忆阻器的物理特性来模拟神经网络中的突触连接,为人工智能和机器学习应用提供了一种高效、低能耗的计算平台。本文将深入探讨忆阻器Crossbar阵列的基本原理及其在Read(读取)和Update(更新)阶段的工作机制。

Crossbar阵列的三种导线WL/BL/SL

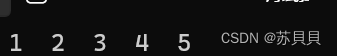

忆阻器Crossbar阵列是由交叉的金属线(Bit Lines, BL和Word Lines, WL)以及位于交叉点的忆阻器构成的矩阵结构。这种结构中还包含了Source Lines(SL),用于传输通过忆阻器的电流。BL、WL和SL共同协作,使得Crossbar阵列能够执行复杂的计算任务。

BL (Bit Lines)

BL通常用于传输输入信号或读取操作中的电流信号。在神经网络的模拟中,BL可以视为输入神经元,负责提供输入向量。

WL (Word Lines)

WL在写入(Update)阶段用于施加更新电压,控制忆阻器的电导值,即模拟突触权重的调整。WL在读取过程中也起到激活特定忆阻器行的作用。

SL (Source Lines)

通常作为源极线使用,为忆阻器提供参考电压或用于在编程和写入操作中建立电流路径。

前向传播阶段(Read阶段)

在Read阶段,忆阻器Crossbar阵列通过BL和SL实现输入信号的前向传播。具体步骤如下:

1.输入信号施加

输入电压

V

j

V_j

Vj通过BLj施加到crossbar的一侧(列信号),即忆阻器的一端。

2.计算电流

令此时WLj的电压为零,SLj的电压恒定为零,则从BLi到SLj的电压降刚好等于

V

j

V_j

Vj。设第i行第j列的忆阻器的电导为

G

i

,

j

G_{i,j}

Gi,j,则传输到SLj的电流为

I

j

=

V

i

⋅

G

i

,

j

I_j=V_i\cdot G_{i,j}

Ij=Vi⋅Gi,j。

3.MAC电学运算

当电压向量通过所有列(BL1-BLn)输入到crossbar内,则SLi将汇总通过这一列的忆阻器的所有电流,即:

I

j

=

∑

i

=

1

n

V

i

⋅

G

i

,

j

I_j=\sum^{n}_{i=1}{V_i\cdot G_{i,j}}

Ij=∑i=1nVi⋅Gi,j

对应神经网络中的前向传播运算:

y

j

=

∑

i

=

1

n

x

i

⋅

W

i

,

j

y_j=\sum^{n}_{i=1}{x_i\cdot W_{i,j}}

yj=∑i=1nxi⋅Wi,j

对于权重如何与电导对应上,可参考文献[1][2]当中的差分对放大电路。

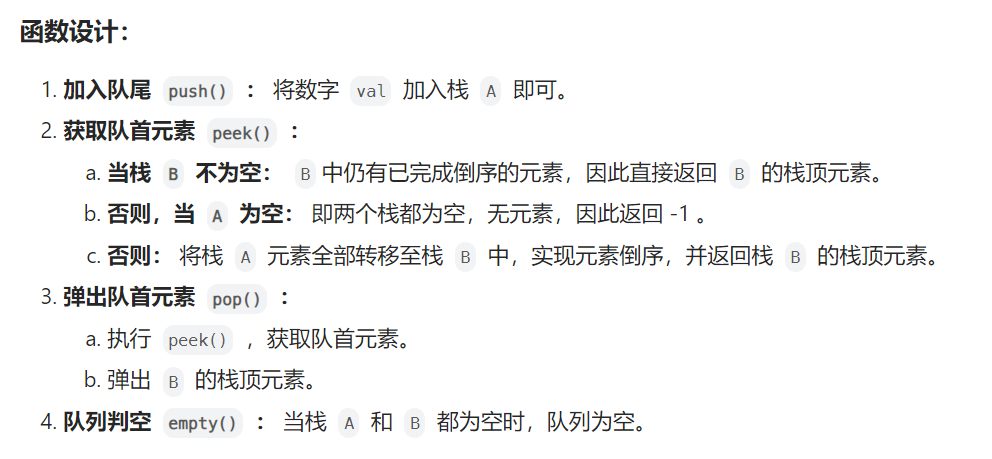

反向传播阶段(Update阶段)

在忆阻神经网络中,BP机制决定的权重更新量实际由电导的更新量来决定。假设现在需要对器件(i,j)进行更新(SET或RESET),SET脉冲强度为4.5 V(RESET同理,只是极性相反)。设

V

W

L

=

5

V

V_{WL}=5\;V

VWL=5V,则:

V

W

L

i

−

V

B

L

j

=

V

s

e

t

=

4.5

V

⇒

V

B

L

j

=

0.5

V

V_{WLi}-V_{BLj}=V_{set}=4.5\;V\Rightarrow V_{BL_j}=0.5\;V

VWLi−VBLj=Vset=4.5V⇒VBLj=0.5V

因此在更新阶段,write脉冲是由WL提供的,而BL此时起到的是选通的作用,使SET脉冲刚好能够施加给需要更新的器件,同时避免改变不需要更新的器件。例如,若不能改变第i行的其他器件时,则此时必定满足:

V

B

L

k

=

V

W

L

i

(

k

≠

j

)

V_{BLk}=V_{WL_i}\;(k\neq j)

VBLk=VWLi(k=j)

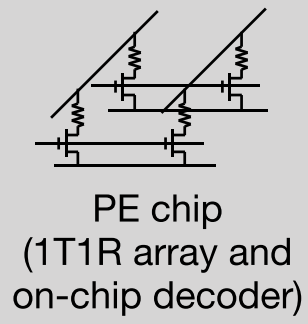

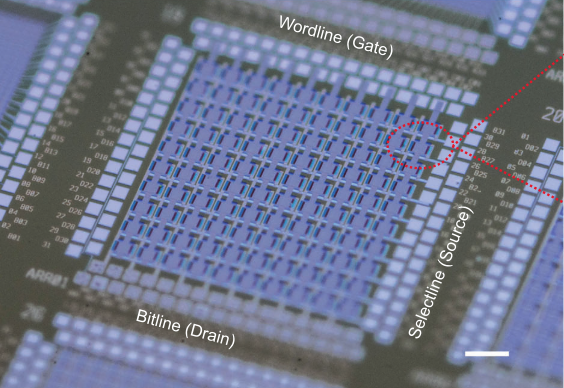

1T1R结构

在1T1R结构中,每个忆阻器的一端与一个晶体管相连,形成一个1T1R单元。这种结构使得可以通过晶体管的门极控制对忆阻器的精确访问,从而实现对忆阻器电导的细致调整。

- **源极(Source)**连接到源线(SL,Source Line)。

- **漏极(Drain)**连接到忆阻器的上电极,而忆阻器的下电极则连接到位线(BL,Bit Line)。

- **栅极(Gate)**通过字线(WL,Word Line)进行控制,所有在同一行的晶体管的栅极都连接到同一条字线上。

这种1T1R结构的设计使得通过调节栅极上的电压,可以控制源极和漏极之间的电流,从而实现对忆阻器电导的精确调整。这种方式不仅提高了对忆阻器的选择性和控制能力,还增强了阵列的可靠性和稳定性,因为晶体管可以有效防止非目标忆阻器因电压泄露而被意外写入。通过在每个忆阻器单元中加入一个晶体管,1T1R结构有效隔离了每个单元,只有当晶体管被开启时,电流才能流过忆阻器,这样就大大减少了非目标忆阻器的误激活,从而减少了串扰。此外,晶体管还可以提供更精细的电流控制,进一步提高了写入操作的准确性和重复性。总之,1T1R结构通过为每个忆阻器提供独立的访问通道,有效减少了串扰,提高了阵列的数据准确性和稳定性,这对于实现高密度、高可靠性的忆阻器存储和计算系统至关重要。

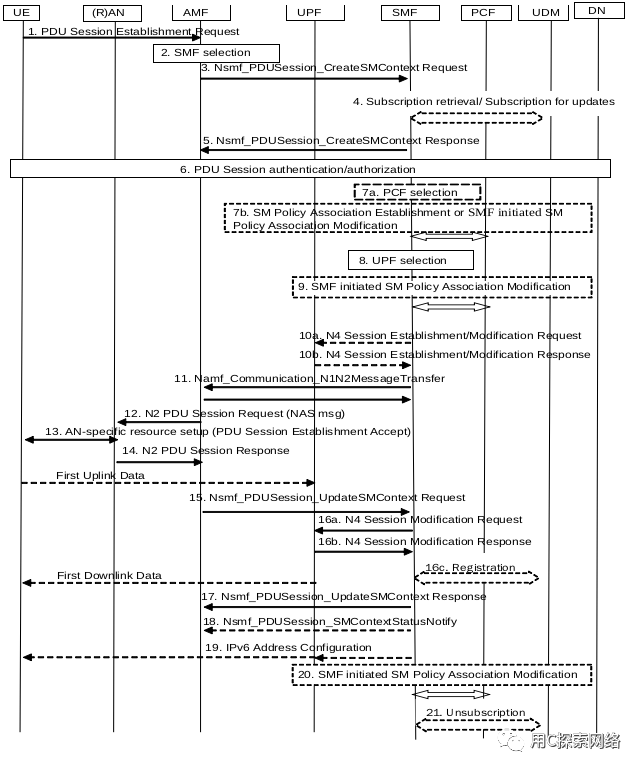

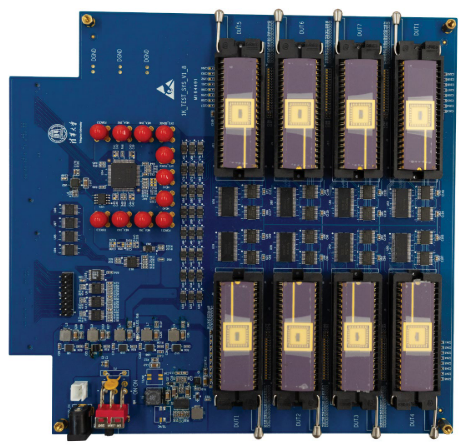

以上内容均参考清华大学吴华强课题组的阵列设计[1],但要注意的是针对crossbar的控制线路并非只有这一种,例如浙江大学林芃教授团队的工作便采用WL与BL平行的策略[3]:

但是交叉控制与通信的基本思路是一致的,换汤不换药。

参考文献

[1] Yao, Peng, et al. “Fully hardware-implemented memristor convolutional neural network.” Nature 577.7792 (2020): 641-646.

[2] Zhang, Wei, et al. “Hardware‐Friendly Stochastic and Adaptive Learning in Memristor Convolutional Neural Networks.” Advanced Intelligent Systems 3.9 (2021): 2100041.

[3] Chen, Peng, et al. “Open-loop analog programmable electrochemical memory array.” Nature Communications 14.1 (2023): 6184.