文章目录

- 1 画一个1.8V转3.3V升压电路。

- 2 用NMOS设计一个双向电平转换电路,及原理

- 3 三分频电路的设计

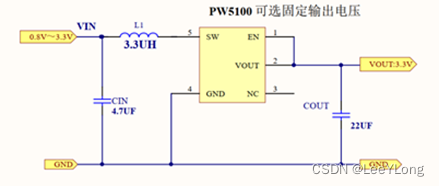

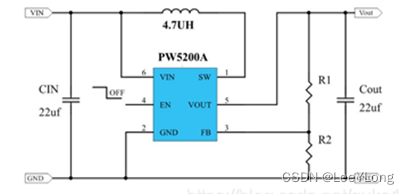

1 画一个1.8V转3.3V升压电路。

升压:1.8V升3.3V升压芯片方案,如PW5100,固定输出3V、3.3V,输入电压范围0.7V-5V,输出电流最大是500MA,输入静态功耗是10uA。

1.8V升3V升压芯片方案,如PW5200A,可调输出电压版本,2.5V-5V之间输出电压,输入电压是在1V-4.4V的范围。输出电流最大500MA.

电平转换:

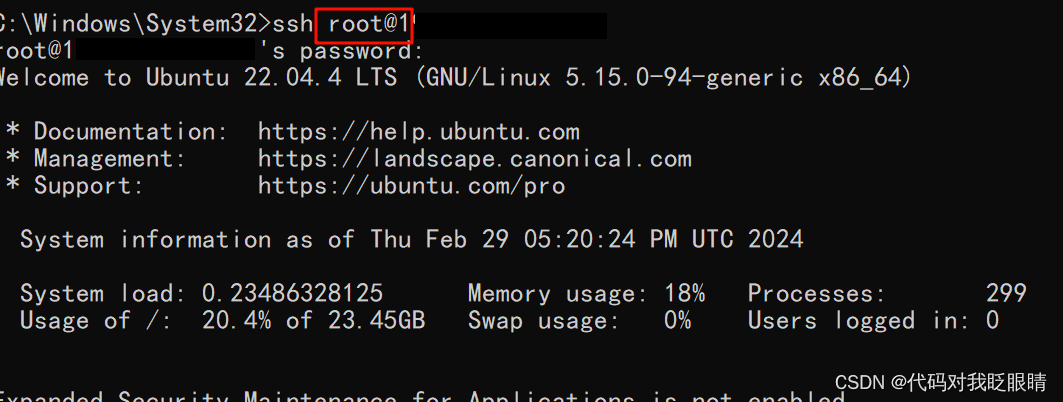

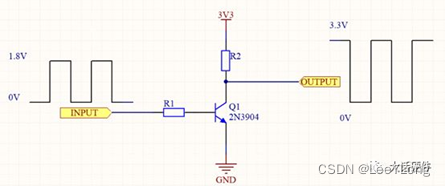

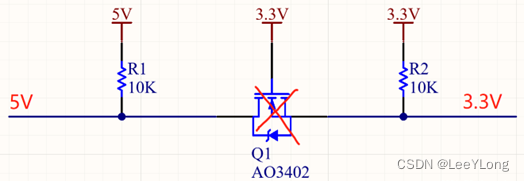

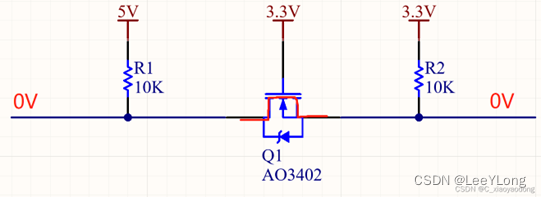

2 用NMOS设计一个双向电平转换电路,及原理

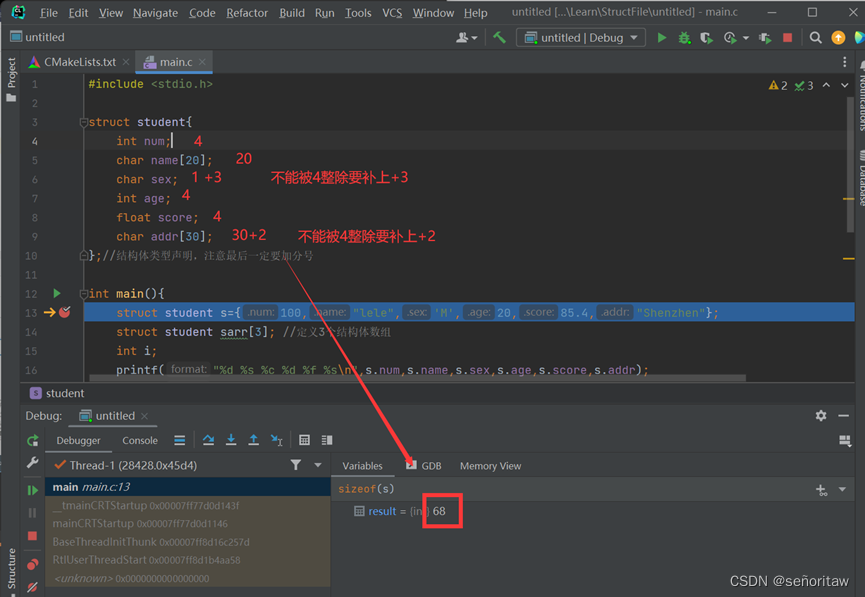

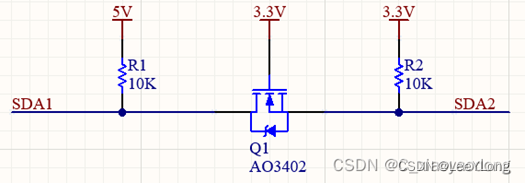

该电路是通过增强型NMOSFET的符号来实现的。

原理详:(137条消息) 基于NMOSFET的电平转换电路设计(详细版)_nmos电平转换

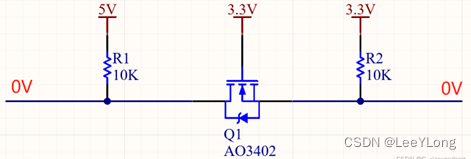

5V→3.3V:①当左边输入5V时,UGS=0V(UG=3.3V、US=3.3V),所以NMOSFET截止,DS不导通,所以右边电平被拉到了3.3V。

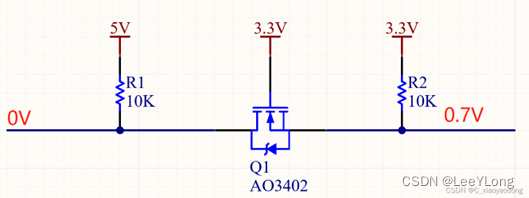

②当左边输入0V时,右边为3.3V。这时NMOS管下面的二极管导通,右边电位被钳位在0.7V左右。

这时的UGS=2.6V,NMOS管被导通,DS可以流过电流。由于D和S间的电压比二极管的电压小,所以二极管被短路了,右边电压变成了0V。如下图5.1.2.2所示。(AO3402的UGS(th)大约在1.5V左右。右边电压不是准确的0V,由于RDS电阻的存在,右边大概几百mV到几十mV。)

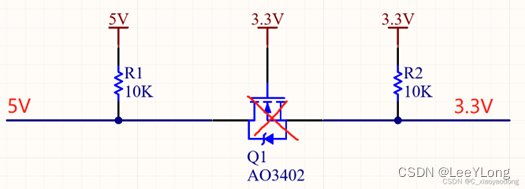

3.3V→5V:①当右边电压为3.3V,UGS=0V,NMOS管被截止,左边电平就会被拉到5V。

① 当右边电压为0V时,UGS=3.3V,这时NMOS管导通,左边电压为0V。

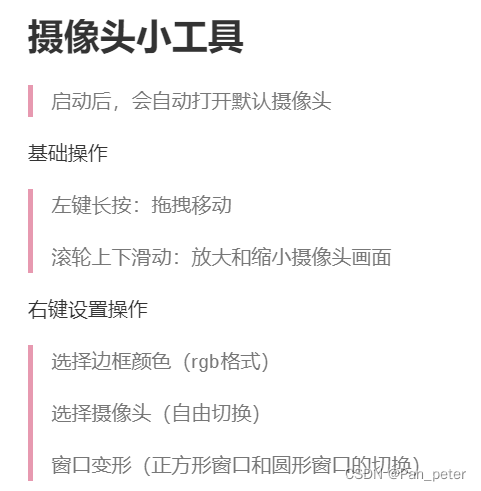

3 三分频电路的设计

详见: 常用电路设计——“分频电路” - 知乎 (zhihu.com)

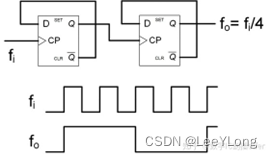

1、 偶数分频:(1) 用D触发器级联实现 ;(2) 用计数器实现

2、奇数分频:(1) 占空比非50%的奇数分频;用Moore状态机实现

;用计数器实现

利用基本逻辑单元直接搭建占空比为50%的奇数分频电路

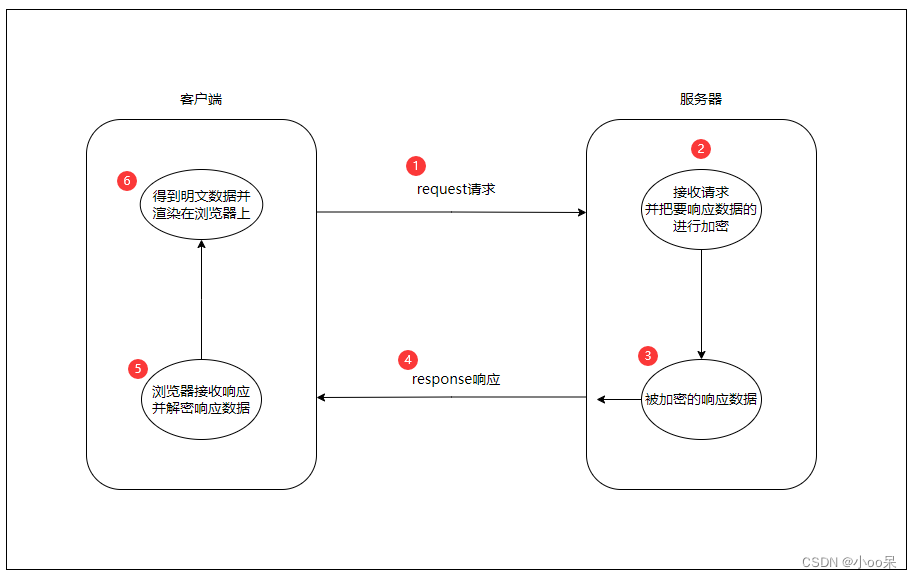

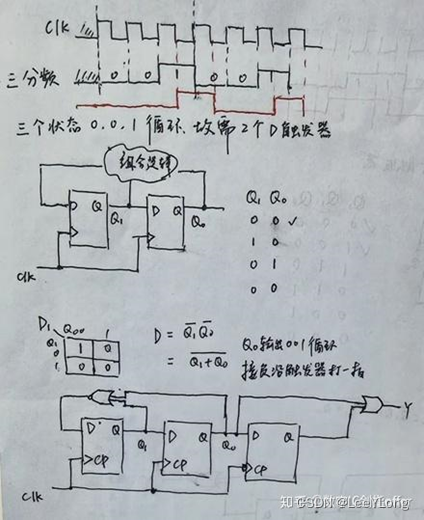

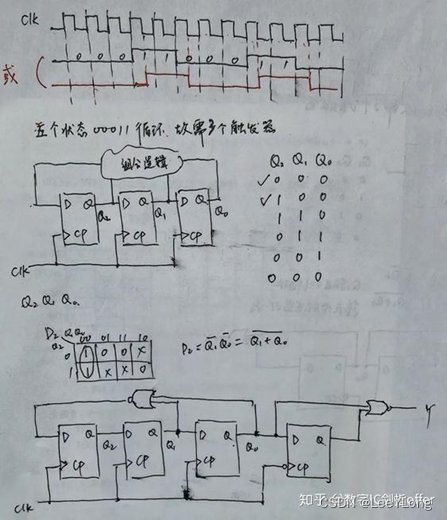

思路:先使用触发器构成序列生成器,输出001循环脉冲,实现占空比非50%的三分频,然后用负沿触发器打一拍,再相或。由于001循环共三个状态,故需2个D触发器。通过列状态表、画卡诺图,得到由两个D触发器及逻辑门构成的001序列生成器,后接负沿触发器打一拍并将其输出与序列生成器的输出相或,即得到占空比为50%的三分频电路。

下面贴出三分频和五分频电路的简略设计思路及过程仅供参考,如图4、图5所示。

法二:图2是3分频电路,用JK-FF实现3分频很方便,不需要附加任何逻辑电路就能实现同步计数分频。但用D-FF实现3分频时,必须附加译码反馈电路,如图2所示的译码复位电路,强制计数状态返回到初始全零状态,就是用NOR门电路把Q2,Q1=“11B”的状态译码产生“H”电平复位脉冲,强迫FF1和FF2同时瞬间(在下一时钟输入Fi的脉冲到来之前)复零,于是Q2,Q1=“11B”状态仅瞬间作为“毛刺”存在而不影响分频的周期,这种“毛刺”仅在Q1中存在,实用中可能会造成错误,应当附加时钟同步电路或阻容低通滤波电路来滤除,或者仅使用Q2作为输出。D-FF的3分频,还可以用AND门对Q2,Q1译码来实现返回复零。

注:

在本文中,我借鉴了互联网上的一些内容,以总结面试经验和技巧。这些内容旨在为读者提供实用的指导和参考。然而,由于个人经验和认知的局限性,本文的总结可能存在不准确或遗漏之处。因此,我真诚地欢迎读者朋友们提出宝贵的意见和建议,以帮助我改进和完善这些内容。

此外,有些知识点参考了其他博主,可能由于疏忽未注明出处。这些借鉴的部分旨在提供更多信息和观点,以丰富和完善文章的主题。在此,我对所借鉴的来源表示感谢。此外,为确保所引用的内容均符合版权规定,以维护知识产权和学术道德。若文中任何内容侵犯了您的合法权益,请相关权益人及时与我联系,我将立即进行核实并采取适当措施,包括但不限于删除相关内容或更新文章以消除影响。