引言

手头的FPGA开发板上有一个千兆网口,最近准备做一下以太网通信的内容。本文先介绍基本的理论知识。

FPGA芯片型号:xc7a35tfgg484-2

网口芯片(PHY):RTL8211

网络接口:RJ45

简述以太网

什么以太网?

以太网是一种计算机局域网技术。IEEE组织的IEEE 802.3标准制定了以太网的技术标准,它规定了包括物理层的连线、电子信号和介质访问层协议的内容。以太网是应用最普遍的局域网技术。

常用的传输速率

以太网传输速率:10Mbps、100Mbps、1000Mbps、10Gbps

硬件接口

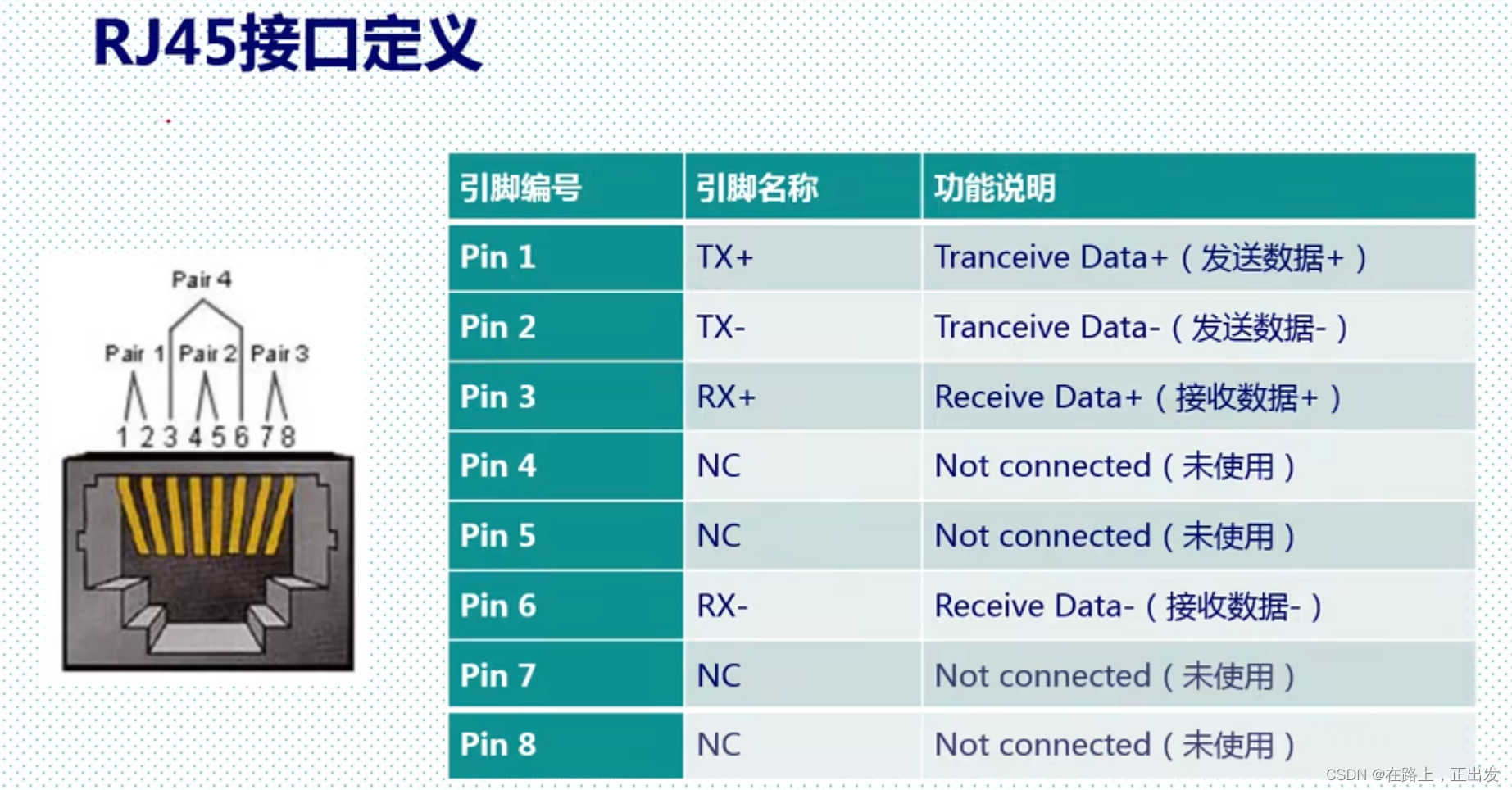

以太网的接口类型有,RJ45接口、RJ11接口,SC光纤接口等。RJ45的接口插头和插座的示意图:

RJ-45接口定义:

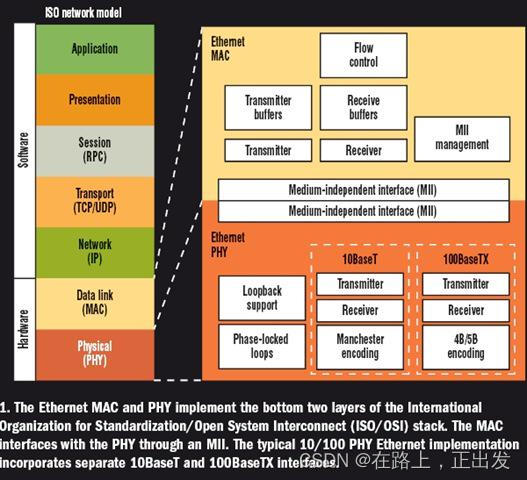

关于MAC与PHY

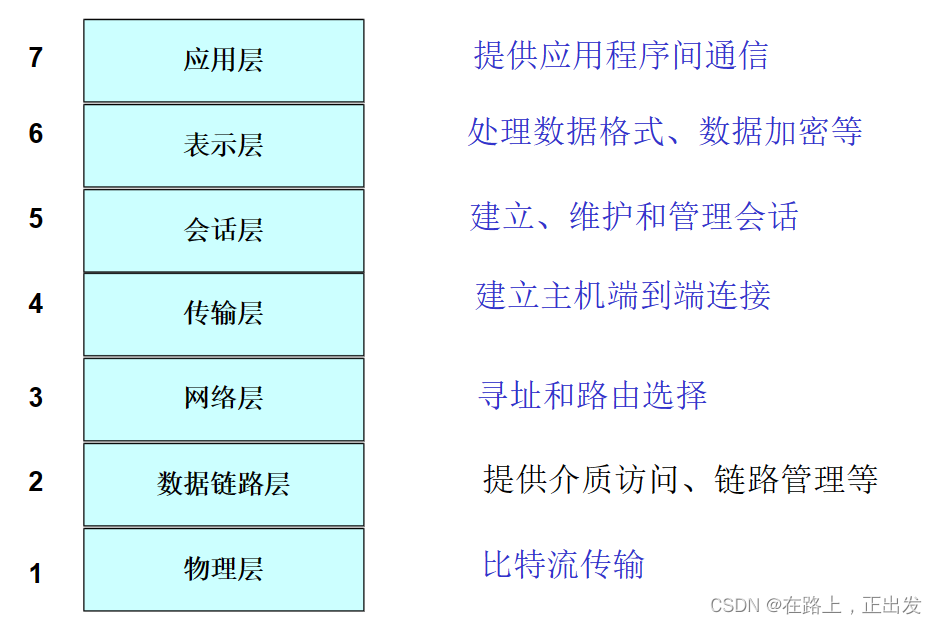

OSI模型

提到以太网,就要先简单说下 OSI(Open System Interconnection) 7层网络模型:

应用层:网络服务与最终用户的一个接口。协议有HTTP 、FTP、 TFTP、 SMTP、 SNMP、 DNS、 TELNET、 HTTPS、 POP3、 DHCP

表示层:数据的表示、安全、压缩。格式有,JPEG、ASCll、EBCDIC、加密格式等

会话层:建立、管理、终止会话。对应主机进程,指本地主机与远程主机正在进行的会话

传输层:定义传输数据的协议端口号,以及流控和差错校验。协议有TCP、 UDP,数据包一旦离开网卡即进入网络传输层

网络层:进行逻辑地址寻址,实现不同网络之间的路径选择。协议有ICMP、 IGMP 、IP(IPV4 IPV6)

数据链路层:建立逻辑连接、进行硬件地址寻址、差错校验等功能。(由底层网络定义协议)将比特组合成字节进而组合成帧,用MAC地址访问介质,错误发现但不能纠正。

物理层:建立、维护、断开物理连接。(由底层网络定义协议)

对于FPGA实现以太网数据传输(主要是局域网)来说,最主要的就是 数据链路层、 物理层。

MAC

MAC(Media Access Control Address)就是媒体接入控制器。以太网MAC由IEEE-802.3以太网标准定义。它实现了一个数据链路层。最新的MAC同时支持10/100/1000Mbps速率。通常情况下,它实现MII/GMII/RGMII接口,来同行业标准PHY器件实现接口。

对于FPGA的应用来说,MAC层的实现就在 FPGA侧通过RTL代码编程实现。

MAC地址

MAC地址也叫物理地址、硬件地址,由网络设备制造商生产时烧录在网卡的EPROM。IP地址与MAC地址在计算机里都是以二进制表示的,IP地址是32位的,而MAC地址则是48位的 。

MAC地址的长度为48位(6个字节),通常表示为12个16进制数,如:00-16-EA-AE-3C-40就是一个MAC地址,其中前3个字节,16进制数00-16-EA代表网络硬件制造商的编号,它由IEEE(电气与电子工程师协会)分配,而后3个字节,16进制数AE-3C-40代表该制造商所制造的某个网络产品(如网卡)的系列号。只要不更改自己的MAC地址,MAC地址在世界是唯一的。

PHY

PHY是物理接口收发器,它实现物理层。IEEE-802.3标准定义了以太网PHY。它符合IEEE-802.3k中用于10BaseT和100BaseTX的规范。

开发板上用到的网络芯片 RTL8211就是负责物理层。

PHY芯片在发送数据时,首先将MAC发过来的并行数据转化为串行流数据,按照物理层的编码规则把数据编码转换为模拟信号通过网口发送出去,接收数据的流程反之。

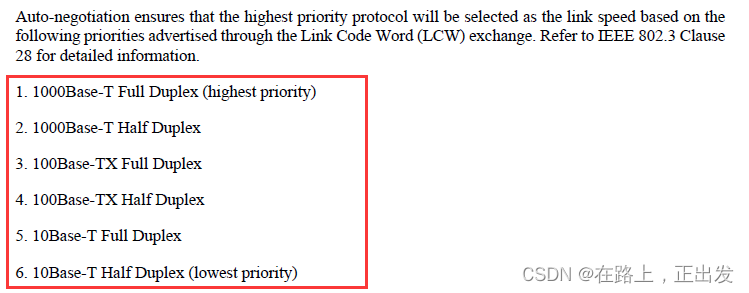

当我们给网卡接入网线的时候,PHY芯片不断发出脉冲信号来检测对端是否有设备,它们通过标准的“语言”交流,互相协商并确定连接速度、双工模式、是否采用流控等。通常情况下,协商的结果是两个设备中能同时支持的最大速度和最好的双工模式。这个技术被称为自动协商。

附:RTL8211芯片手册给出的IEEE802.3自协商优先级规定:

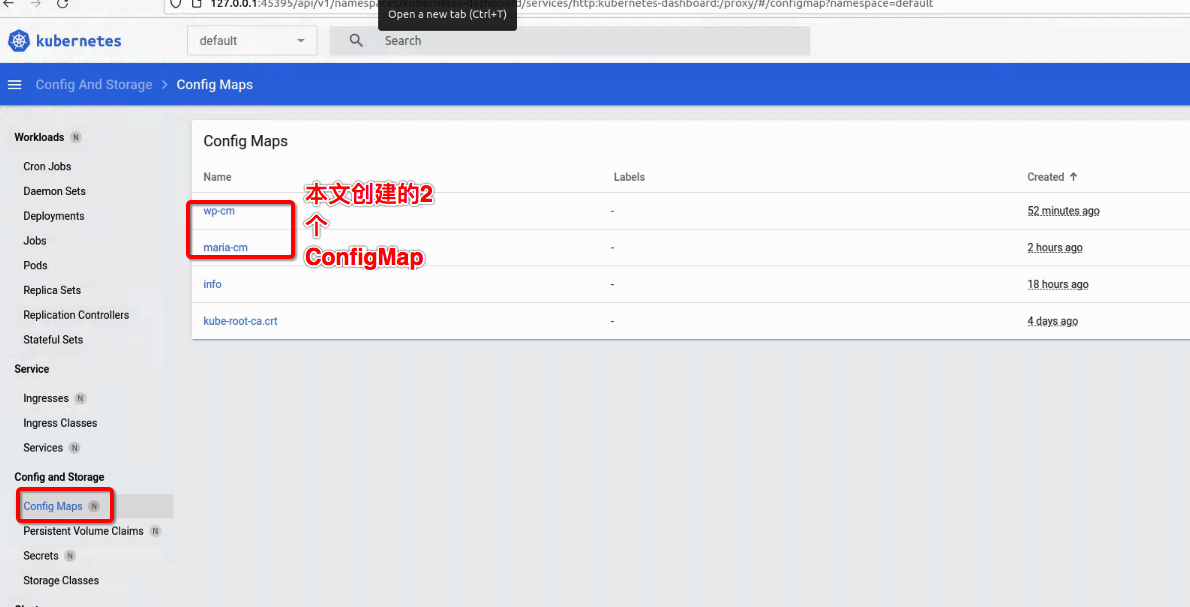

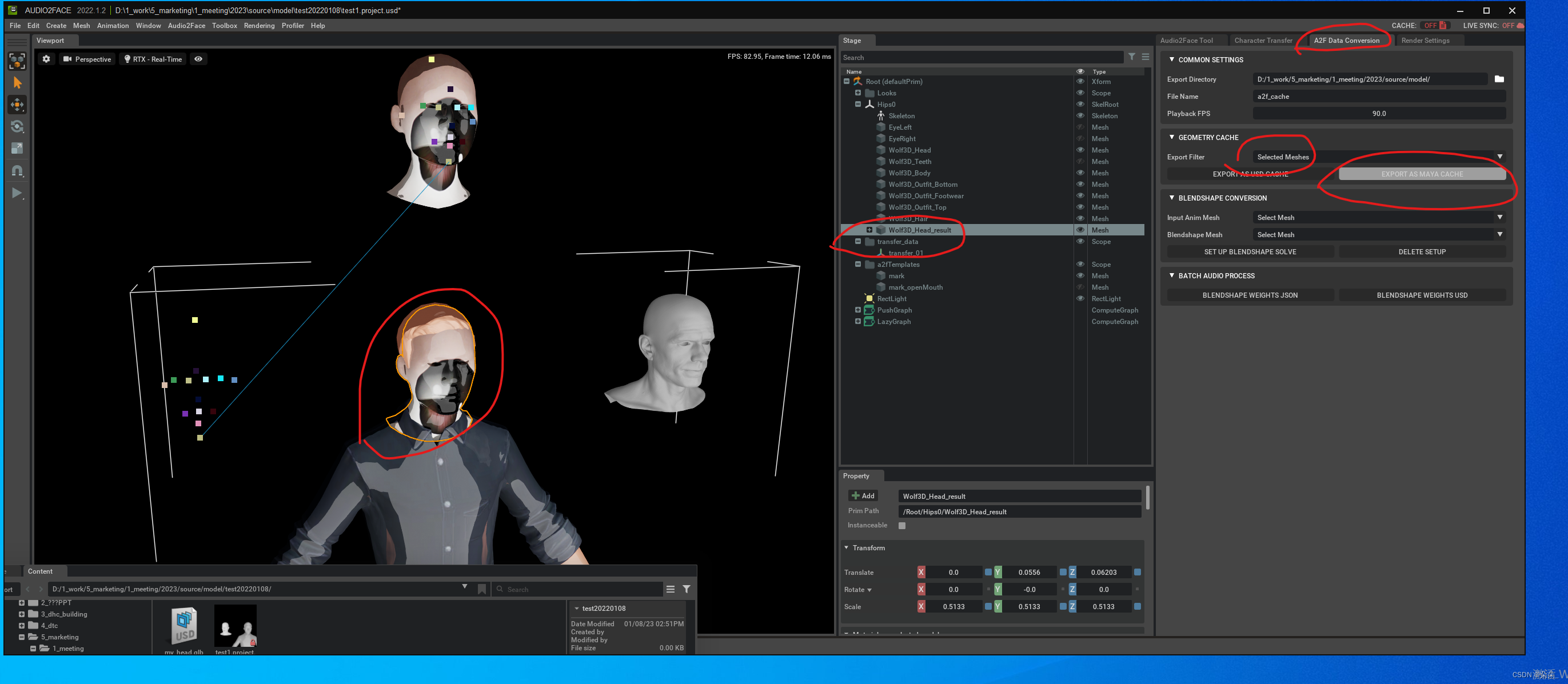

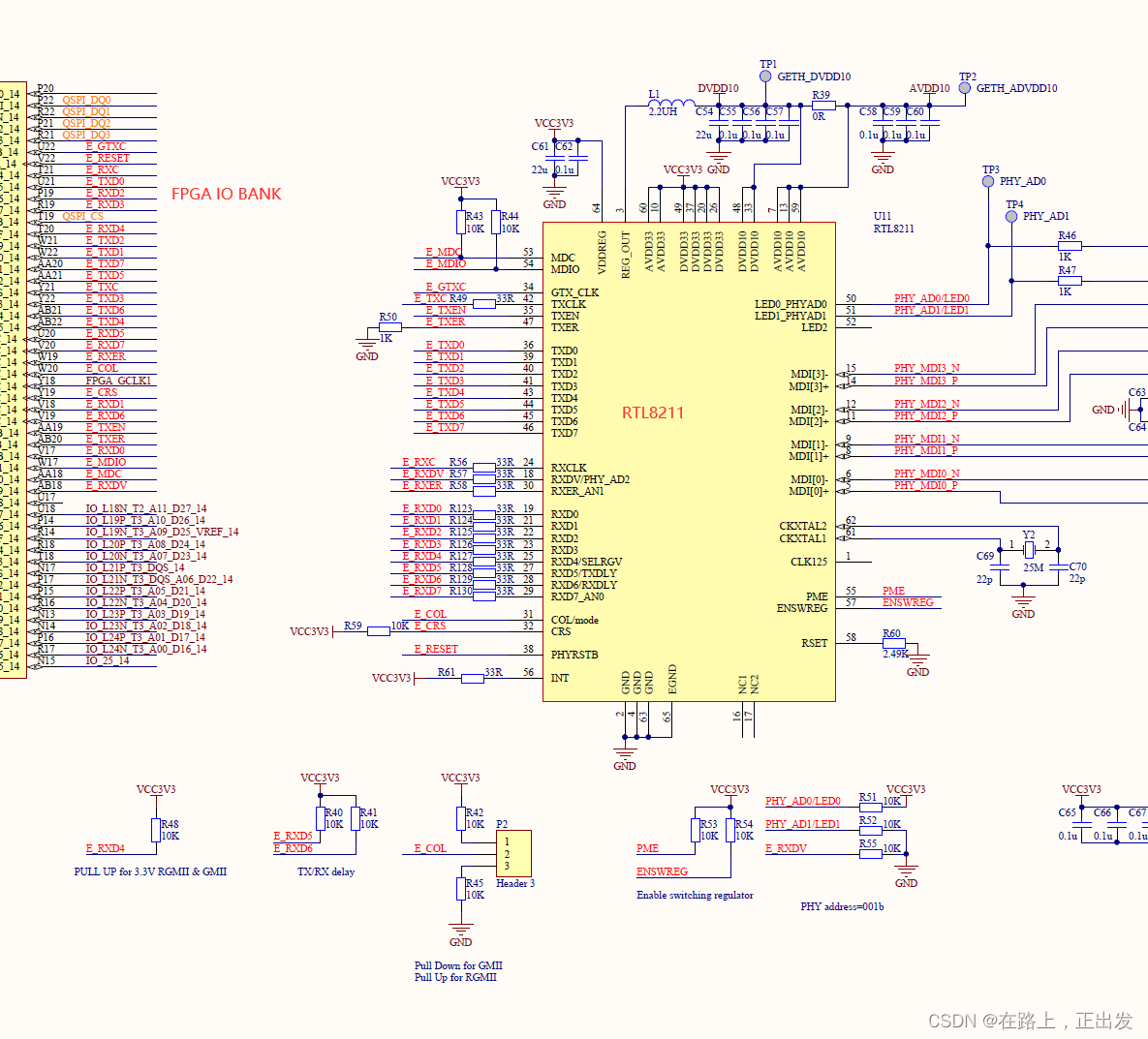

FPGA与PHY芯片、网络接口的连接关系:

MII接口时序介绍

MII(Medium Independent Interface)媒体独立接口,主要针对十兆/百兆以太网通信。

引脚连接示意图

针脚含义说明

针脚名称 | 输入/输出 (相对MAC侧而言) | 位宽 | 含义 |

TX_ER | 输出 | 1 | Transmit Error,发送数据错误提示信号; 同步于TX_CLK,高电平有效,表示TX_ER 有效期内传输的数据无效。 对于10Mbps 速率下,TX_ER 不起作用。 |

TX_EN | 输出 | 1 | Transmit Enable,发送使能信号,只有在TX_EN 有效(高电平)期内传的数据才有效。 |

TX_CLK | 输入 | 1 | 发送数据参考时钟。 🔶100Mbps 速率下,时钟频率为 25MHz。 🔷10Mbps 速率下,时钟频率为 2.5MHz 。 该时钟是由 PHY侧提供。 |

TXD | 输出 | 4 | TransmitData ,数据发送信号,共 4 根信号线。 |

RX_ER | 输入 | 1 | Receive Error 接收数据错误提示信号; 同步于 RX_CLK高电平有效,表示 RX_ER 有效期内传输的数据无效。对于10Mbps 速率下, RX_ER 不起作用 。 |

RX_DV | 输入 | 1 | Reveive Data Valid 接收数据有效信号;拉高时表示接收数据有效。 |

RXD | 输入 | 4 | ReceiveData ,数据接收信号,共 4 根信号线。 |

RX_CLK | 输入 | 1 | 接收数据参考时钟。 🔶100Mbps 速率下,时钟频率为 25MHz。 🔷10Mbps 速率下,时钟频率为 2.5MHz 。 该时钟是由 PHY侧提供。 |

CRS | 输入 | 1 | Carrier Sense ,载波侦测信号,不需要同步于参考时钟,只要有数据传输, CRS 就有效 。 需要注意的是 CRS 只有 PHY在半双工模式下有效 。 |

COL | 输入 | 1 | Collision Detectd ,冲突检测信号,不需要同步于参考时钟 。 需要注意的是 CRS 只有 PHY 在半双工模式下有效 |

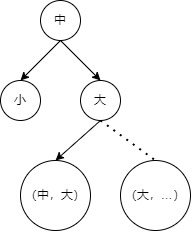

收发时序

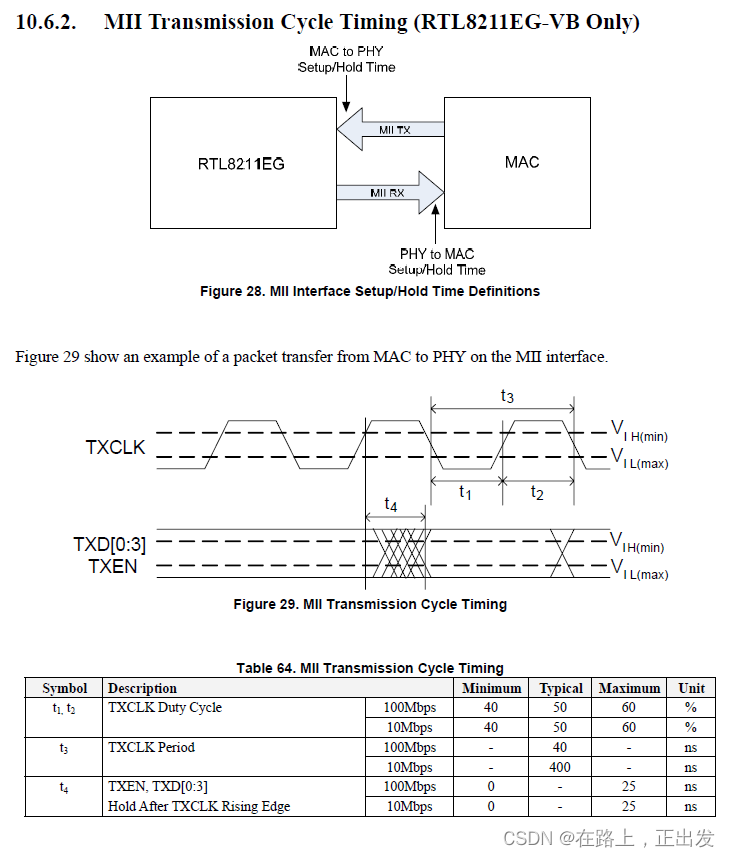

发送时序

MAC 侧向 PHY 侧传输数据的时序图如下:

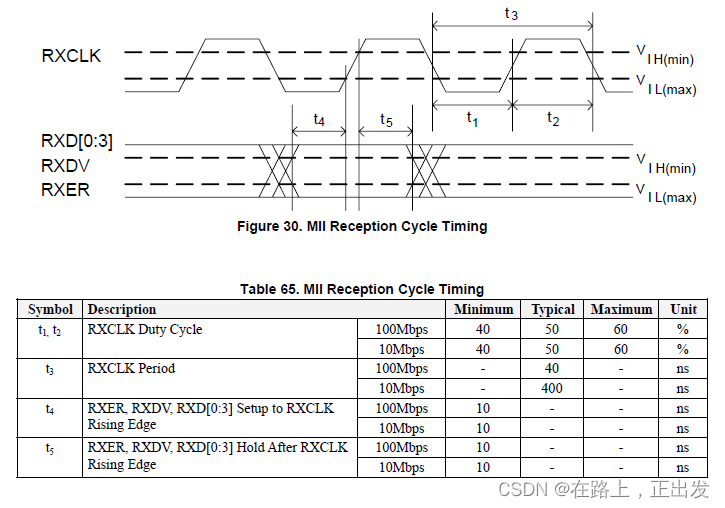

接收时序

PHY 侧向 MAC 侧传输数据的时序图如下:

GMII接口时序介绍

GMII(Gigabit Medium Independent Interface)媒体独立接口,主要针对十兆/百兆/千兆以太网通信。

引脚连接示意图

针脚含义说明

针脚名称 | 输入/输出 (相对MAC侧而言) | 位宽 | 含义 |

TX_ER | 输出 | 1 | Transmit Error,发送数据错误提示信号; 同步于GTX_CLK,高电平有效,表示TX_ER 有效期内传输的数据无效。 对于10Mbps 速率下,TX_ER 不起作用。 |

TX_EN | 输出 | 1 | Transmit Enable,发送使能信号,只有在TX_EN 有效(高电平)期内传的数据才有效。 |

GTX_CLK | 输出 | 1 | 发送参考时钟,时钟频率为125MHz 。 需要注意的是GTX_CLK 时钟的方向是从 MAC 侧指向 PHY 侧的,此时钟是由 MAC 提供的 ,这里与 MII 接口有所差别的地方。 |

TXD | 输出 | 8 | TransmitData ,数据发送信号,共 8 根信号线。 |

RX_ER | 输入 | 1 | Receive Error 接收数据错误提示信号; 同步于 RX_CLK高电平有效,表示 RX_ER 有效期内传输的数据无效。对于10Mbps 速率下, RX_ER 不起作用 。 |

RX_DV | 输入 | 1 | Reveive Data Valid 接收数据有效信号;拉高时表示接收数据有效。 |

RXD | 输入 | 8 | ReceiveData ,数据接收信号,共 8 根信号线。 |

RX_CLK | 输入 | 1 | 接收数据参考时钟,时钟频率为 125MHz 。 RX_CLK 是由PHY 侧提供的。 |

CRS | 输入 | 1 | Carrier Sense ,载波侦测信号,不需要同步于参考时钟,只要有数据传输, CRS 就有效 。 需要注意的是 CRS 只有 PHY在半双工模式下有效 。 |

COL | 输入 | 1 | Collision Detectd ,冲突检测信号,不需要同步于参考时钟 。 需要注意的是 CRS 只有 PHY 在半双工模式下有效 |

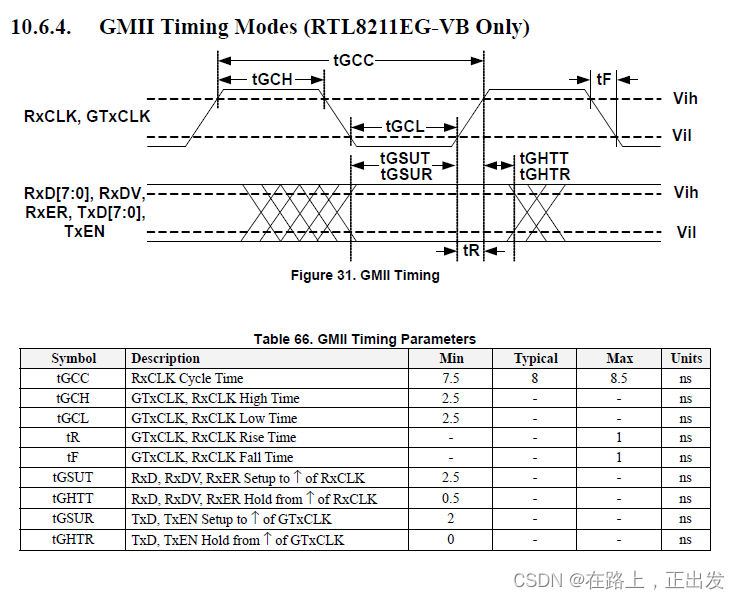

收发时序

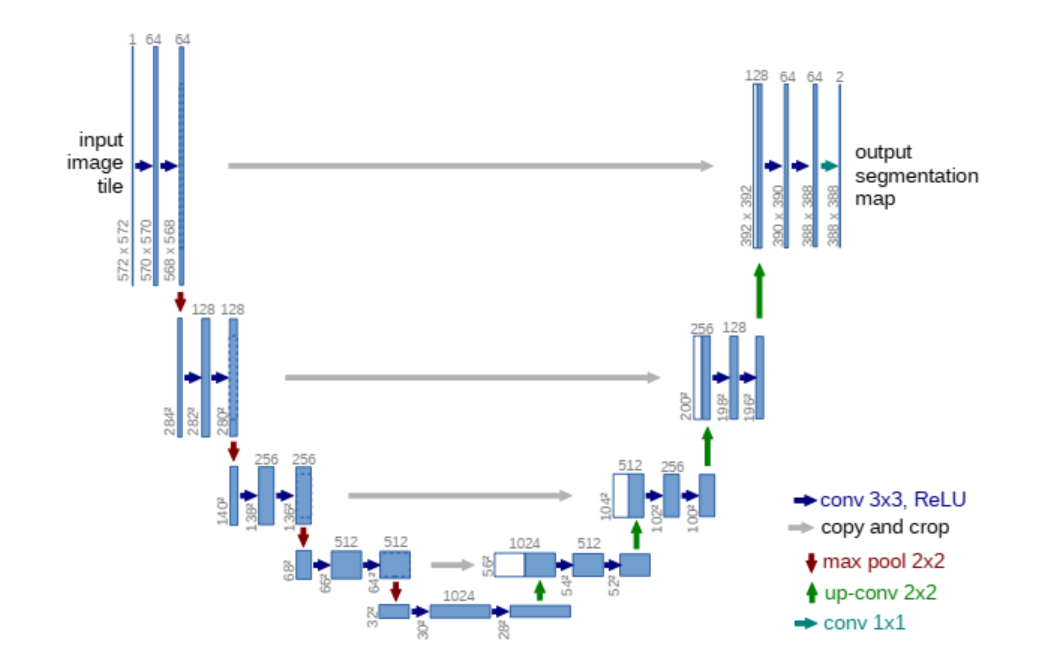

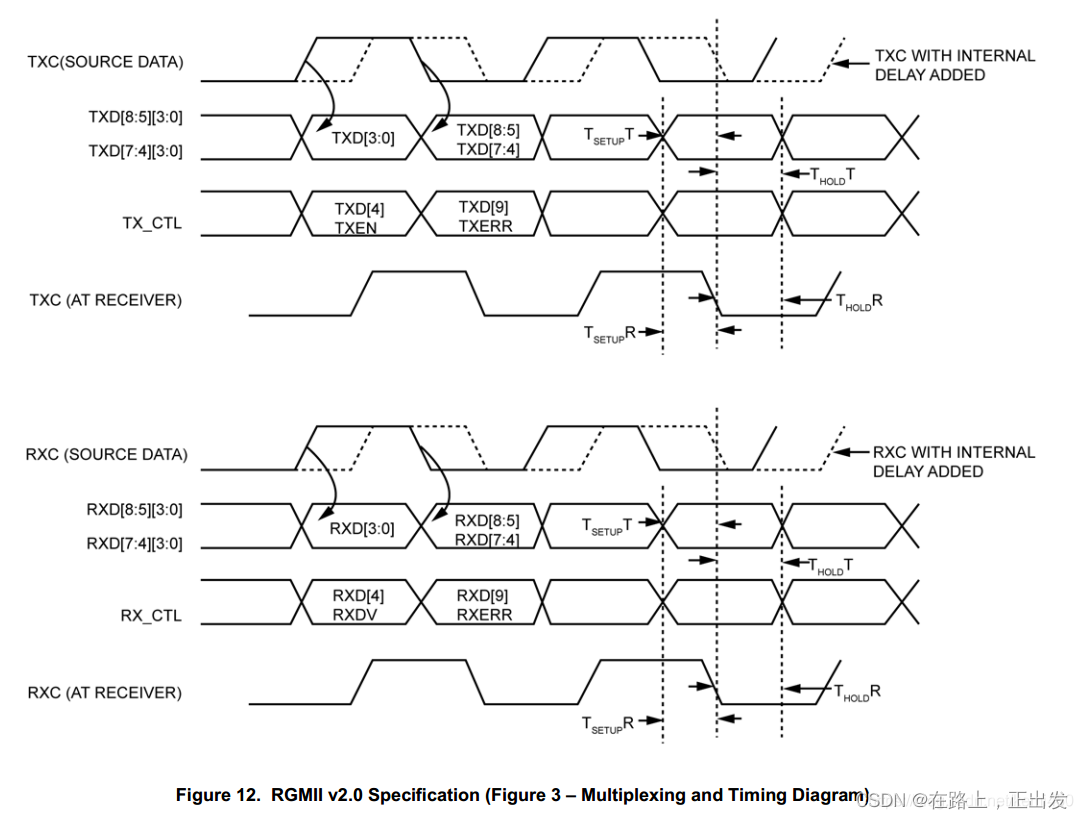

RGMII接口时序介绍

RGMII(Reduced Gigabit Medium Independent Interface)媒体独立接口,主要针对十兆/百兆/千兆以太网通信。GMII 的简化版本,将接口信号线数量从24 根减少到 14 根,时钟频率仍旧为125MHz TX/RX 数据宽度从 8 为变为 4 位。

引脚连接示意图

针脚含义说明

针脚名称 | 输入/输出 (相对MAC侧而言) | 位宽 | 含义 |

TX_ER | 输出 | 1 | 该信号线上传送 GMII 接口中的 TX_EN 和 TX_ER 两种信息,在 TX_CLK 的上升沿发送 TX_EN ,下降沿发送 TX_ER 。 |

TX_CLK | 输出 | 1 | 发送参考时钟,1000Mbps 速率下,时钟频率为时钟频率为125MHz 。 需要注意的是TX_CLK 时钟的方向是从 MAC 侧指向 PHY 侧的,此时钟是由 MAC 提供的 ,这里与 MII 接口有所差别的地方。 |

TXD | 输出 | 4 | 在时钟 TX_CLK 的上升沿发送 GMII 接口中的 TXD[3:0] 在时钟 TX_CLK 的下降沿发送 GMII 接口中的 TXD[7:4] 。 |

RX_DV | 输入 | 1 | 该信号线上传送 GMII 接口中的 RX_DV 和 RX_ER 两种信息,在 RX_CLK 的上升沿 传输 RX_DV ,下降沿 传输RX_ER |

RXD | 输入 | 4 | 时钟RX_CLK 的上升沿 传输 GMII 接口中的 RXD[3:0] 0],在时钟 RX_CLK 的下降沿发送 GMII 接口中的 RXD[7:4] 。 |

RX_CLK | 输入 | 1 | 接收数据参考时钟,时钟频率为 125MHz 。 RX_CLK 是由PHY 侧提供的。 |

CRS | 输入 | 1 | Carrier Sense ,载波侦测信号,不需要同步于参考时钟,只要有数据传输, CRS 就有效 。 需要注意的是 CRS 只有 PHY在半双工模式下有效 。 |

COL | 输入 | 1 | Collision Detectd ,冲突检测信号,不需要同步于参考时钟 。 需要注意的是 CRS 只有 PHY 在半双工模式下有效 |

收发时序

RGMII 接口为了保持1000Mbps 的传输速率不变,RGMII 接口在时钟的上升沿和下降沿都采样数据。在参考时钟的上升沿发送GMII 接口中的TXD[3:0]/RXD[3:0],在参考时钟的下降沿发送GMII 接口中的TXD[7:4]/RXD[7:4]。RGMII 同时也兼容100Mbps 和10Mbps 两种速率,此时参考时钟速率分别为25MHz 和2.5MHz。TX_EN 信号线上传送TX_EN 和TX_ER 两种信息,在TX_CLK 的上升沿,下降沿发送TX_ER;同样的,RX_DV 信号线上也传送RX_DV 和RX_ER 两种信息,在RX_CLK 的上升沿传输RX_DV,下降沿传输RX_ER。

千兆以太网硬件设计参考

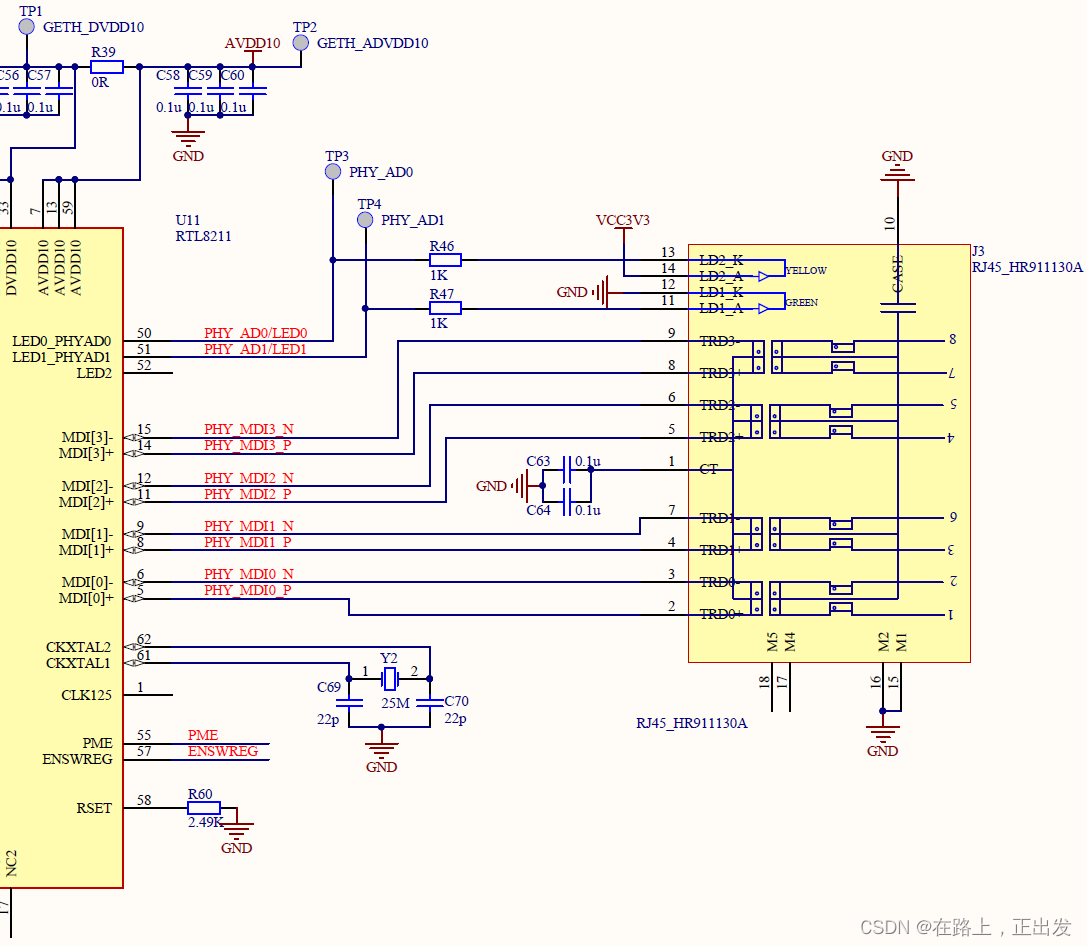

RJ-45

RJ-45的四对差分数据线接PHY芯片RTL8211输出的四队差分数据线。此外PHY输出的LED灯控制信号输出控制RJ-45的黄绿灯状态。

一般来说,黄灯闪烁代表有数据传输,绿灯常亮代表与对端网口互联成功。

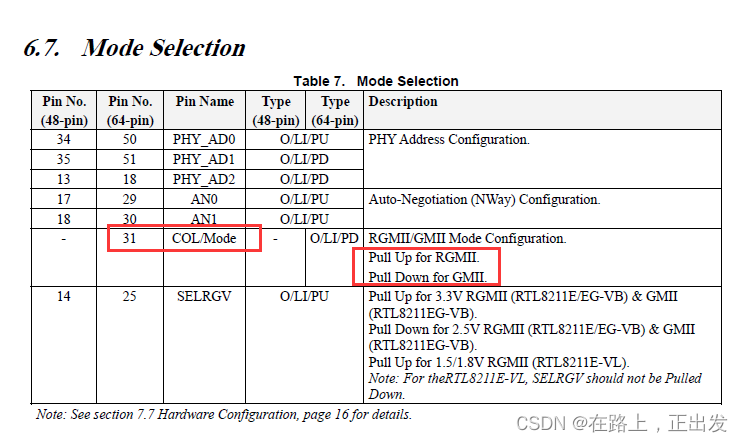

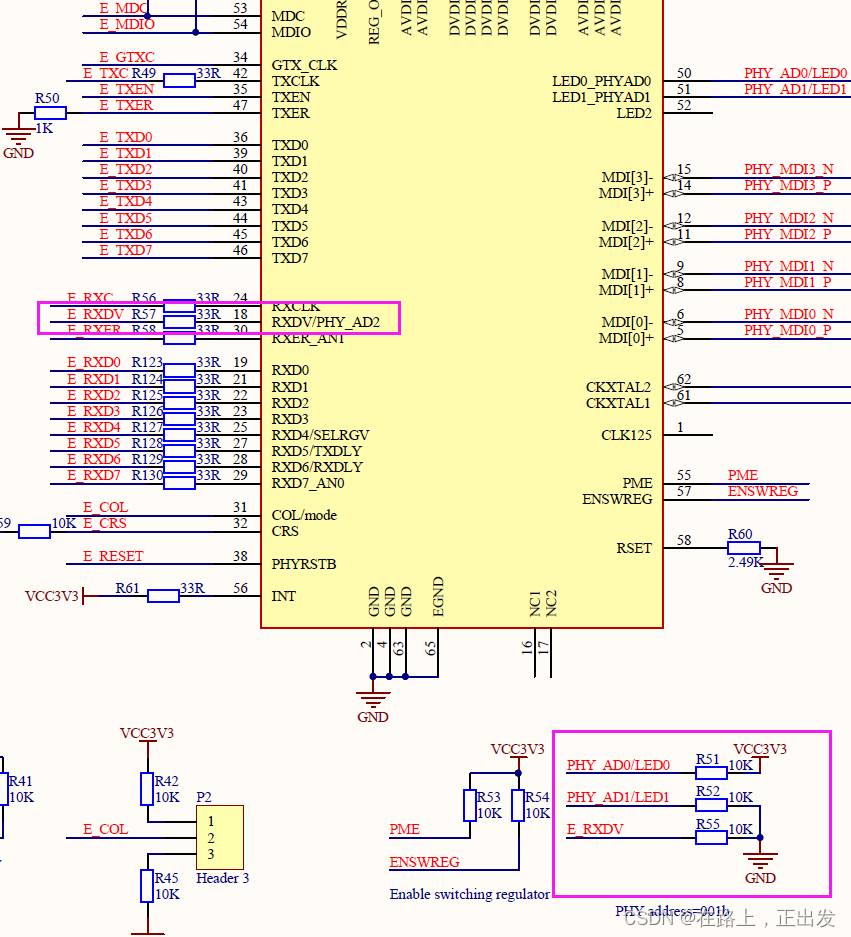

RTL8211

RGMII/GMII模式的切换通过外部跳线帽实现,因为芯片手册声明:

PHY的物理地址:3'b001

参考声明并致谢

【1】正点原子FPGA实战篇之以太网

【2】RTL8211芯片手册

【3】芯路恒开发板资料