目录

if_else语句:

五点说明:

case语句:

真值表:

例:

由于使用条件语句不当在设计中生成了原本没想到有的锁存器:

if_else语句:

if语句是用来判定所给定的条件是否满足,根据判定的结果(真或假)决定执行给出的两种操作之一。 Verilog HDL语言提供了三种形式的if语句。

(1).if(表达式)语句

例如:

if ( a > b ) out1 <= int1;

(2).if(表达式) 语句1

else 语句2

例如:

if(a>b) out1<=int1;

else out1<=int2;

(3).if(表达式1) 语句1;

else if(表达式2) 语句2;

else if(表达式3) 语句3;

........

else if(表达式m) 语句m;

else 语句n;

例如:

if(a>b) out1<=int1;

else if(a==b) out1<=int2;

else out1<=int3;

五点说明:

(1).三种形式的if语句中在if后面都有“表达式”,一般为逻辑表达式或关系表达式。系统对表达式的值进行判断,若为0,x,z,按“假”处理,若为1,按“真”处理,执行指定的语句。

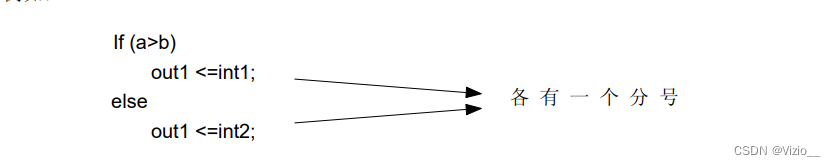

(2) .第二、第三种形式的if语句中,在每个else前面有一分号,整个语句结束处有一分号。

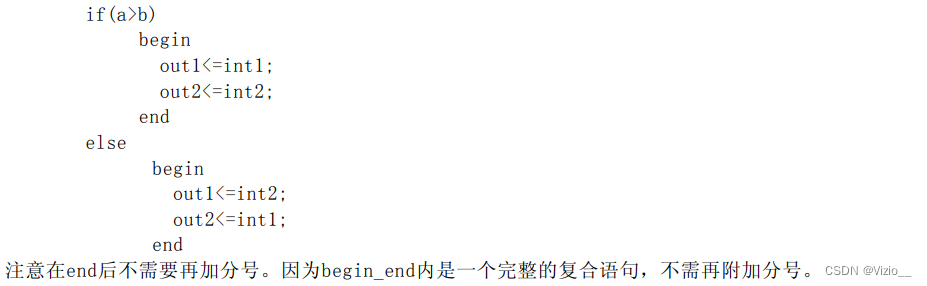

(3).在if和else后面可以包含一个内嵌的操作语句(如上例),也可以有多个操作语句,此时 用begin和end这两个关键词将几个语句包含起来成为一个复合块语句

(4).允许一定形式的表达式简写方式。

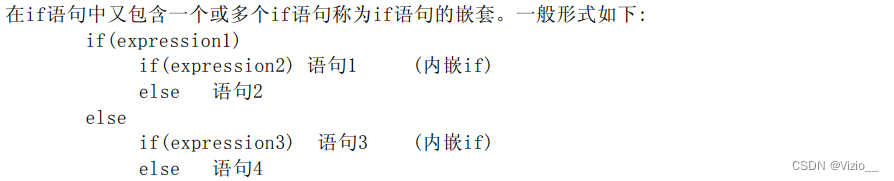

(5).if语句的嵌套

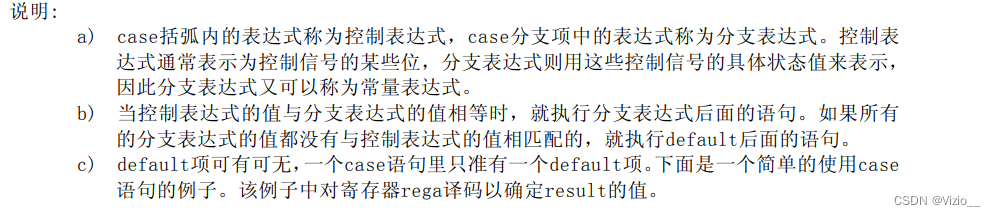

case语句:

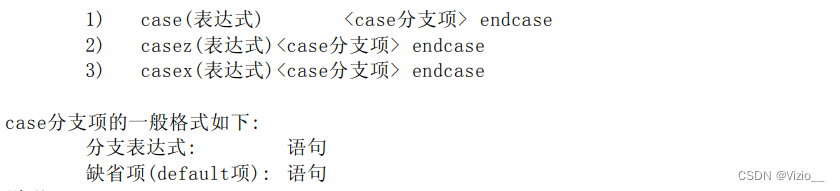

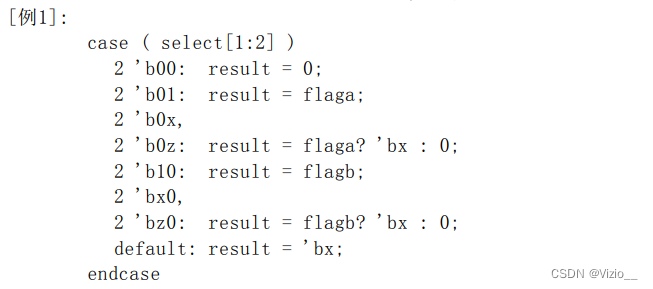

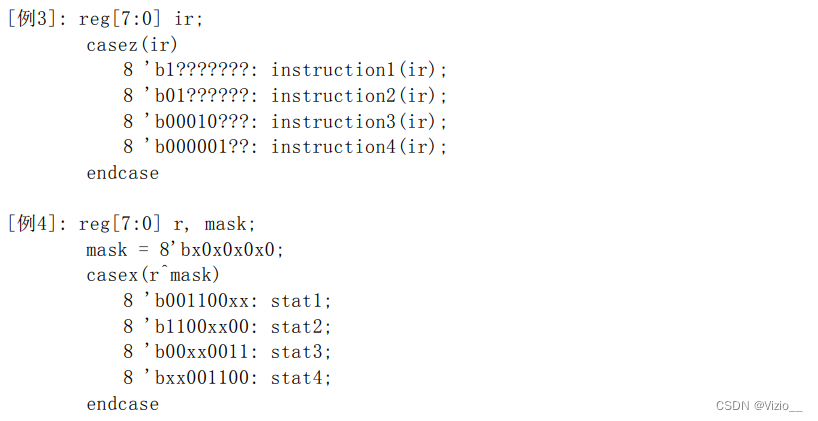

case语句是一种多分支选择语句,if语句只有两个分支可供选择,而实际问题中常常需要用到多分支 选择,Verilog语言提供的case语句直接处理多分支选择。case语句通常用于微处理器的指令译码, 它的一般形式如下:

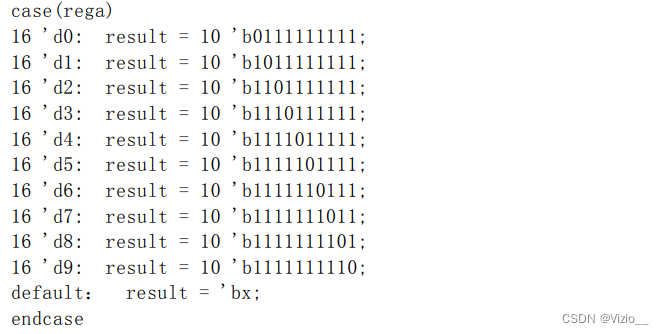

真值表:

例:

例:

由于使用条件语句不当在设计中生成了原本没想到有的锁存器:

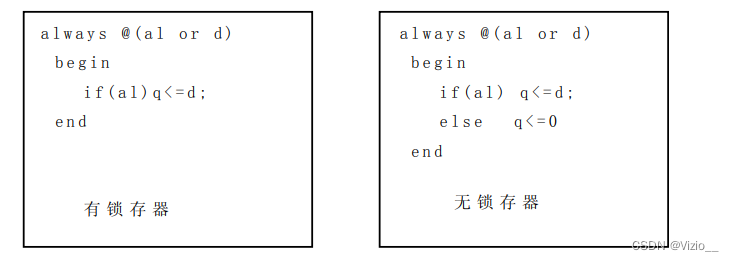

由于使用条件语句不当在设计中生成了原本没想到有的锁存器:

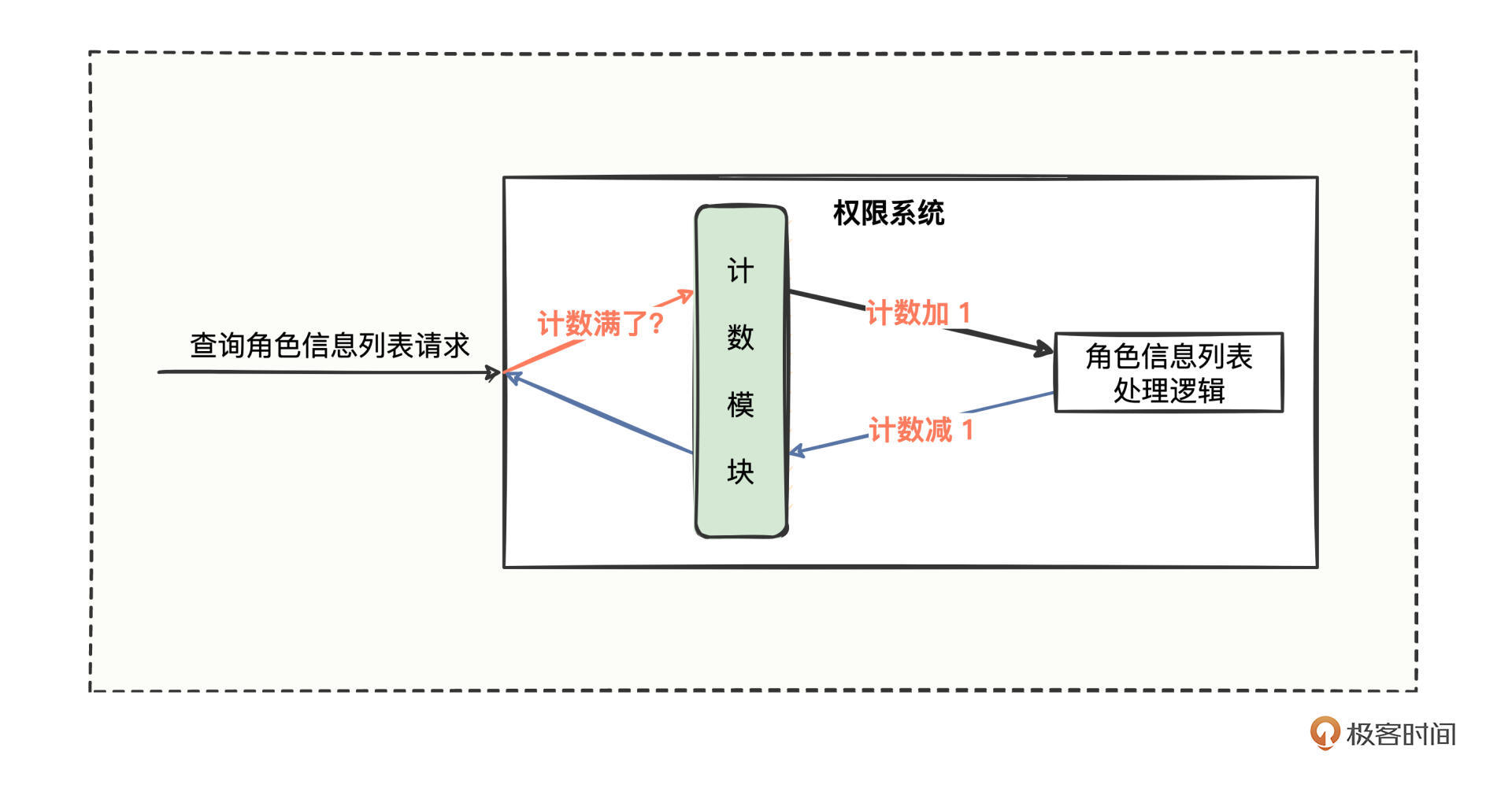

检查一下左边的"always"块,if语句保证了只有当al=1时,q才取d的值。这段程序没有写出 al = 0 时的结果, 那么当al=0时会怎么样呢?

在"always"块内,如果在给定的条件下变量没有赋值,这个变量将保持原值,也就是说会生成一个锁 存器!

如果设计人员希望当 al = 0 时q的值为0,else项就必不可少了,请注意看右边的"always"块,整 个Verilog程序模块综合出来后,"always"块对应的部分不会生成锁存器。

另一种偶然生成锁存器是在使用case语句时缺少default项的情况下发生的

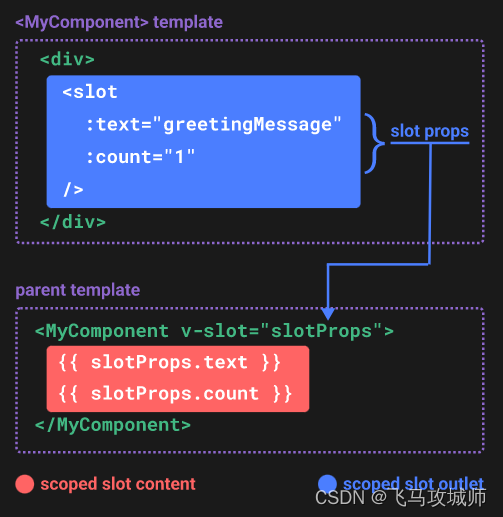

case语句的功能是:在某个信号(本例中的sel)取不同的值时,给另一个信号(本例中的q)赋不同的 值。注意看下图左边的例子,如果sel=0,q取a值,而sel=11,q取b的值。这个例子中不清楚的是:如 果sel取00和11以外的值时q将被赋予什么值?在下面左边的这个例子中,程序是用Verilog HDL写的, 即默认为q保持原值,这就会自动生成锁存器。

右边的例子很明确,程序中的case语句有default项,指明了如果sel不取00或11时,编译器或仿真 器应赋给q的值。程序所示情况下,q赋为0,因此不需要锁存器。

以上就是怎样来避免偶然生成锁存器的错误。如果用到if语句,最好写上else项。如果用case语句, 最好写上default项。遵循上面两条原则,就可以避免发生这种错误,使设计者更加明确设计目标, 同时也增强了Verilog程序的可读性。