高层次综合 (HLS) 是自动设计进程, 利用数字系统的抽的象行为规范来生成寄存器传输级结构, 以实现给定行为。

使用 HLS 的典型流程包含下列步骤:

1. 围绕给定架构在高抽象层次使用 C/C++ 编写算法

2. 在行为级别验证功能

3. 使用 HLS 工具为给定时钟速度和输入约束生成 RTL

4. 验证生成的 RTL 的功能

5. 使用相同输入源代码探索其他不同的架构HLS 能够为创建高质量 RTL 铺路, 但并不能快速手动编写没有任何错误的 RTL。

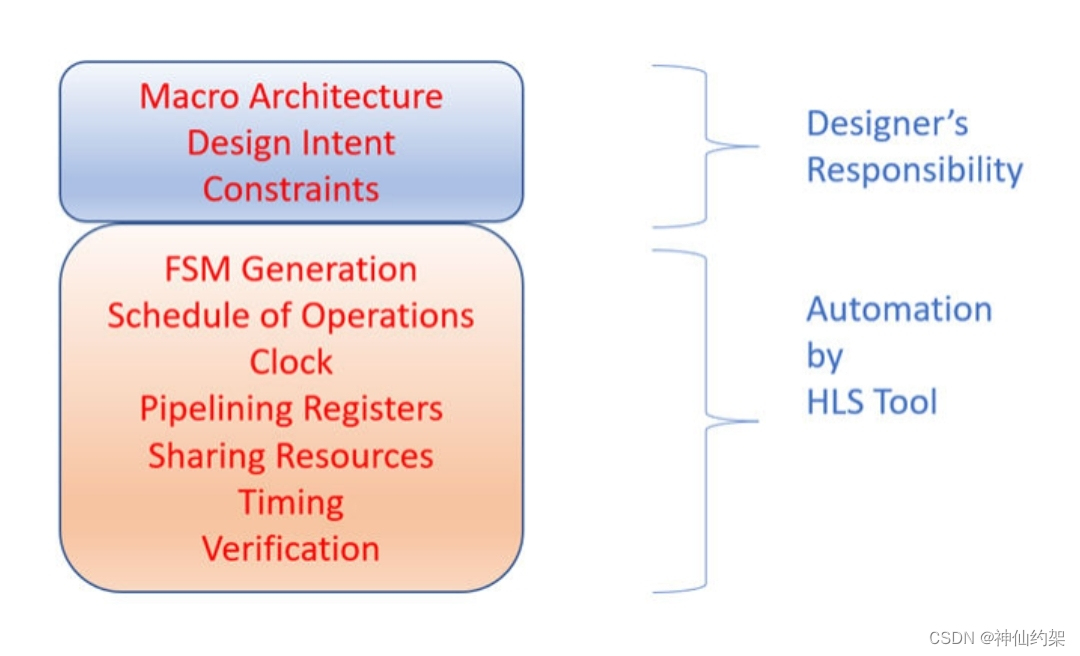

设计师需要以 C/C++ 创建高层次的算法宏架构, 这意味着必须审慎全面考量设计意图以及设计与外界世界的交互方式。 HLS 工具还需要时钟周期、性能约束等输入约束。

在高层次上并不需要制定微架构决策, 如创建状态机、数据路径、寄存器流水线等。这些细节可以留给 HLS 工具, 通过提供输入约束(如时钟速度、性能编译指示、目标器件等) 即可生成经过最优化的 RTL。

提升效率

设计师利用 HLS 开展高抽象层工作, 这表示需编写为 HLS 输入的代码行数更少。由于缩短了用于编写 C++ 代码的时间并且周转更快, 因此错误更少, 从而提升了整体设计效率。设计师们能将更多时间集中在创建更高层次的高效设计上, 而无需担忧机械性的 RTL 实现任务。

HLS 不仅能提升设计效率, 也能提升验证效率。借助 HLS 也能在高层次生成或创建测试激励文件, 这意味着原始设计意图可以快速得到验证。由于流程仍在 C/C++ 领域内, 因此设计师可以尝试快速调整已验证的算法。在 C/C++ 内完成算法验证后, HLS 工具即可将同样的测试激励文件用于生成 RTL。然而, 生成的 RTL 可与现有 RTL 验证流程加以集成, 从而实现更全面的验证覆盖范围。

使用 HLS 给设计和验证带来的好处总结如下:

• 在 C 语言层次开发和确认算法, 以便根据硬件实现详细信息在抽象层进行设计。

• 使用 C 语言仿真来确认设计并以比传统 RTL 设计更快的速度进行迭代。

• 根据 C 语言源代码和编译指示创建多个设计解决方案, 以探索设计空间并找到最优解。

支持复用

为高层次综合创建的设计属于通用设计, 无关实现。不同于给定 RTL, 这些源代码并不与任何技术节点或任何给定时钟周期绑定。只需少量更新输入约束, 无需更改任何源代码, 即可尝试多种不同的架构。对 RTL 采用类似的做法却并不实用。设计师为给定时钟周期创建 RTL, 无论对衍生产品进行任何程度的更改, 都会导致产生新的复杂工程。设计师利用 HLS 开展高层次工作时, 就无需担心微架构, 并且可以依靠 HLS 工具来自动重新生成新的 RTL。