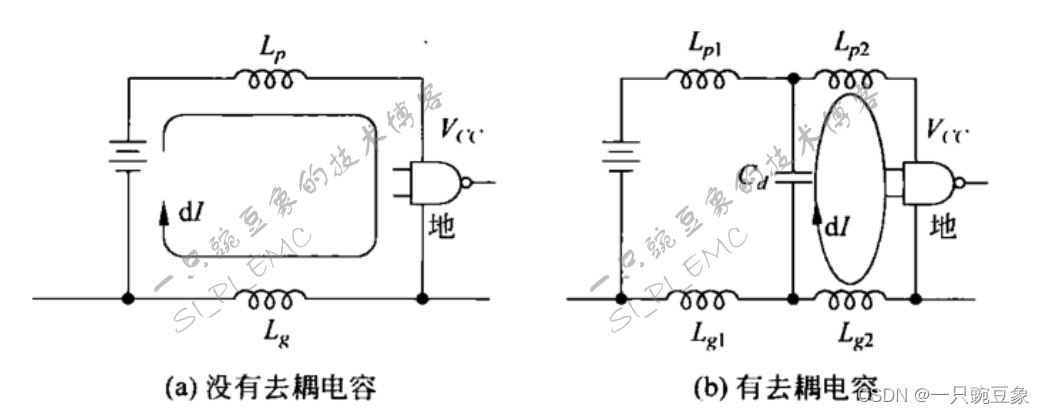

大多数资料都会提到电容摆放要尽可能靠近芯片,这是从小回路电感的角度来看待这个摆放问题,如下图所示,当逻辑芯片发生信号电平的转换时,配电网络中出现瞬态电流增量dI,这个瞬态电流会流过电源和接地电感从而产生一个噪声电压,一个大的电感环路就会成为一个大的等效环形天线:

因此,去耦电容具有两个作用:

1. 提供一个邻近IC的电荷源,当IC发生切换时,其可以通过一个低阻抗通路提供所需的瞬态电流;

2. 在电源和接地之间提供一个低交流阻抗,从而有效地短路由IC 回注入电源/接地系统的噪声。

但是,大型BGA的芯片设计,导致PCB的电容布局空间有限,如何才是有效的靠近芯片放置电容的位置呢?

理解电容的去耦半径最好的办法→考察噪声源和电容补偿电流之间的相位关系:

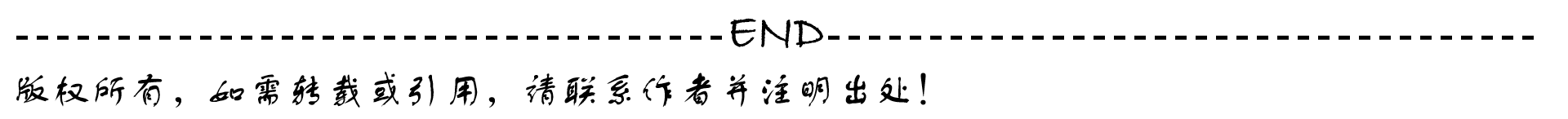

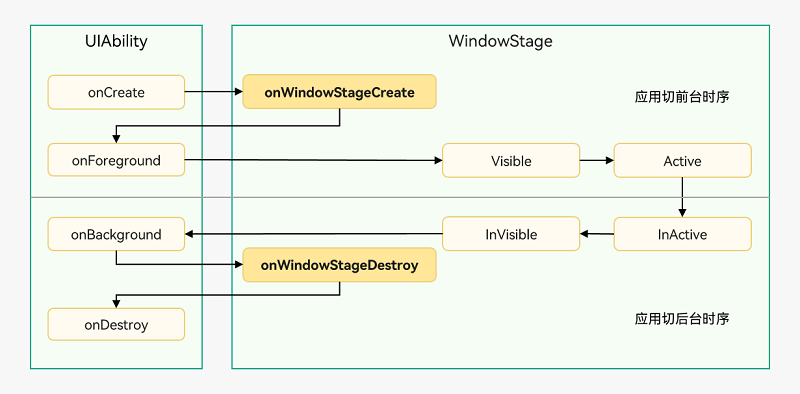

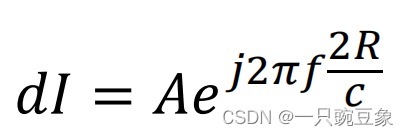

当芯片产生瞬态电流增量dI 时,会在电源网络的局部区域产生电压扰动,电容要对其进行补偿,就必须先感知到这个电压扰动,而信号在介质中传播存在延时,因此从发生局部电压扰动到电容感知到扰动之间会有一个时间延迟,同样,电容的补偿电流达到扰动区也需要一个延迟,因此必然造成噪声源和电容补偿电流之间的相位上的不一致。 在谐振点f 附近,电容对噪声补偿效果最好,因此,补偿电流可表示为:

其中,A是总的动态工作电流幅度,R是扰动区域到电容的距离,c是信号传播速度。 当扰动区到电容的距离达到λ/4时,补偿电流和噪声源相位刚好相差180度,即完全反相,此时补偿电流不再起作用,去耦作用失效,所以,距离越近,相位差越小,补偿能传递越多,实际应用中最好控制在λ/40 ~ λ/50,这是一个实验数据。

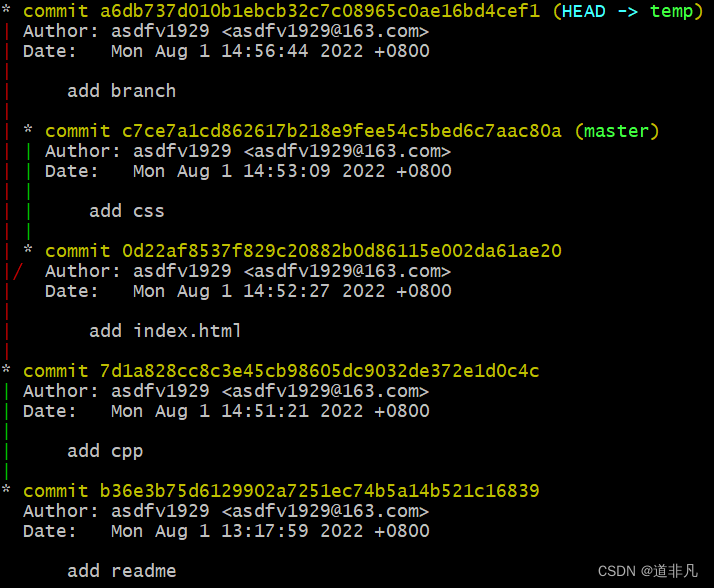

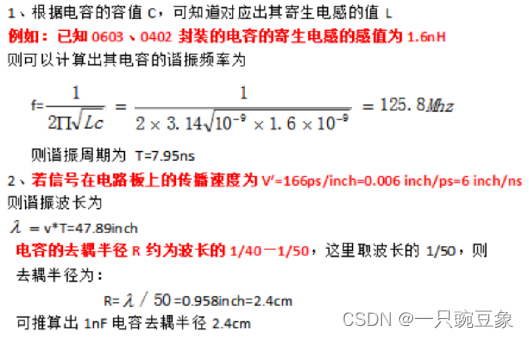

举例说明耦合半径的计算:

综上所述,对于电容的摆放,关键就是与负载之间的安装距离,容值最小的电容,有最高的谐振频率,去耦半径最小,因此放在最靠近芯片的位置,而大容值的电容,因为其谐振频率很低,对应的波长非常长,因此去耦半径也就很大,这也就是为什么工程设计中不太关注大电容在电路板上位置的原因。