目录

为什么要创建时序约束文件?

时序:

创建时序约束文件:

为什么要创建时序约束文件?

对于一些简单的工程时序的要求并不是特别的严格,添不添加时序约束文件影响不大。但是对于一些复杂的工程,涉及到高频时钟,多个时钟信号,跨多个时钟域等等时序比较混乱的工程添加时 序约束文件就很有必要了,不添加时序约束极有可能会导致功能不正常或者时而正常时而不正常。

时序:

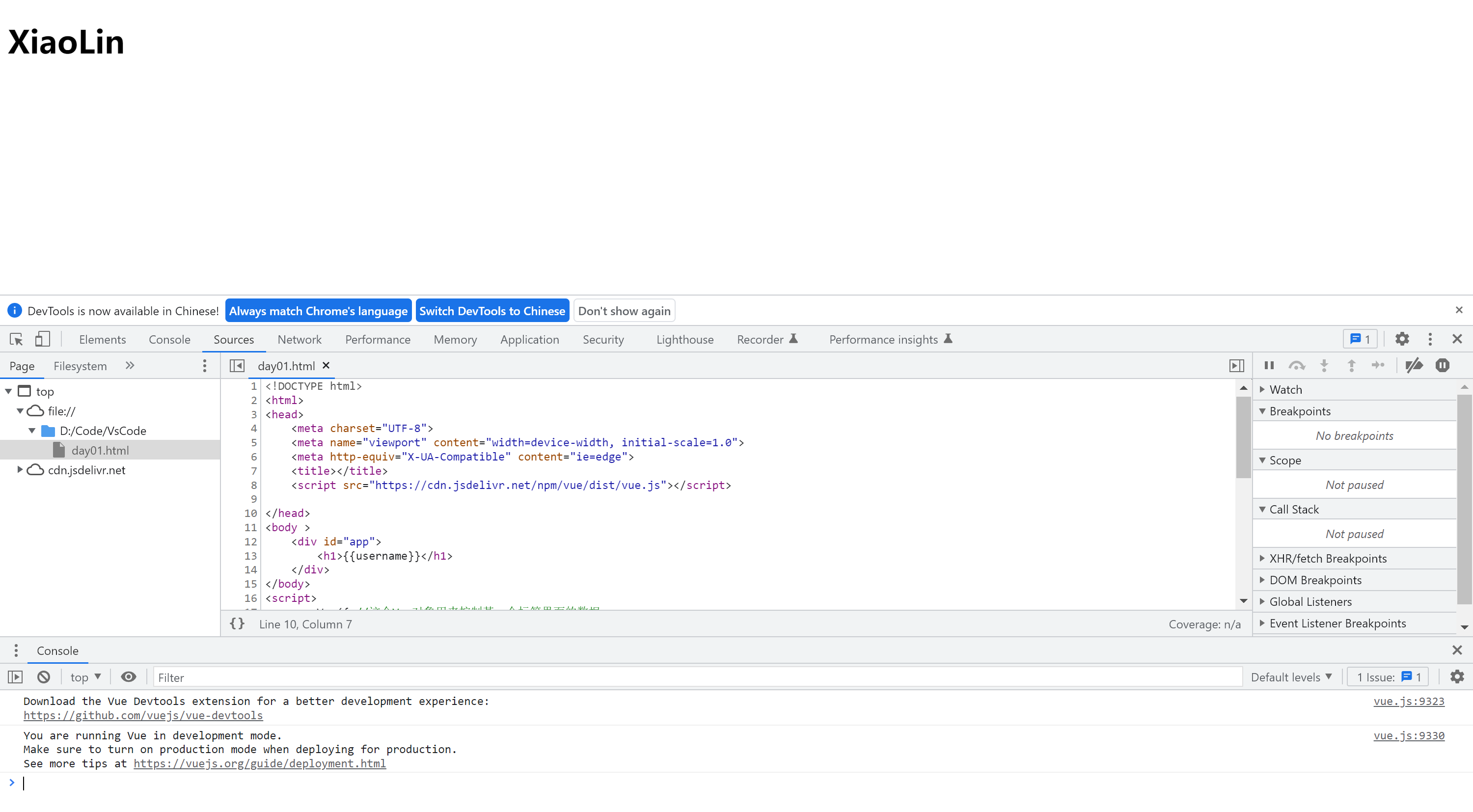

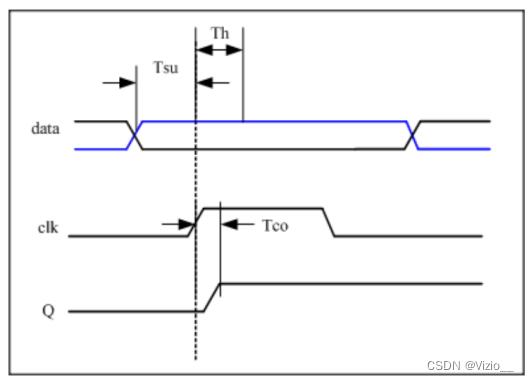

简单的讲就是时钟与数据的关系,这里我们要引入“建立时间”和“保持时间”这 两个概念,大家要明白,FPGA 内部是有大量的触发器的,而“建立时间”和“保持时间”就是针对触发器来讲的。要想完成一次数据的正确采样,那么就必须满足“建立时间”和“保持时间”的要求,那么什么 是“建立时间”和“保持时间”呢,我们先看下图:

上图中的 Tsu 就是建立时间,它是指在触发器的时钟信号上升沿到来以前,数据稳定不变的时间,如 果建立时间不够,数据将不能在这个时钟上升沿被稳定的打入触发器,Tsu 就是指这个最小的稳定时间。而 保持时间是指在触发器的时钟信号上升沿到来以后,数据稳定不变的时间,如果保持时间不够,数据同样不能被稳定的打入触发器,Th 就是指这个最小的保持时间。

因此我们在开发工程时一定要注意这两个时间,切忌在数据亚稳态时对数据进行采样,那么采样的数 据就不准确。当然时序约束不仅仅如此,还需要考虑各个触发器的延时时间,例如数据需要从寄存器 1 传 向寄存器 2,那么假设在寄存器 1 进行触发时数据被准确采样,当数据从寄存器 1 出来是需要一定延时的, 延时完成后我们再经过组合逻辑处理又会进一步延时,再之后到达寄存器 2 进行采样,这个时候我们就需 要考虑寄存器 2 时钟的上升沿到来前我们的数据是否已经保持稳定并且能够满足建立时间,如果不满足那 么寄存器 2 极有可能是在数据处于亚稳态的时候对数据进行了采样那么数据是不准确。

创建时序约束文件:

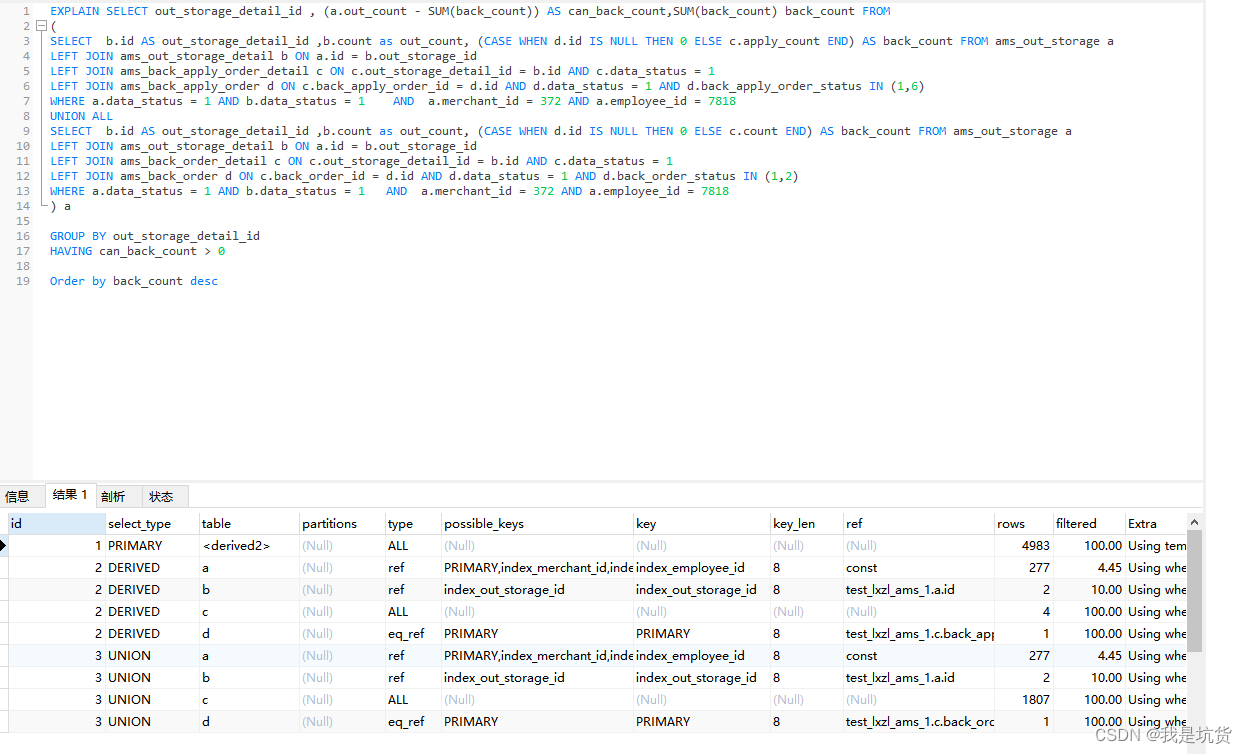

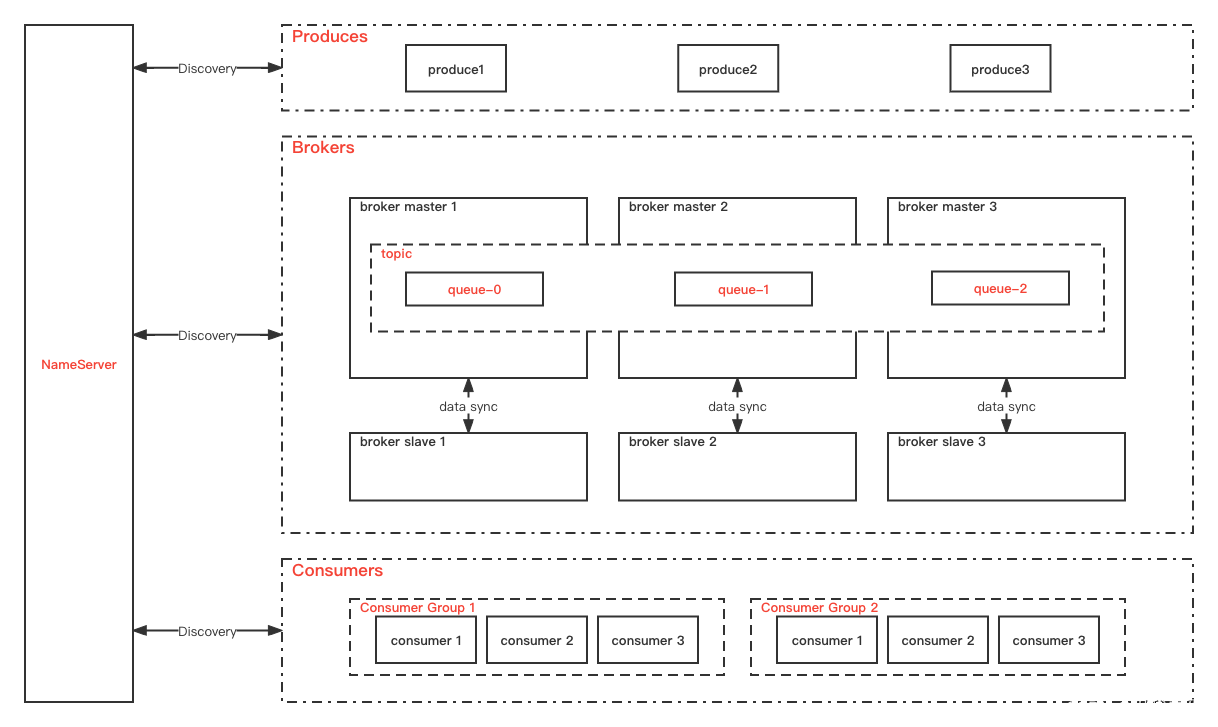

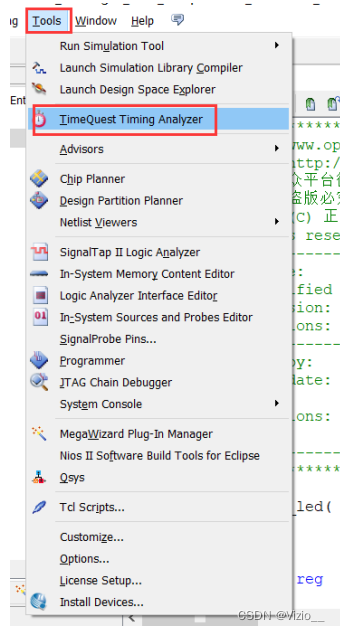

点击 Tools 选中 TimeQuest Timing Analyer 如下图所示:

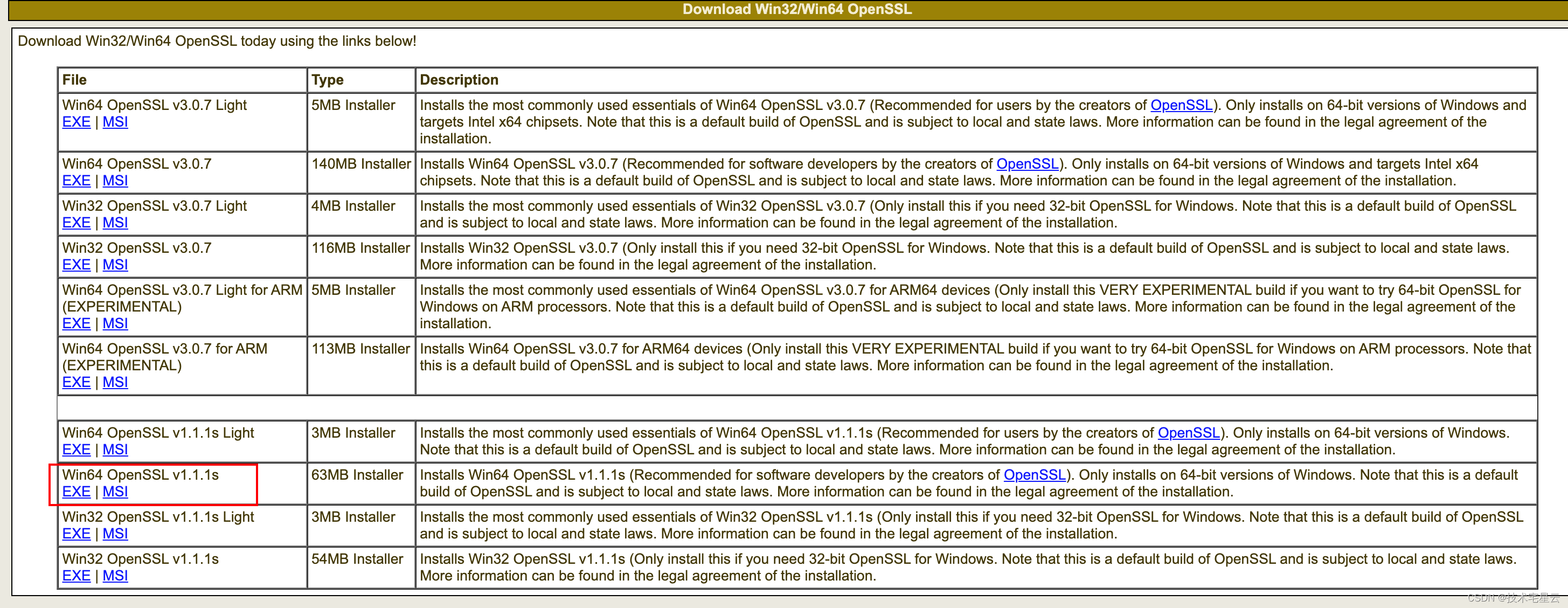

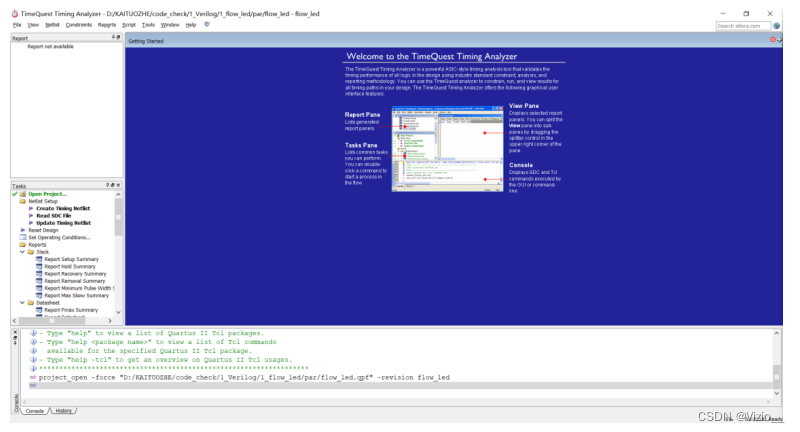

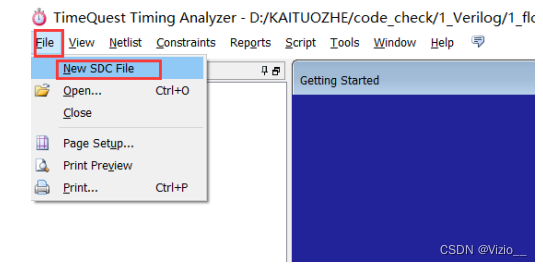

然后我们创建一个文件格式为.SDC 的约束文件,步骤如下图所示:

然后我们创建一个文件格式为.SDC 的约束文件,步骤如下图所示:

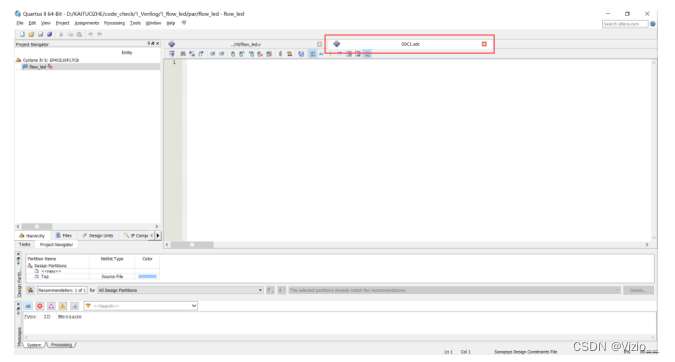

创建好 SDC 文件后我们回到工程,可以看到工程里已经出现一个空白的 SDC 文件,如下图所示:

接下来我们就可以在这个空白约束文件中编写约束语句了

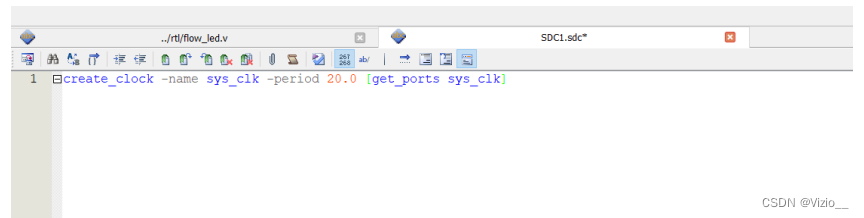

我们在空白的 SDC 文件中输入:create_clock -name sys_clk -period 20.0 [get_ports sys_clk]。这条语句就 是创建一个时钟( create_clock),这个时钟的名字是 sys_clk(-name sys_clk,注意这里的名字是可以随意 起的,但是建议大家命名的时候可以一眼看出其含义),这个时钟的周期是 20ns(-period 20.0,这里大家 要注意如果没有约束占空比,那么默认 50%的占空比),映射到工程的 sys_clk 端口上(get_ports sys_clk, 这里映射的端口就是工程的实际端口了,这里代表输入的系统时钟)。这样我们就把输入时钟约束好了, 他就是一个严格的 50Mhz 标准时钟。