前情提要

计分板算法可看我写的博文计算机体系结构----计分板(scoreboard)算法

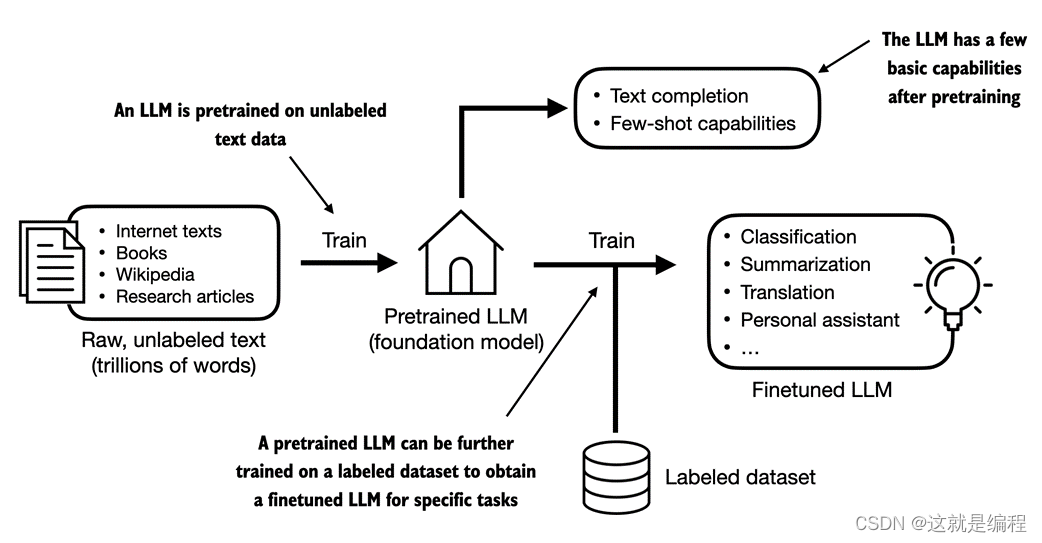

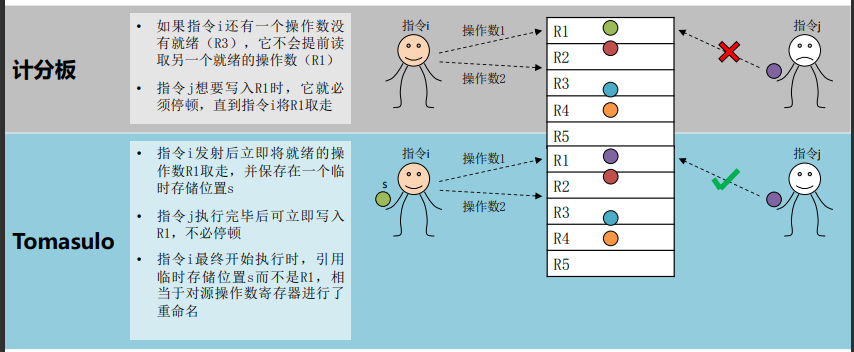

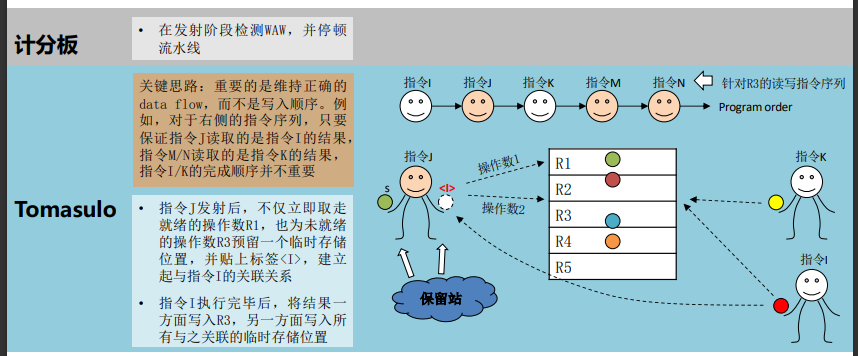

Tomasulo算法的核心是寄存器重命名(register renaming);通过寄存器重命名,可彻底消除WAR/WAW冲突,计分板算法中,WAR/WAW都是通过停顿解决的,当然计分板算法虽然没那么厉害但还是通过动态调度消除了RAW冲突的。

Tomasulo算法如何实现乱序执行

- 需要在值的生产者和消费者之间建立通信,这里消费者指的是当前这条指令,生产者指的是在与这条指令相关的指令。

- 寄存器重命名:给每个值一个tag

- 需要给指令提供缓冲区,这个缓冲区称为保留站

- 指令需要持续监测值是否可用,当这个值准备好了,就广播自己的tag,消费者匹配tag,如

果是自己用的,就知道这个值已经准备好了 - 当全部的值都准备好,需要分发指令到对应的功能单元上去,即当需要的全部值都准备好,分发指令,出保留站

Tomasulo算法的核心要素

- 保留站 Reservation stations (scheduling window),缓存指令以及指令的操作数

- 公共数据总线 Common data bus (CDB),广播结果给保留站(RS)

- 寄存器重命名:消除WAR/WAW相关

- 转发/前递:Forwarding,消除RAW相关(注:我们看下面的例子会发现在RAW相关的前一条指令处于write result阶段时,后一条指令就可以进入EXE阶段了)

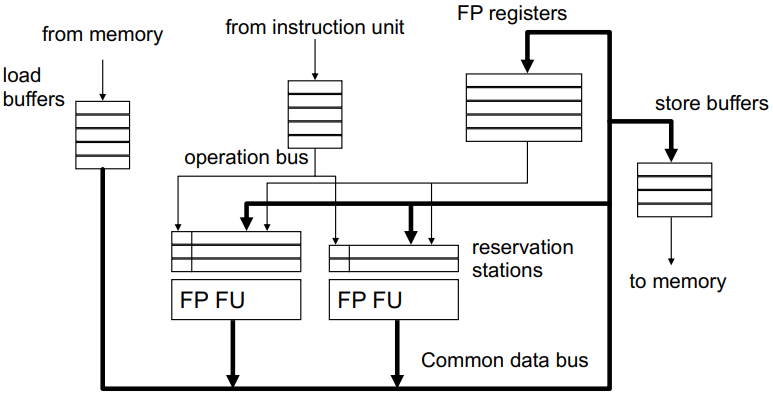

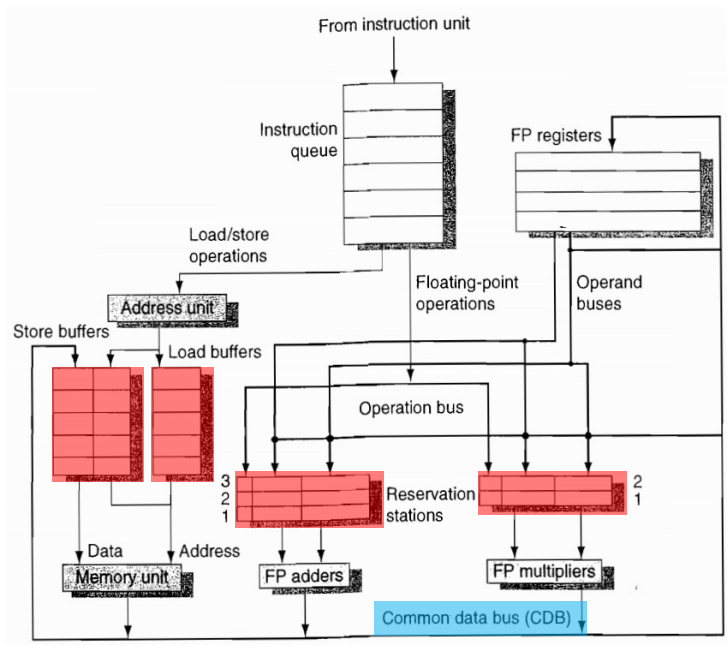

典型的Tomasulo系统:IBM 360/91

Tomasulo算法的各个功能区

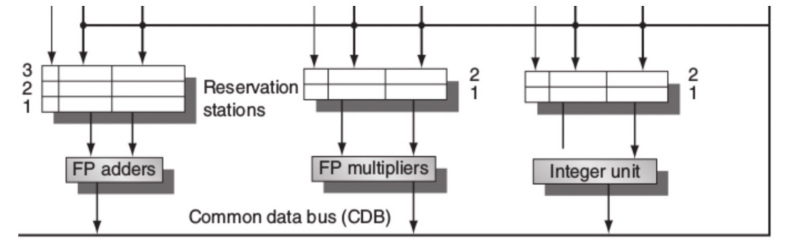

保留站(发射队列)

- 指令顺序发射到保留站

- 缓存指令及操作数

- 如果操作数未就绪,保留站监听数据总线

- 如果操作数已就绪,缓存到保留站

- 每个功能部件有独立的保留站(计分板算法里面所有的功能部件共用一个计分板),如果保留站已全部占用,无法发射指令,只能等。

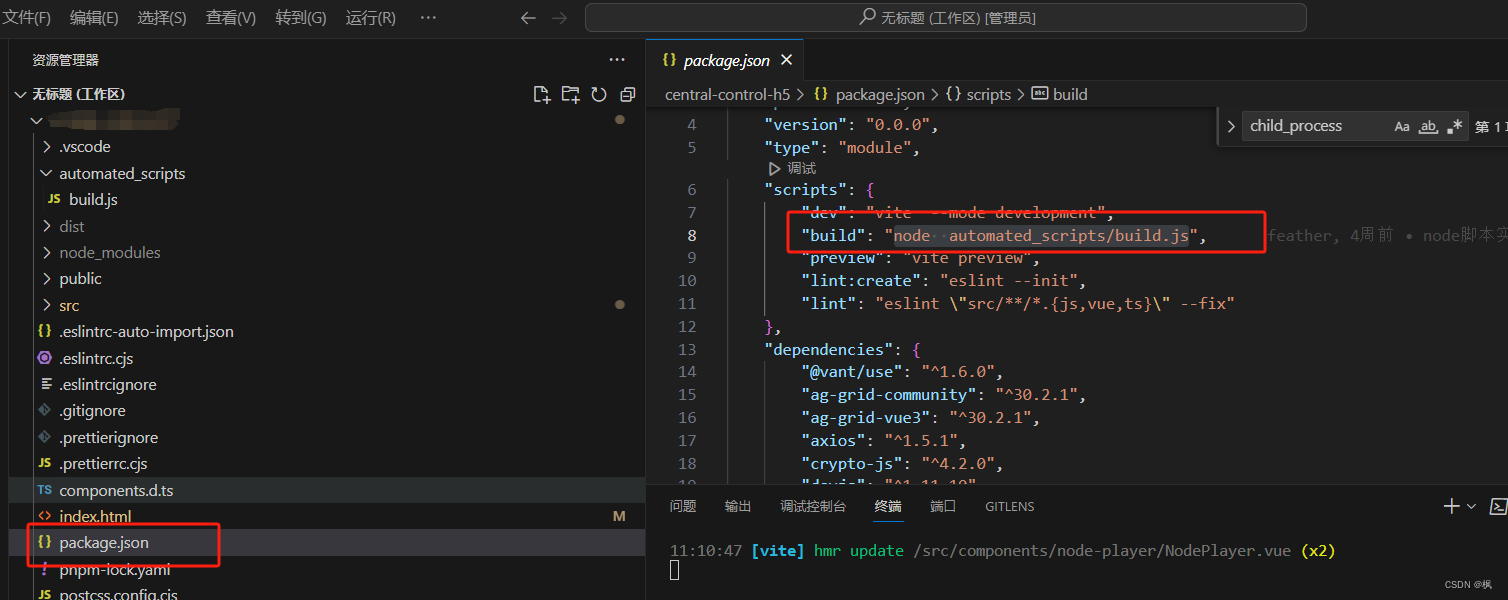

保留站示意图如下。

保留站结构

- Busy字段:表明对应功能部件的保留站已被占用

- Op字段:表明具体的操作,如ADD

- Vj、Vk字段:保留源操作数的值

- Qj、Qk字段

- Qj:产生源操作数Vj的保留站编号,或者0

- Qk:产生源操作数Vk的保留站编号,或者0

- 0表示源操作数已在Vj或Vk

- A字段:为load与store指令存放存储器地址计算信息

上述字段的含义和计分板很相似。

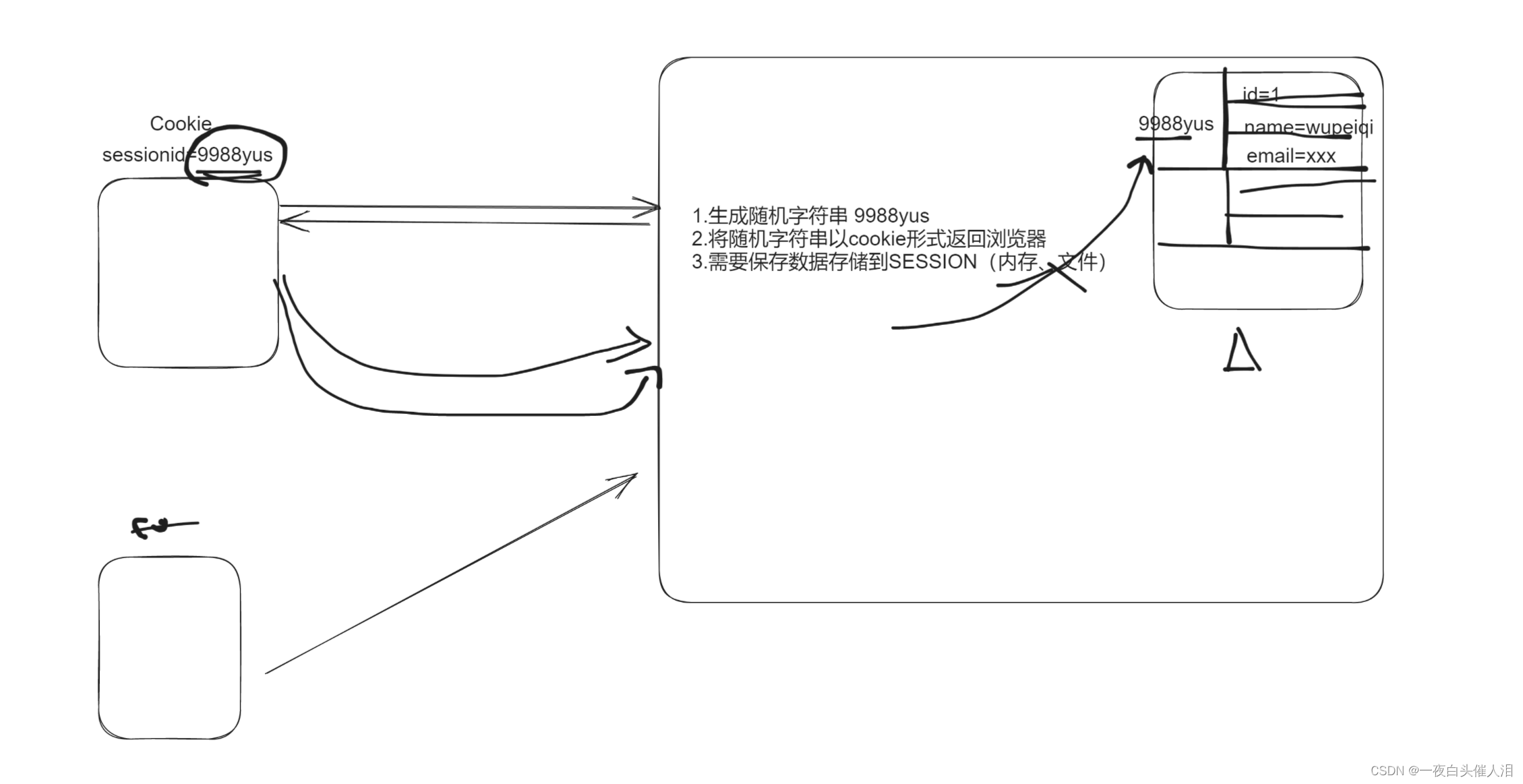

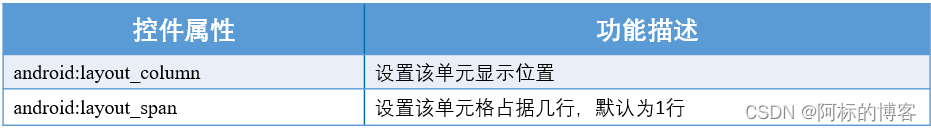

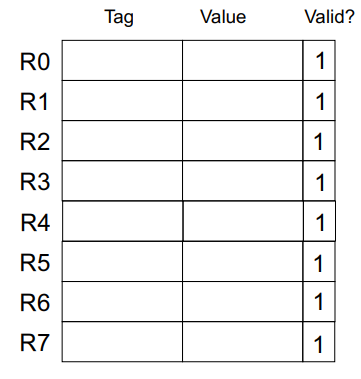

重命名映射表Register Alias Table (RAT)

如果设置了“有效位”,则表中的“值”正确。 否则,Tag 指定在何处查找正确的值。 Tag 是要生成的 Value 的唯一名称、

公共数据总线

Common Data Bus (CDB):广播已完成 insns 的<RS#, value> 。

Tomasulo算法 – 处理WAR

Tomasulo算法 – 处理WAW

Tomasulo算法 – 基本结构

- 每个功能部件有自己的保留站,Load/store buffers和保留站结构基本相同

- 保留站中的每一行保存着一条发射到相应功能部件的指令,并缓存了已就绪的操作数,和未就绪操作数的标签(即生 产指令所在的保留站行号)

- CDB不仅把结果送到寄存器中,也送到所有正在等待该结果的保留站中

- 每个结果会附带一个标签(即生产指令所在的保留站行号),用来和保留站中的标签相匹配

- CDB相当于实现了前送功能

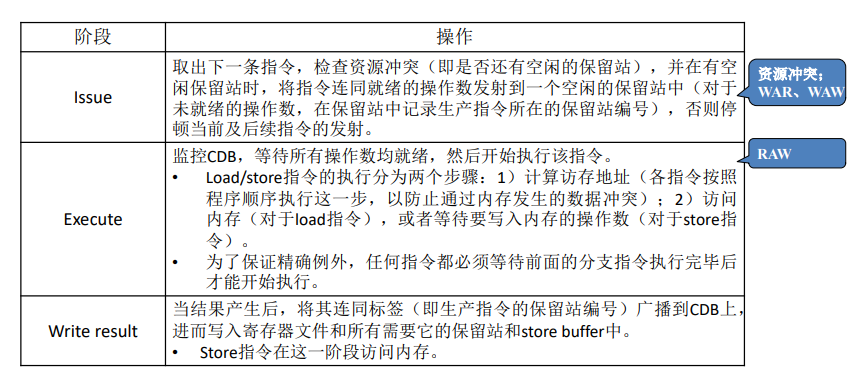

Tomasulo算法 – 三个阶段

每条指令的执行经历三个阶段

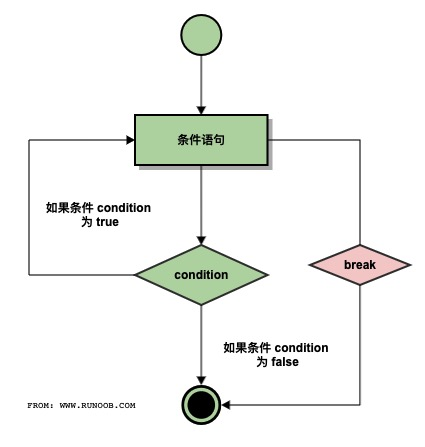

Tomasulo算法 – 算法流程

- 如果在重命名之前保留站可用

- 指令 + 重命名的操作数(源值/标签)插入到保留站中

- 仅当保留站可用时重命名

- 否则停顿

- 在保留站时,每条指令:

- 监视公共数据总线 (CDB) 的源标签

- 当看到标签时,获取源的值并将其保存在保留站中

- 当两个操作数都可用时, 指令准备分派

- 指令准备就绪时向功能单元发送指令

- 指令在功能单元中完成后

- CDB 仲裁

- 将标记值放入 CDB 上(标记广播)

- 寄存器文件已连接到 CDB

– 寄存器包含一个标签,指示寄存器的最新写入者

– 如果寄存器文件中的标签与广播标签匹配, 将广播值写入寄存器(并设置有效位) - 回收重命名标签

– 系统中没有标签的有效副本

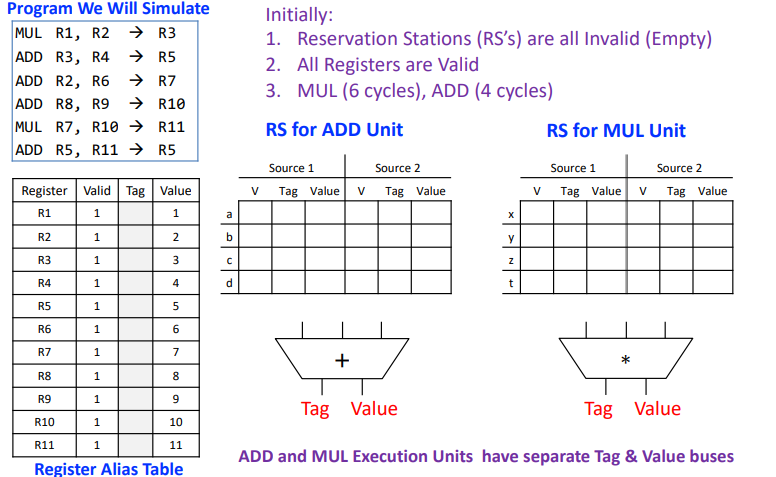

Tomasulo算法示例

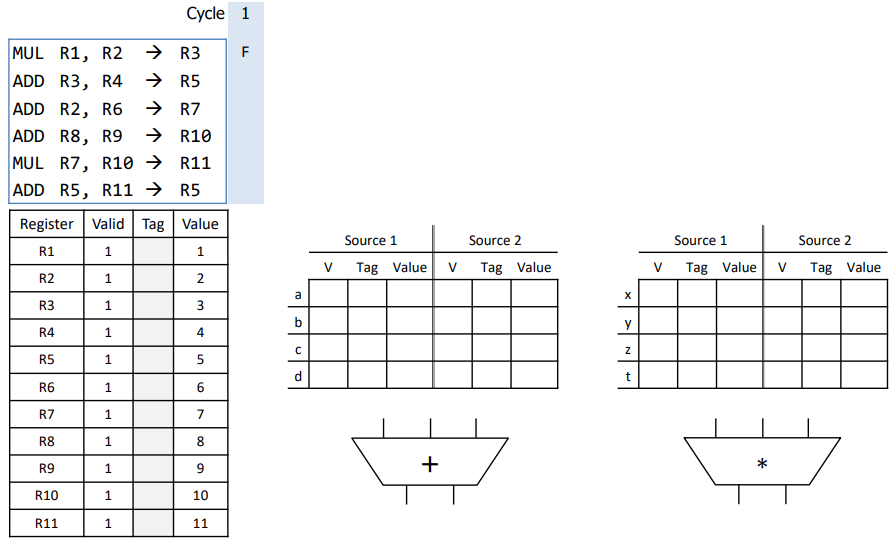

初始化

注意下面的示例中,W和E阶段是同时发生的,因为Tomasulo算法采用了forwarding技术,其他细节不用过多说明,图中均 详细介绍了,自己推导一边这个过程即可熟练掌握。。

Cycle1

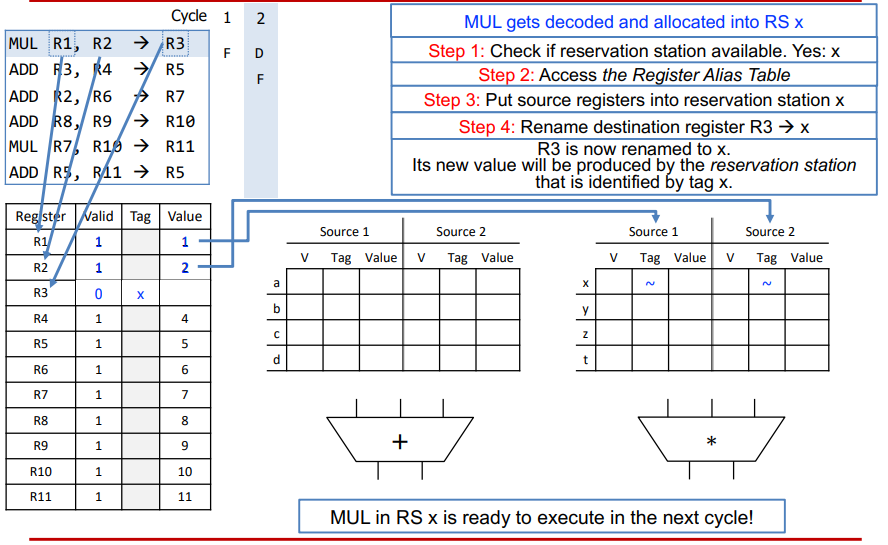

Cycle2

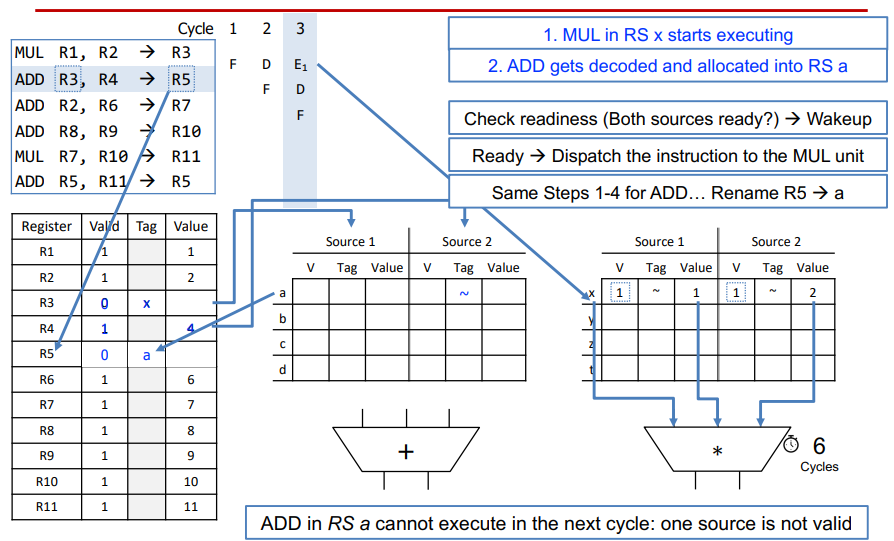

Cycle3

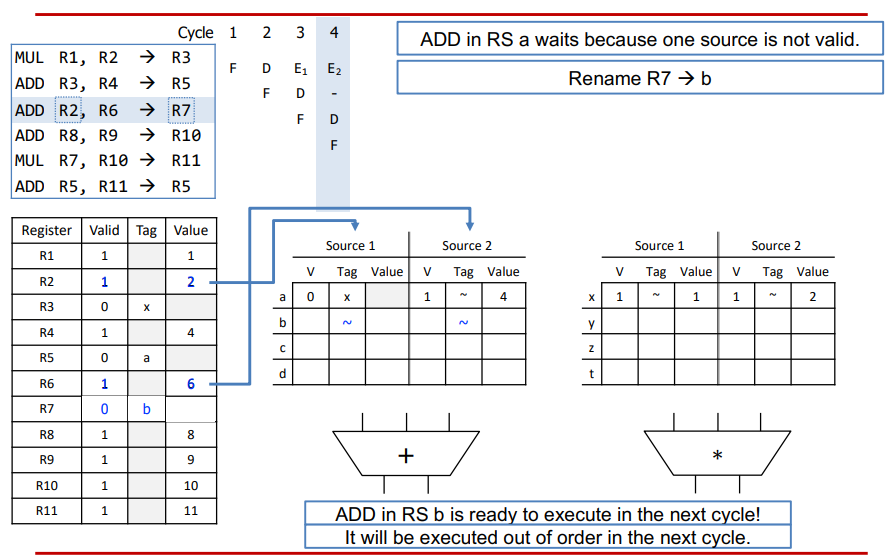

Cycle4

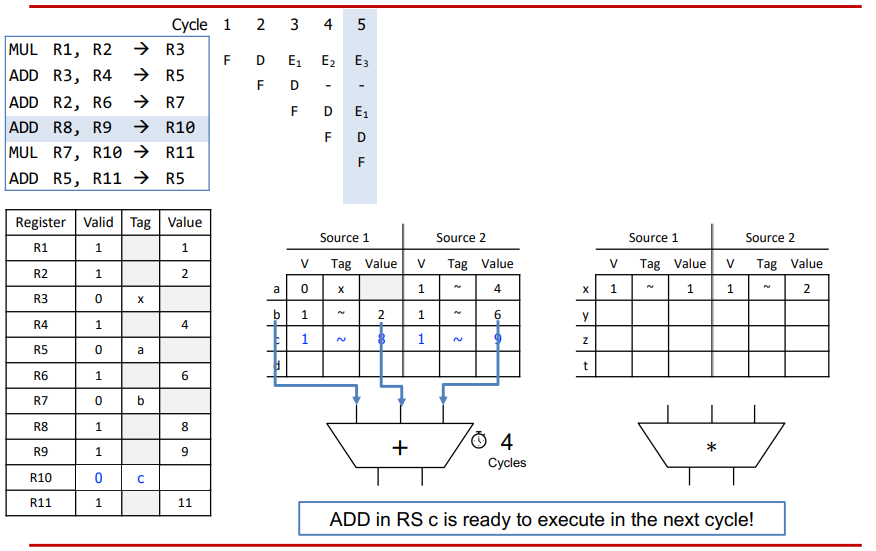

Cycle5

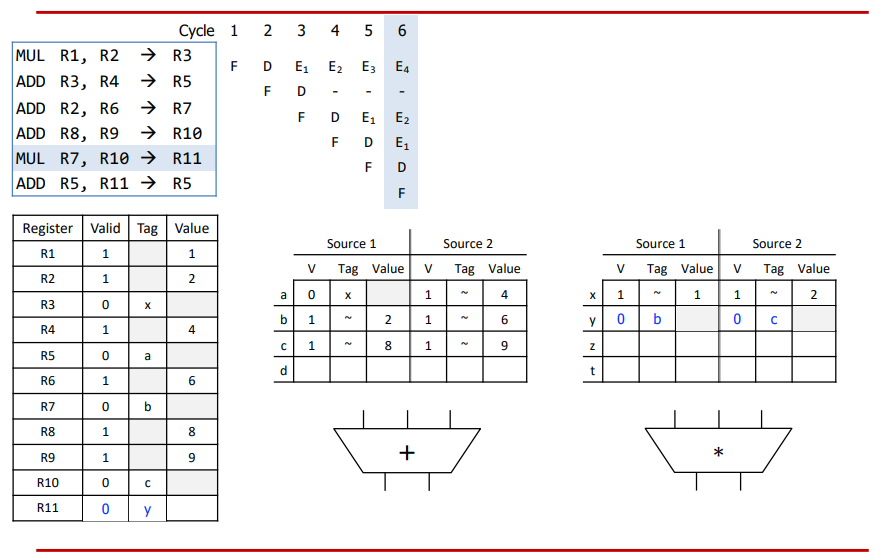

Cycle6

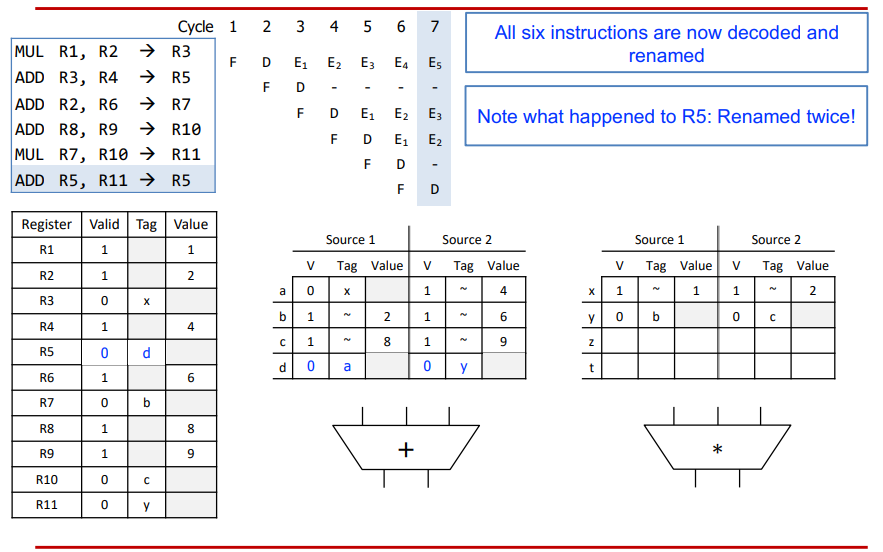

Cycle7

虽然cycle7中R5被二次标记,但是R5第一次重命名的值仍存在保留站项a中,是要比保留站项d先计算出来并广播的。

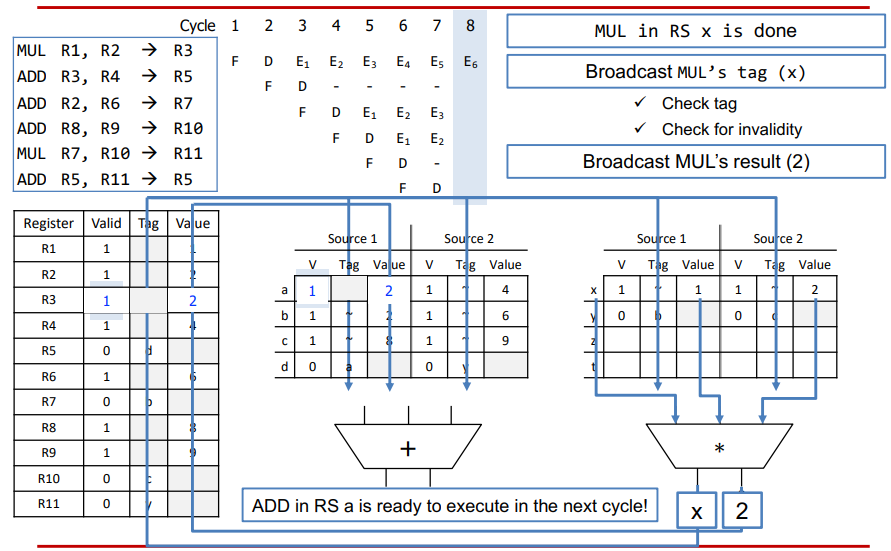

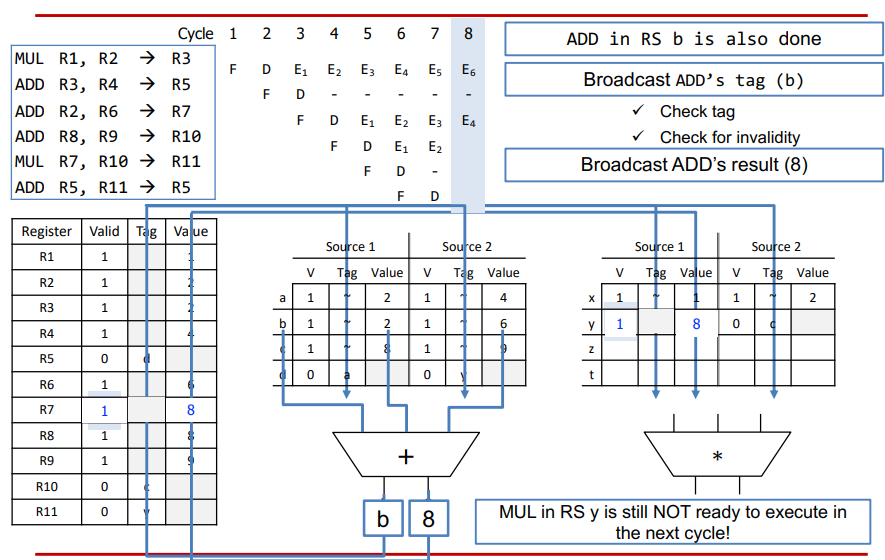

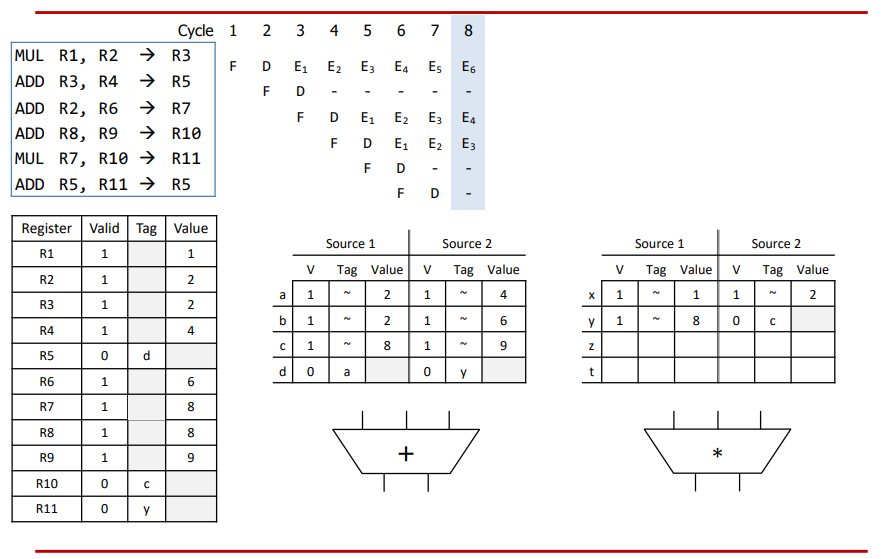

Cycle8

Cycle8

Cycle8

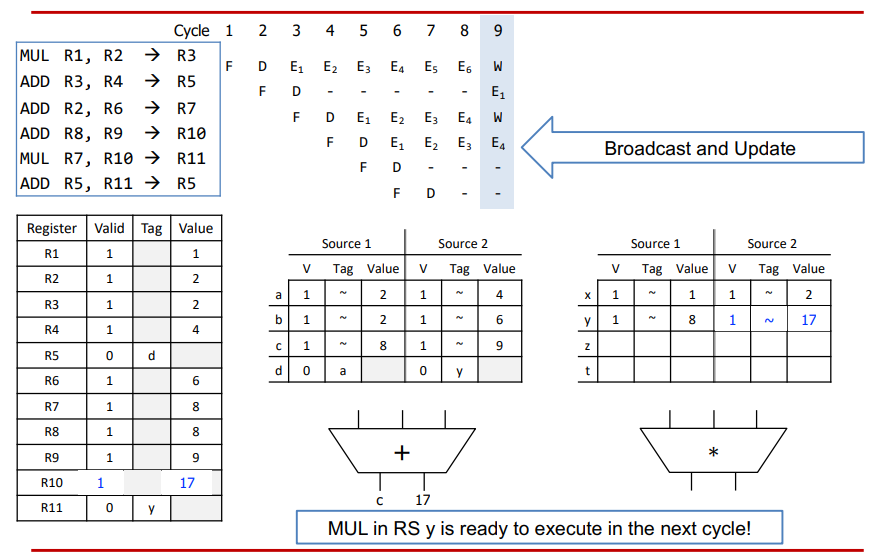

Cycle 9

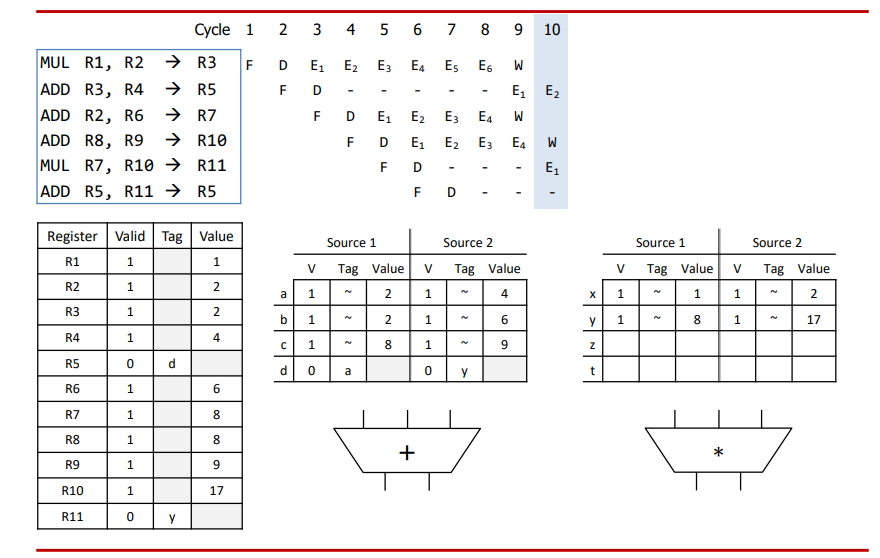

Cycle 10

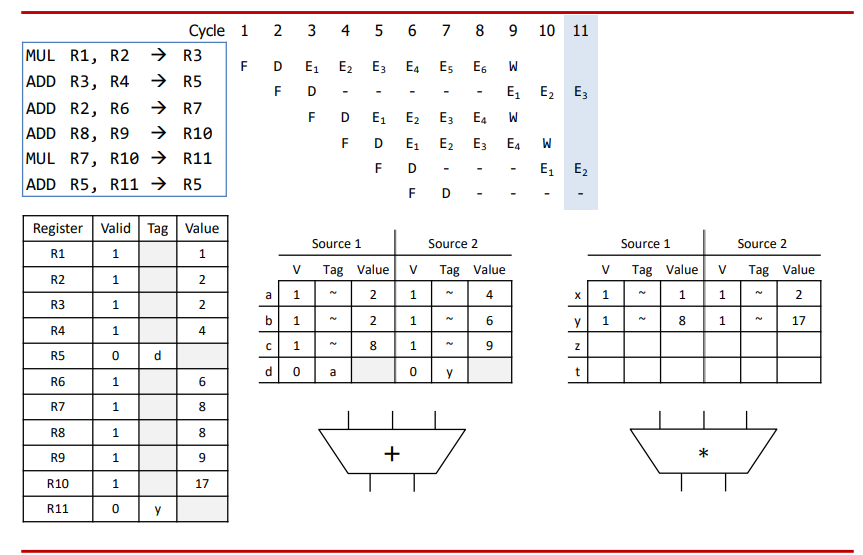

Cycle 11

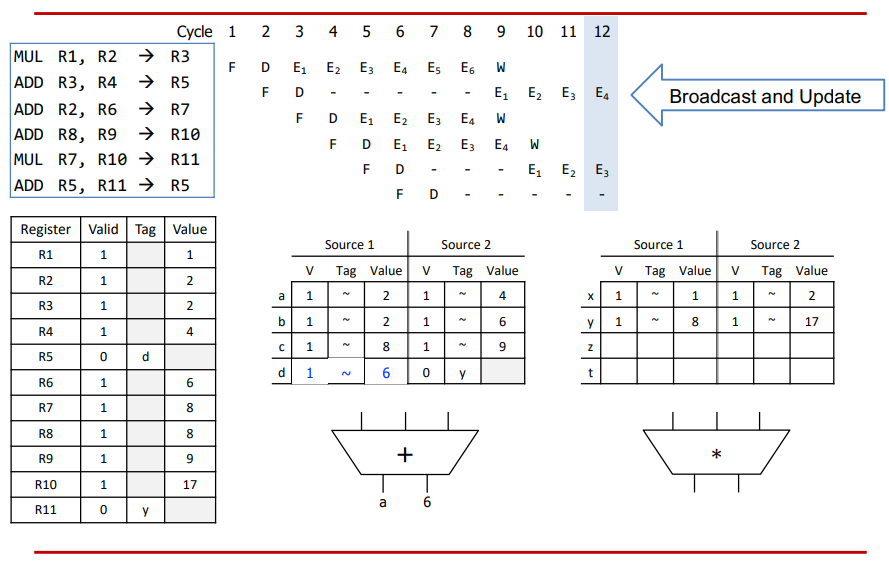

Cycle 12

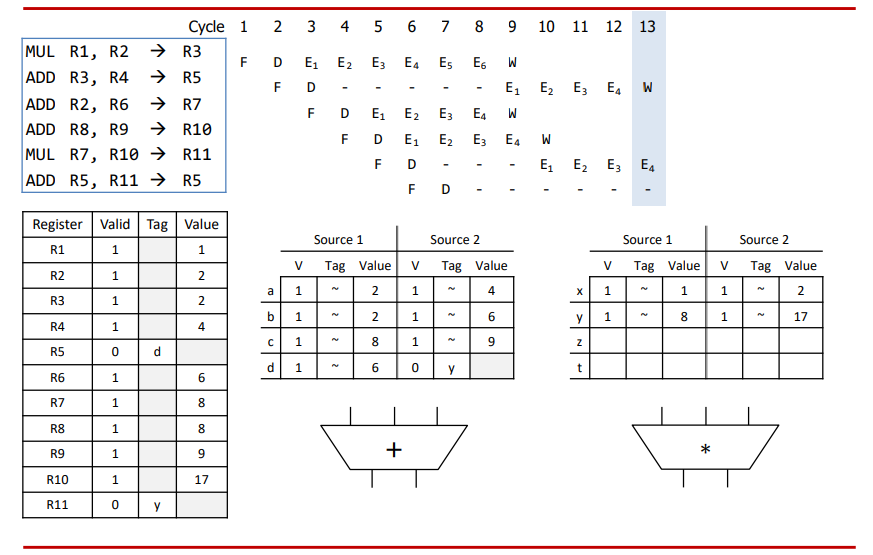

Cycle 13

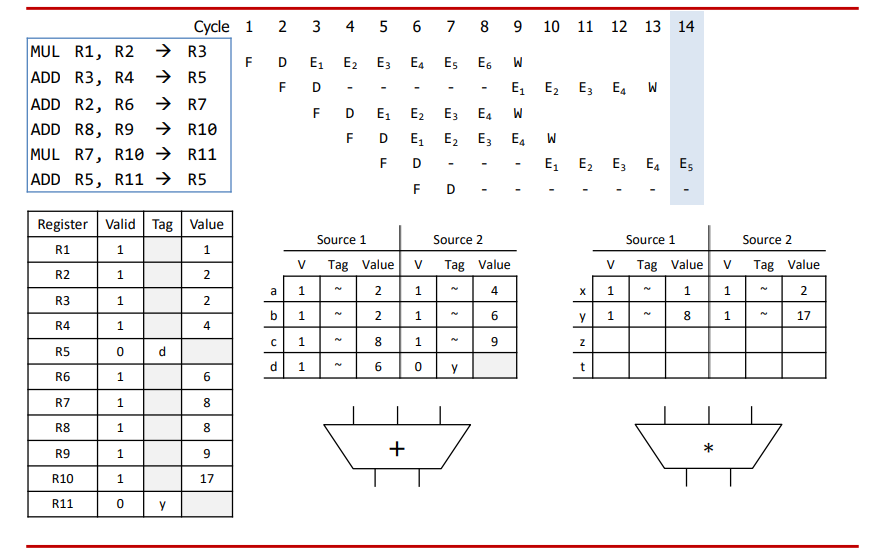

Cycle 14

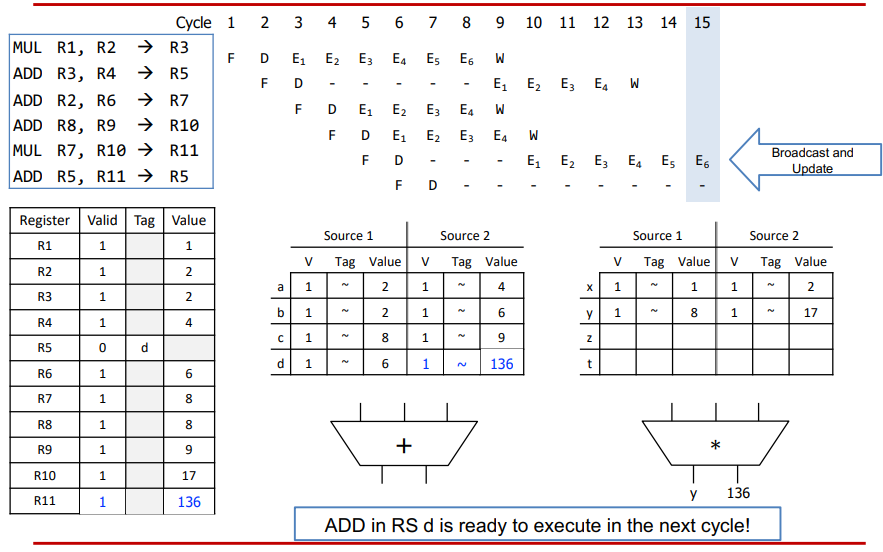

Cycle 15

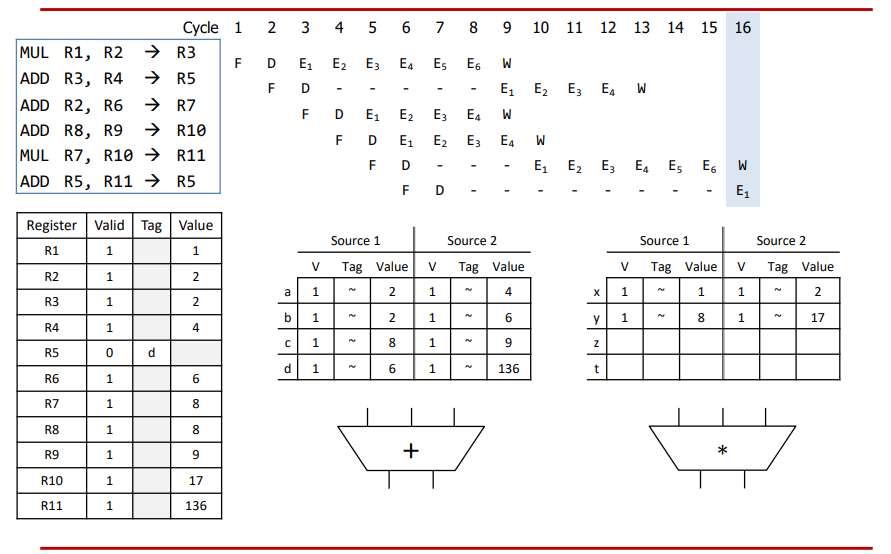

Cycle 16

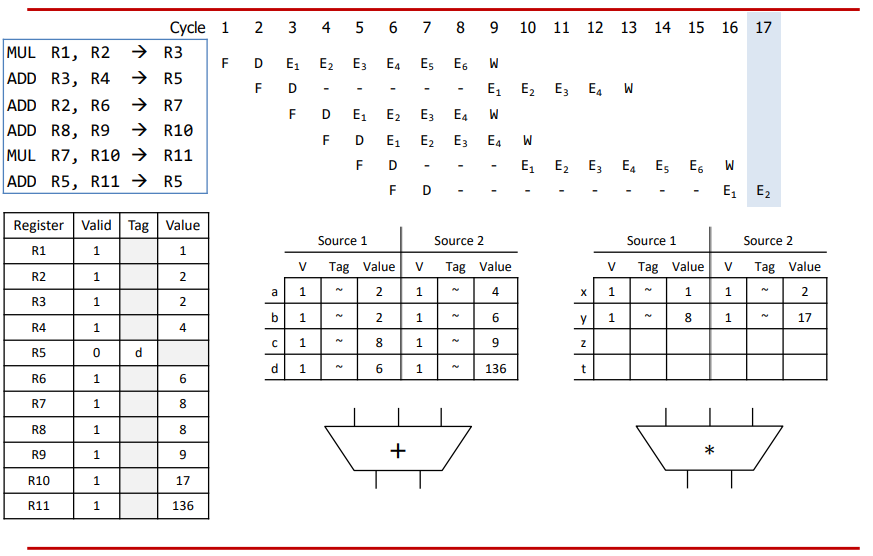

Cycle 17

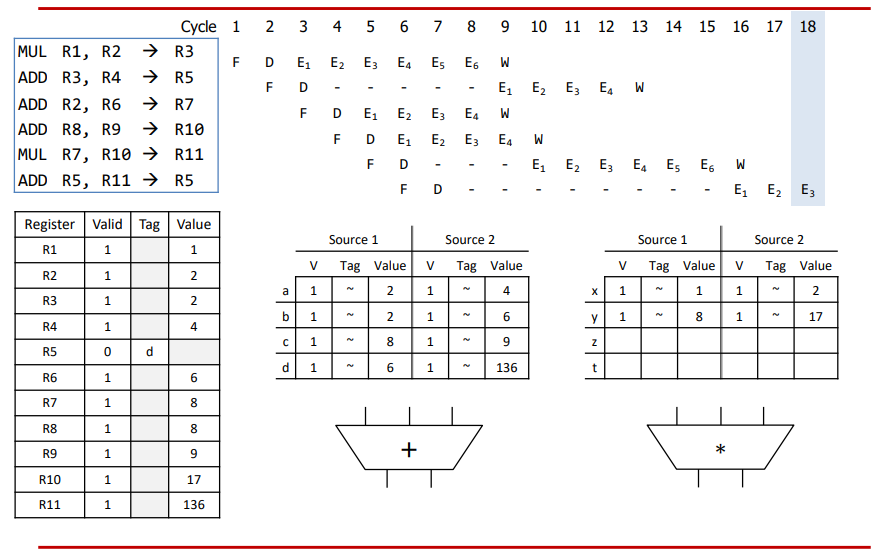

Cycle 18

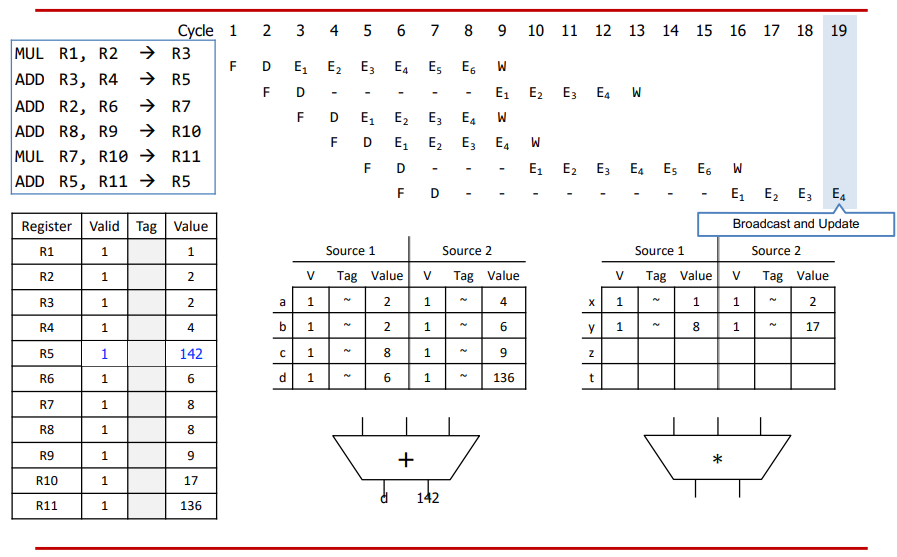

Cycle 19

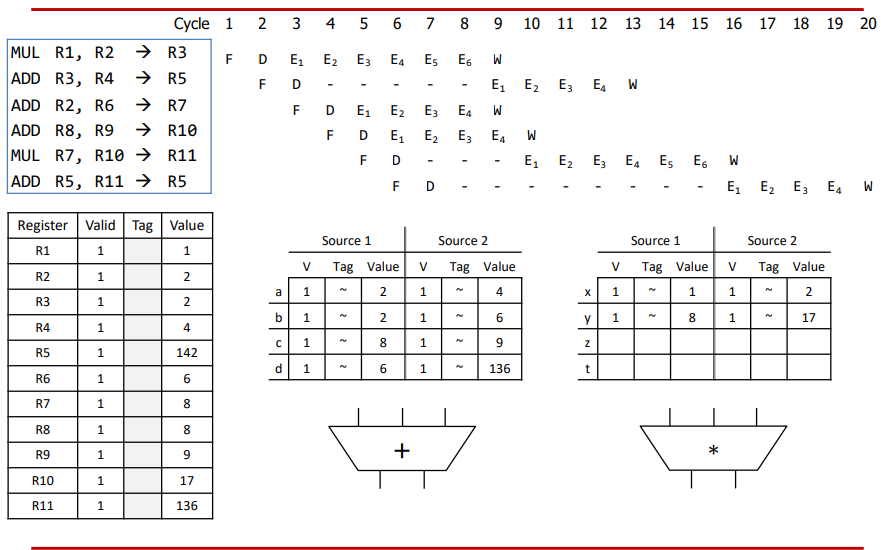

Cycle 20

Tomasulo算法性能分析

- Tomasulo算法完善的处理了数据冲突,与分支预测和猜测执行配合起来后能达到很高的性能,当今处理器仍在广泛采用

- 仍没有处理控制冲突,乱序执行仍局限在一个基本块内

- 要求高速CDB: 性能受限于Common Data Bus