1 EEPROM

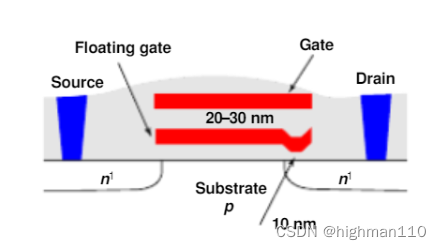

通过EPROM的原理分析我们知道,由于叠栅雪崩注入MOS晶体管(SAMOS)的结构特性(浮栅周围是二氧化硅的绝缘层),而且由于早期工艺的原因,这个二氧化硅层比较厚,势垒比较高,所以不管是往浮栅中充入电子还是擦除电子,都需要给电子充较大的能量,也就是需要更高的电压或更长的时间,很显然,加电压和加时间都不是好的选择,所以为了让电子移动更容易,就需要将这个二氧化硅绝缘层做得更薄,于是科学家们又研发了一种新的结构:FLOTOX,这也是一种浮栅存储器件,是在SAMOS的基础上,特别设置一层较薄的氧化层以产生热电子的隧道效应以实现向浮栅的注入,如下图所示,称为浮栅隧穿氧化层(FLOTOX)存储器。FLOTOX的工作原理与SAMOS相同,只是给浮栅充电方式是隧穿(Fowler-Nordheim隧穿)、而不是热电子注入。FLOTOX的工作电压较低,并且只需要一种极性的电压(正电压)即可实现编程和擦除两种功能。如下图所示,浮栅右侧有个下沉的小平台,这部分浮栅与漏极之间的绝缘介质(ONO或二氧化硅)只有10nm或更小,当把一个约10V电压加在这个薄介质之间时,电子将通过隧穿机理注入或导出浮栅。

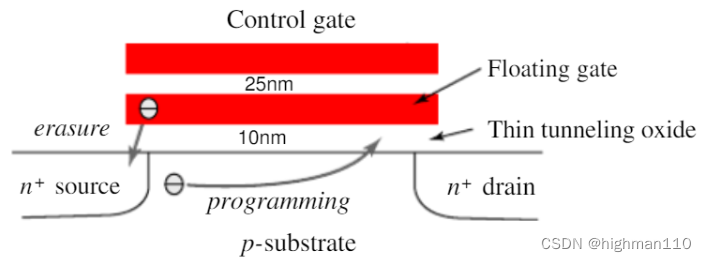

EEPROM的存储单元示意图如下:其中T1为FLOTOX晶体管,T2为选择管。

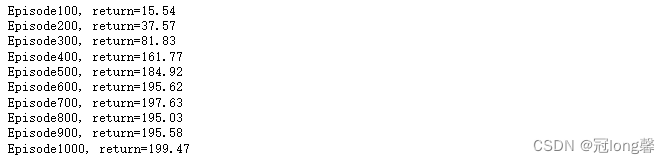

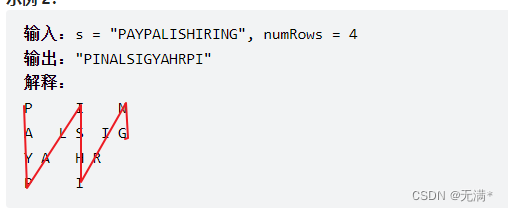

读过程:字线为5V,打开选择管T2,浮栅管控制栅极给3V电压,当浮栅中有电子时,T1截止,位线读出1,当浮栅中没有电子时,T1导通,位线上读出0。同样,位线电压经过反相器后输出。也就是没有编程过的新片子,读出来是全1。

写入:写入就是往浮栅中注入电子,就是写0,在20V的脉冲控制下,T2间歇性导通,T2导通期间,T1的漏极和源极均为0V,在T1的控制栅极的20V正脉冲作用下,漏极和栅极之间发生电子隧穿,电子从漏极注入到浮栅当中,通过脉冲控制注入的电子数量,使得T1要在控制栅极电压提高到7V才导通,所以读过程时T1栅极供电3V,才能保证有浮栅电子时是截止的,这就是这个选择管T2的作用—控制T1管的导通阈值。

擦除:擦除就是将浮栅中注入的电子拉出来,也就是写1。在20V的脉冲控制下,T2间歇性导通,T2导通期间,T1的漏极为20V脉冲,而此时控制栅极电压为0,于是漏源介质再次发生隧穿,不过这次的电子流动方向是从浮栅到漏极,一直擦除到T1的开启电压变成0V,保证读过程,浮栅没有电子时,T1栅极供电3V能正常导通。

通过以上的分析可以知道,EEPROM的存储单元有两个管子,所以相同工艺、相同容量时,EEPROM的体积更大,同时制造低于10nm的隧穿氧化层工艺较难,成本较高。一般EEPROM的容量不会很大。

2 FLASH

Flash的存储结构是EPROM和EEPROM的结合。大多数flash器件采用和EPROM一样的雪崩热电子注入的方式往浮栅充电完成写入,而采用和EEPROM一样的FN隧穿效应来完成擦除,所以它既有EPROM的单管结构,也能像EEPROM一样在线擦除,其容量比EEPROM大很多。

不同厂家推出的flash浮栅结构可能有些不同,但原理基本一致,如下为英特尔推出的ETOX(EPROM tunnel oxide)flash单元,采用了非常薄(10nm)的隧道氧化层来隔离浮栅和衬底,使用隧道氧化层的不同位置进行编程和擦除。通常情况下nor flash使用这种类似结构,编程过程为热电子注入,擦除过程为栅源之间的FN隧穿效应;而nand flash编程是利用栅漏之间的FN隧穿,擦除是利用栅极和衬底之间的FN隧穿。

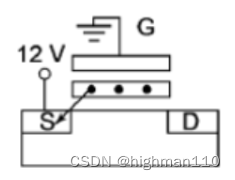

写入:在漏极加6V电压,栅极加12V脉冲,漏源之间发生雪崩击穿产生热电子,热电子在12V脉冲作用下,穿过薄隧道氧化层进入浮栅中,通过脉冲控制注入的电子数量。

擦除:源极加12V ,栅极接地,源栅之间发生FN隧穿,将浮栅中的电子拉回源极。

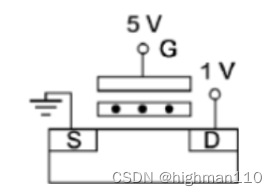

读取:字线接源极为5V,位线接漏极,预充电到高电平。当浮栅中没有电子时,管子导通,位线被拉低,经反相器输出1,当浮栅中有电子时,电子截止,位线保持预充电电压,经反相器后输出0。

为什么写入不能和擦除一样用隧穿效应呢?我觉得是可以的,这个依据所用浮栅晶体管的浮栅和源极的重叠区域大小来定,如果浮栅就在源极正上方,12V产生的场强全部集中在这个隧穿区,那是可以达到隧穿的发生条件的。如果重叠区域比较小,12V产生的场强被分散,则不足以发生隧穿。而擦除时12V在源极上,源极的区域小,能够在与浮栅的重叠区形成的小电容中产生大场强,达到了隧穿的条件。这只是技术的选择问题,可以选择加大电压或者把氧化层做的更薄来提升隧穿概率。

为什么擦除要在源极接12V呢?在flash存储阵列中,源极是接在一起的,这样可以实现以块为单位快速擦除(NOR flash架构),如果存储阵列源极不是接在一起,则高压不是加在源极,而是加载这些存储阵列的公共衬底上(NAND flash架构)。为什么高压加在衬底上也能发生浮栅到源极的隧穿?我们知道浮栅晶体管就是在原来MOS的基础上增加了一个浮栅,而MOS管本身的源极和衬底是相连的,所以衬底加了高压相当于源极加了高压。

以上两个问题都是我个人的理解,大家自行斟酌判断,欢迎指正。