文章目录

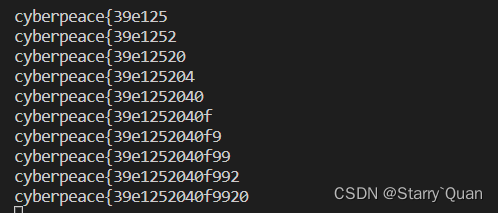

- GPIO

- 8.1 简介

- 8.2 配置概述

- 8.3 ADC引脚上的数字输入(AIO)

- 8.4 数字通用I/O控制

- 8.5 输入限定

- 8.5.1 异步输入

- 8.5.2 仅与SYSCLKOUT同步

- 8.5.3 使用采样窗口进行鉴定

- 8.6 SPI信号

- 8.7GPIO和外设引脚复用

- 8.7.1GPIO复用

- 8.7.2 外设复用

- 8.8 内部上拉配置要求

- 总结

GPIO

GPIO模块控制设备的数字和模拟I/O多路复用,使用共享引脚来最大化应用灵活性。引脚由其通用I/O名称命名(例如,GPIO0、GPIO25、GPIO58)。这些引脚可以单独选择作为数字I/O(也称为GPIO模式)操作,或连接到几个外围I/O信号之一。输入信号可以被限定为去除不需要的噪声。

8.1 简介

除了CPU控制的I/O能力外,多达12个独立的外围信号在单个GPIO使能引脚上复用。每个引脚输出可以由外围设备或两个CPU主机(CPU1、CPU1.CLA)之一控制。有两个I/O端口:

- Port A: GPIO0~GPIO31

- Port B: GPIO32~ GPIO59

该设备上的模拟信号与数字输入复用。这些模拟IO(AIO)引脚不具有数字输出能力。模拟IO(AIO)引脚分配给单个端口:

- Port H: GPIO224~GPIO24

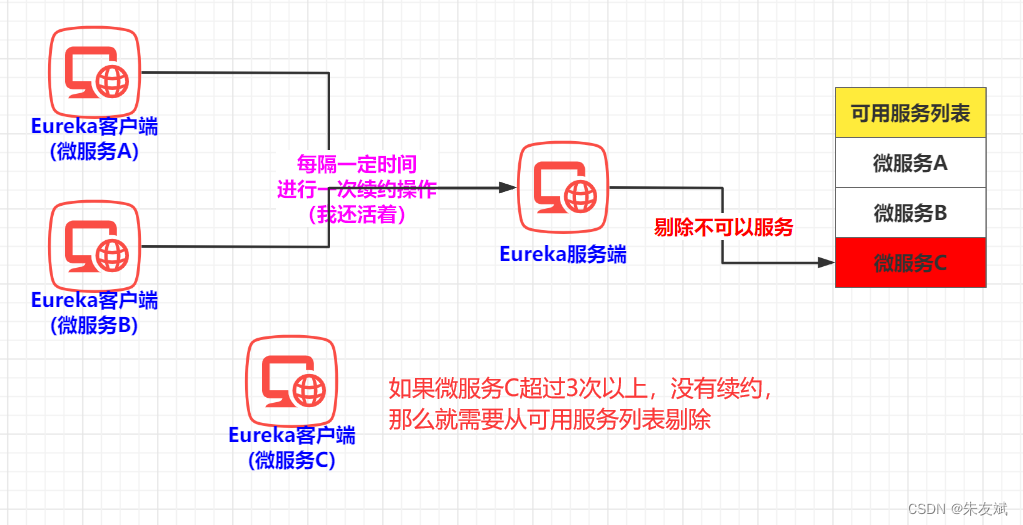

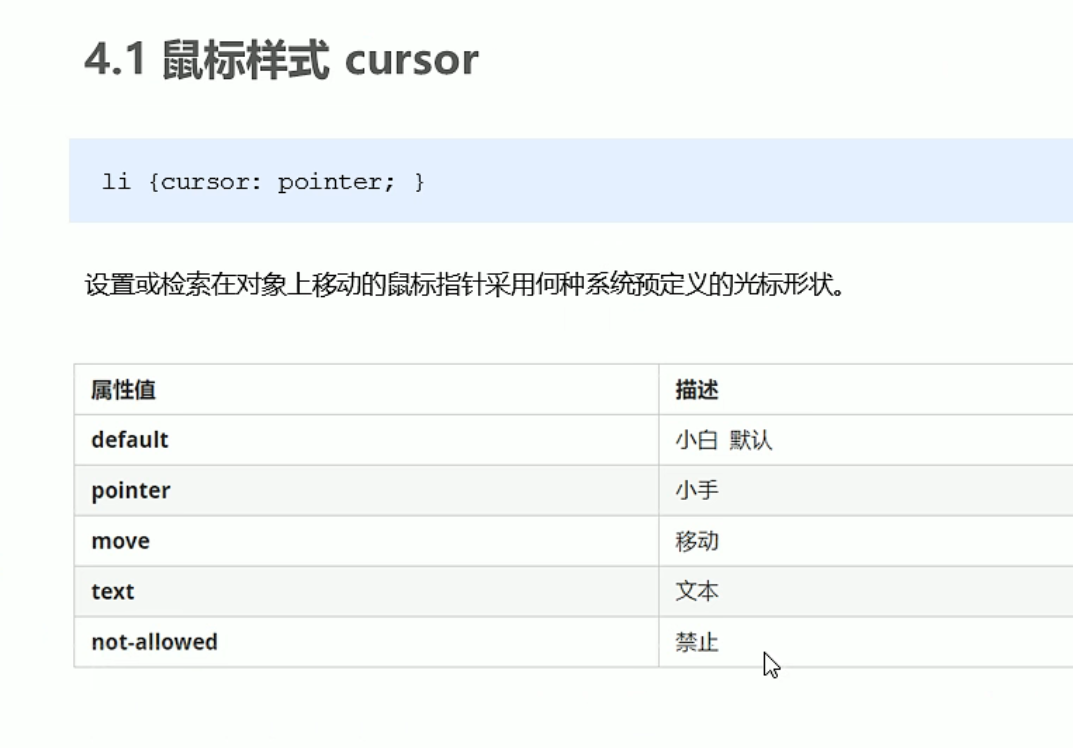

图8-1中有两个关键特征需要注意。第一个是输入和输出路径完全分开,只在引脚处连接。第二个是外设复用发生在远离引脚的地方。因此,CPU和CLA总是可以独立于CPU主控和外设复用读取管脚的物理状态。同样,外部中断也可以从外设活动中产生。所有引脚选项(如输入限定和漏极开路输出)均适用于所有主机和外围设备。然而,外设复用、CPU复用和引脚选项只能由CPU1配置。

8.2 配置概述

IO口配置步骤

- 规划设备引脚

列出应用程序所需的所有外设。使用设备数据手册中的外设多路复用器信息,选择用于外围信号的GPIO。决定将剩余的GPIO中的哪一个用作每个CPU和CLA的输入和输出。

一旦选择了外围复用,就可以通过将适当的值写入GPyMUX1/2和GPyMMUX1/2寄存器来实现复用。当更改引脚的GPyMUX值时,请始终先将相应的GPyMUX位设置为零,以避免多路复用器中出现故障。默认情况下,所有引脚都是通用I/O,而不是外设信号。 - (可选)启用内部上拉电阻器

要启用或禁用上拉电阻器,请写入GPIO上拉禁用寄存器(GPyPUD)中的相应位。默认情况下禁用所有上拉。当没有外部信号驱动输入引脚时,可以使用引体向上将其保持在已知状态 - 选择输入限定

如果引脚用作输入,请指定所需的输入资格(如果有)。输入限定采样周期在GPyCTRL寄存器中选择,而限定类型在GPyQSEL1和GPyQSEL 2寄存器中选择。默认情况下,所有资格与等于PLLSYSCLK的采样周期同步。 - 选择任何通用I/O引脚的方向

对于配置为GPIO的每个引脚,使用GPyDIR寄存器将引脚的方向指定为输入或输出。默认情况下,所有GPIO引脚都是输入。在将引脚更改为输出之前,通过将要驱动的值写入GPySET、GPyCLEAR或GPyDAT寄存器来加载输出锁存器。加载锁存后,写入GPyDIR以更改引脚方向。默认情况下,所有输出锁存器均为零。 - 选择低功耗模式唤醒源

GPIO 0-63可用于将系统从低功耗模式唤醒。要选择一个或多个GPIO进行唤醒,请写入GPIOLPMSEL0和GPIOLPMSEL1寄存器中的相应位。这些寄存器是CPU系统寄存器空间的一部分。有关低功耗模式和GPIO唤醒的更多信息,请参阅“系统控制和中断”一章中的“低功耗模式”部分 - 选择外部中断源

配置外部中断是一个两步过程。首先,必须启用中断本身,并且必须使用XINTnCR寄存器配置其极性。其次,必须通过分别选择输入X-BAR信号4、5、6、13和14的源来设置XINT1-5 GPIO引脚。有关输入X-BAR架构的更多信息,请参阅Crossbar(X-BAR)一章。

8.3 ADC引脚上的数字输入(AIO)

端口H上的GPIO(GPIO224–GPIO253)与模拟引脚复用。这些也被称为AIO。这些引脚只能在输入模式下工作。默认情况下,这些引脚用作模拟引脚,GPIO处于高阻抗状态。GPHAMSEL寄存器用于为数字或模拟操作配置这些引脚。

8.4 数字通用I/O控制

通过使用以下寄存器,可以更改配置为GPIO的引脚上数字电平。

- GPyDAT寄存器

每个I/O端口都有一个数据寄存器。数据寄存器中的每个位对应于一个GPIO引脚。无论管脚如何配置(GPIO或外围功能),数据寄存器中的相应位都反映了限定后管脚的当前状态。写入GPyDAT寄存器会清除或置位相应的输出锁存器,如果该引脚被启用为通用输出(GPIO输出),则该引脚也会被驱动为低电平或高电平。如果引脚未配置为GPIO输出,则该值被锁存,但引脚未被驱动。只有当该引脚后来被配置为GPIO输出时,锁存值才被驱动到该引脚上。

使用GPyDAT寄存器更改输出引脚的电平时,请小心不要意外更改另一个引脚的电平。例如,为了通过使用读-修改-写指令写入GPADAT寄存器位0来改变GPIOA1的输出锁存器电平,如果另一个I/O端口a信号在指令的读和写阶段之间改变电平,则会出现问题。以下是发生这种情况的原因分析:

GPyDAT寄存器反映引脚的状态,而不是锁存器的状态。这意味着寄存器反映实际引脚值。然而,当寄存器被写入时,新的管脚值被反映回寄存器时,两者之间存在延迟。当在随后的程序语句中使用该寄存器来改变GPIO引脚的状态时,这可能会造成问题。下面显示了一个示例,其中两个程序语句试图驱动两个不同的GPIO引脚,这两个引脚当前处于低到高状态。

如果在GPyDAT寄存器上使用读-修改-写操作,由于第一条指令(I1)的输出和输入之间的延迟,第二条指令(I2)读取旧值并将值写回。

GpioDataRegs.GPADAT.bit.GPIO1 = 1; //I1 performs read-modify-write of GPADAT

GpioDataRegs.GPADAT.bit.GPIO2 = 1; //I2 also a read-modify-write of GPADAT

//GPADAT gets the old value of GPIO1 due to the delay

第二条指令等待第一条指令完成写入,这是因为在该外围帧上进行了写入之后进行了读取保护。然而, 在写入(I1)到GPyDAT位这反映了上的新值(1)存在一定的延迟。在此滞后期间,第二条指令读取GPIO1(0)的旧值,并将该值与GPIO2(1)的新值一起写回。因此,GPIO1引脚保持低位。

一个答案是在指令之间插入一些NOP。更好的答案是使用GPySET/GPYLEAR/GPyTOGGLE寄存器而不是GPyDAT寄存器。这些寄存器总是读取0并写入0无效。仅可指定需要更改的位,而不干扰目前正在改变其他位。 - GPySET寄存器

该寄存器用于在不干扰其他引脚的情况下将指定的GPIO引脚驱动为高电平。每个I/O端口有一个设置寄存器,每个位对应一个GPIO引脚。设置寄存器总是读回0。如果相应的引脚被配置为输出,则将1写入设置寄存器中的该位,将输出锁存器设置为高电平,相应的引脚将被驱动为高电平。**如果引脚未配置为GPIO输出,则该值被锁存,但引脚未被驱动。只有当该引脚后来被配置为GPIO输出时,锁存值才被驱动到该引脚上。**将0写入设置寄存器中的任何位都无效。 - GPyCLEAR寄存器

该寄存器用于在不干扰其他引脚的情况下将指定的GPIO引脚驱动为低电平。每个I/O端口都有一个清除寄存器。清除寄存器总是读回0。如果相应的引脚被配置为通用输出,则向清除寄存器中的相应位写入1将清除输出锁存器,引脚被驱动为低电平。如果引脚未配置为GPIO输出,则该值被锁存,但引脚未被驱动。只有当该引脚后来被配置为GPIO输出时,锁存值才被驱动到该引脚上。将0写入清除寄存器中的任何位都无效。 - GPyTOGGLE寄存器

触发寄存器用于将指定的GPIO引脚驱动到相反的电平,而不会干扰其他引脚。每个I/O端口都有一个切换寄存器。切换寄存器总是读回0。如果相应的管脚被配置为输出,则将1写入触发寄存器中的该位会翻转输出锁存器,并沿相反方向拉动相应的管。也就是说,如果输出引脚被驱动为低电平,那么将1写入触发寄存器中的相应位会将引脚拉高。同样,如果输出引脚为高,则向触发寄存器中的相应位写入1将引脚拉低。如果引脚未配置为GPIO输出,则该值被锁存,但引脚未被驱动。只有当该引脚后来被配置为GPIO输出时,锁存值才被驱动到该引脚上。将0写入切换寄存器中的任何位都无效

8.5 输入限定

输入确认方案设计得非常灵活。通过配置GPyQSEL1和GPyQSEL 2寄存器,为每个GPIO引脚选择输入资格类型。在GPIO输入引脚的情况下,可以将鉴定指定为仅与SYSCLKOUT同步或通过采样窗口进行鉴定。对于配置为外围输入的引脚,除了与SYSCLKOUT同步或由采样窗口限定外,输入也可以是异步的。

8.5.1 异步输入

此模式用于不需要输入同步或由外围设备本身执行同步的外围设备。示例包括通信端口McBSP、SCI、SPI和I2C。此外,ePWM跳闸区(TZn)信号的功能与SYSCLKOUT的存在无关。

注意:当外围设备本身执行同步时,使用输入同步可能会导致意外结果。在这种情况下,用户必须确保GPIO引脚配置为异步。

8.5.2 仅与SYSCLKOUT同步

这是复位时所有引脚的默认确认模式。在此模式下,输入信号仅与系统时钟(SYSCLKOUT)同步。因为输入信号是异步的,所以需要一个SYSCLKOUT延迟周期来改变设备的输入。未对信号进行进一步鉴定。

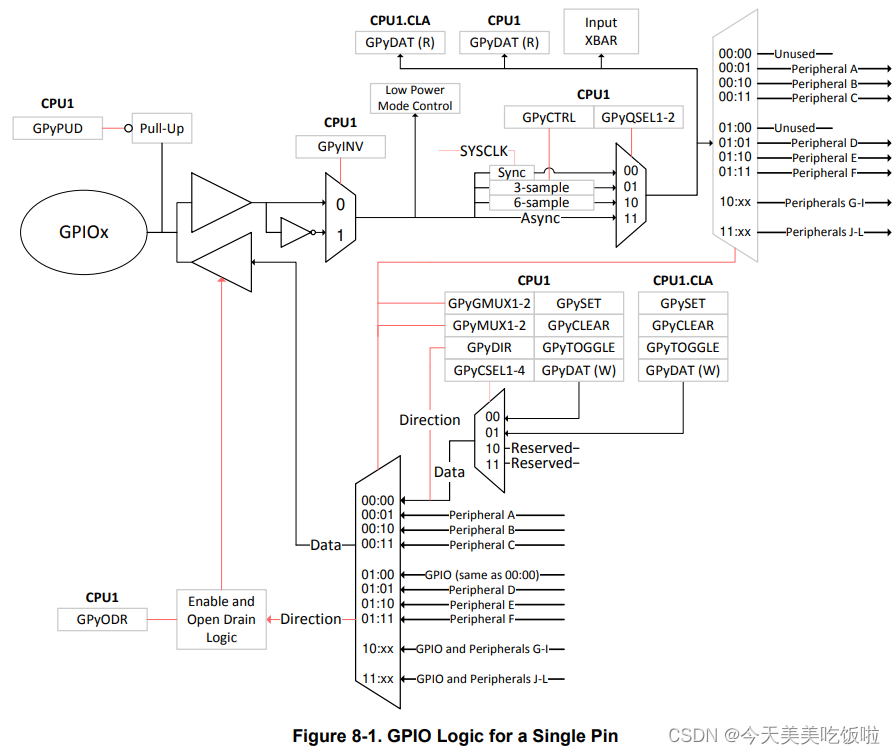

8.5.3 使用采样窗口进行鉴定

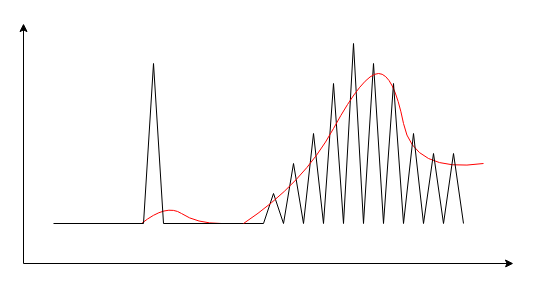

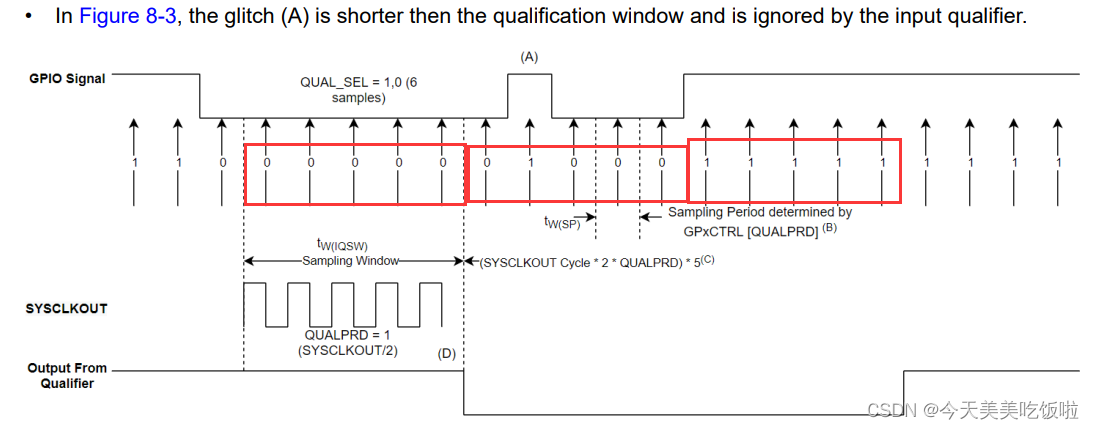

在此模式下,信号首先与系统时钟(SYSCLKOUT)同步,然后在允许输入改变之前,通过指定的周期数进行限定。图8-2和图8-3显示了如何执行输入确认以消除不需要的噪声。用户为此类鉴定指定了两个参数:

- 采样周期或信号采样频率

- 采样数量。

(原文To qualify the signal,感觉不知道怎么翻译才更妥帖一点)为了使采集到的信号真正是外部输入的电平值,CPU以规则的周期采样输入信号。采样周期由用户指定,并确定采样之间的持续时间,或相对于CPU时钟(SYSCLKOUT)采样信号的频率。以下使是几个关键指标:

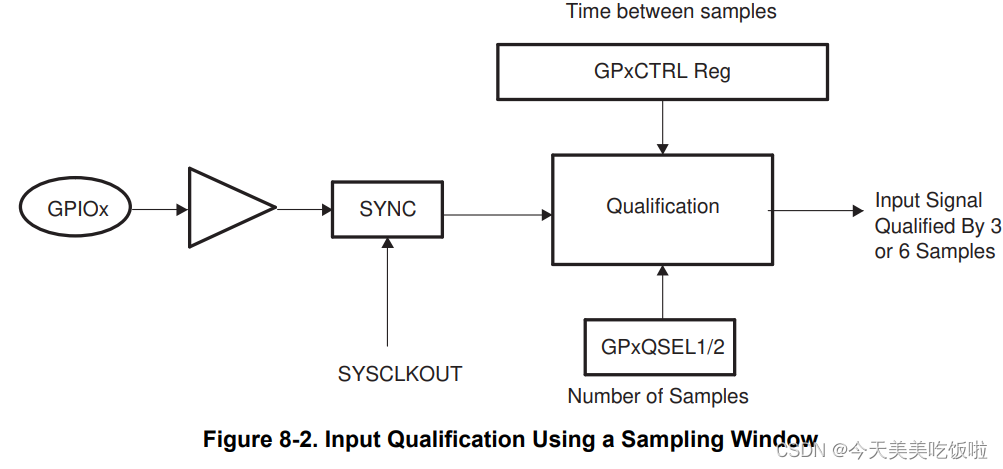

- 采样率

采样周期由GPxCTRL寄存器中的限定周期(QUALPRDn)位指定。采样周期可配置为8个输入信号的组。例如,GPIO0至GPIO7使用GPATRL[QUALPRD0]设置,GPIO8至GPIO15使用GPATRL[QUALPRD 1]。表8-1和表8-2显示了采样周期或采样频率与GPxCTRL[QUALPRDn]设置之间的关系。

- 采样次数

信号的采样次数是限定选择(GPAQSEL1、GPAQSEL2、GPBQSEL1和GPBQSSEL2)寄存器中指定的三次采样或六次采样。当三个或六个连续采样的结果相同时,输入变化将传递到设备。 - 总采样窗宽

采样窗口是对输入信号进行采样的时间,如图8-3所示。通过使用采样周期的方程以及要采集的样本数量,可以确定窗口的总宽度。

为了使输入限定符检测输入中的变化,信号的电平必须在采样窗口宽度的持续时间内稳定或更长。

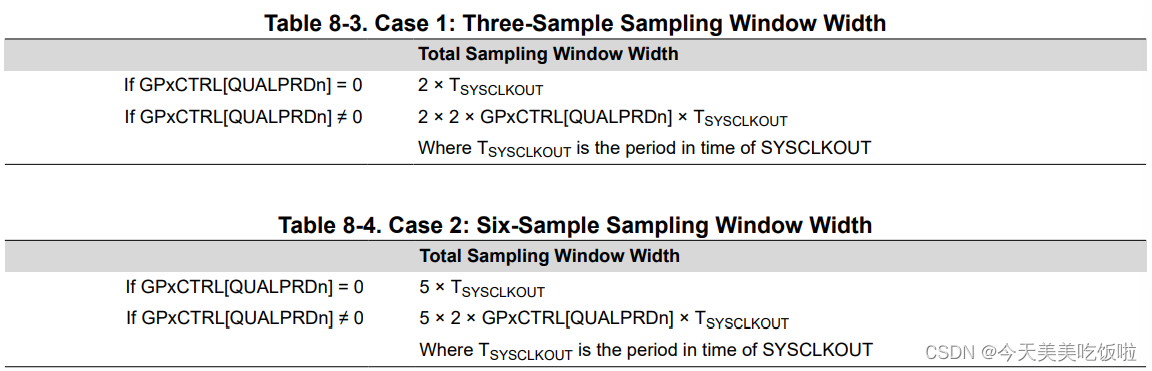

窗口内的采样周期数总是比采样的数量少一个。对于三个采样窗口,采样窗口宽度为两个采样周期宽度,采样周期定义见表8-1。同样,对于六个采样窗口,采样窗口宽度为五个采样周期宽。表8-3和表8-4显示了用于根据GPxCTRL[QUALPRDn]和采样数量确定总采样窗口宽度的计算结果。

A处的扰动比采样窗口短,所以被滤除了。

8.6 SPI信号

该设备上的SPI模块具有高速模式,可实现40 Mbps通信。为了实现最高可能的速度,在每个SPI的单个GPIO多路复用器选项上使用特殊的GPIO配置。当不处于高速模式(HS_mode=0)时,SPI也可以使用这些GPIO。

8.7GPIO和外设引脚复用

8.7.1GPIO复用

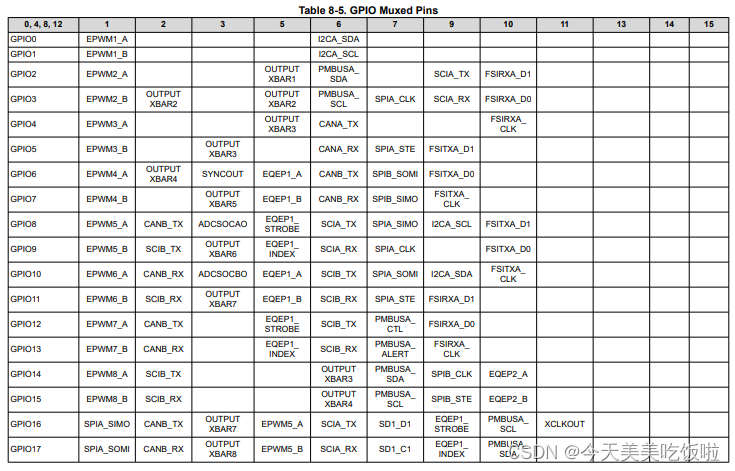

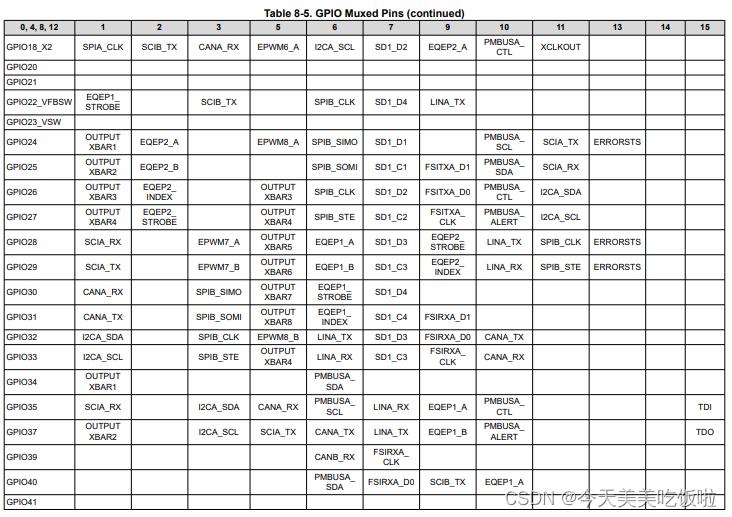

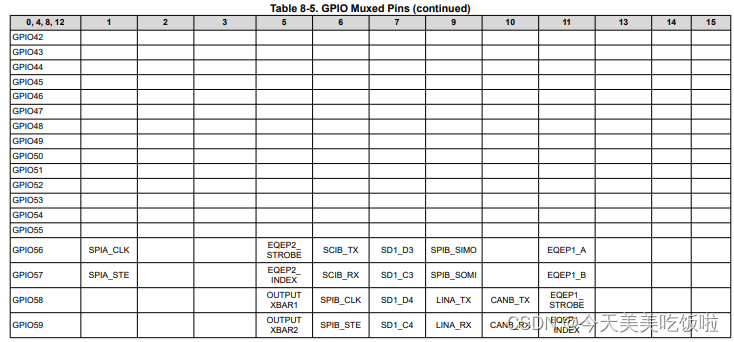

多达12个不同的外围功能与通用输入/输出(GPIO)功能一起复用到每个引脚。这允许您选择最适合特定应用程序的外围设备混合和引脚输出。复用组合和定义请参见表8-5。

8.7.2 外设复用

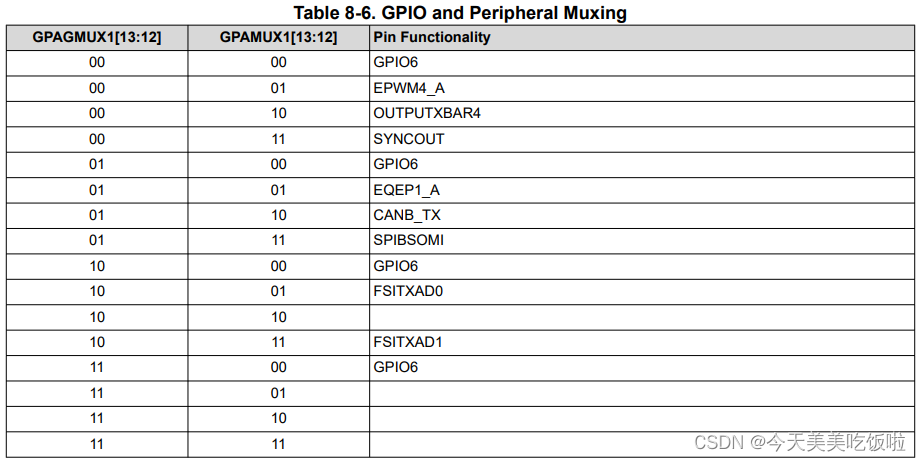

例如,通过向GPAGMUX[13:12]和GPAMUX[13:12]写入来控制GPIO6引脚的多路复用。通过写入这些位,GPIO6被配置为通用数字I/O或四种不同外围

这些设备具有不同的复用方案。如果外围设备在特定设备上不可用,则该多路复用器选择将保留在该设备上,无法使用。

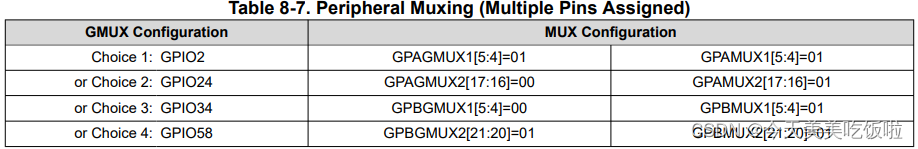

一些外围设备可以通过多路复用寄存器分配给多个引脚。例如,OUTPUTXBAR1可以分配给GPIO 2、24、34或58,具体取决于各个系统要求。表8-7显示了一个示例。

8.8 内部上拉配置要求

复位时,GPIO处于输入模式,并禁用内部上拉。未驱动的输入可以浮动到中轨电压,并在输入缓冲器上造成浪费的直通电流,或者说电平不确定。用户应始终将每个GPIO置于以下配置之一:

- 输入模式,由另一个组件在板上驱动至高于Vih或低于Vil的水平,即确定的高电平或低电平

- 启用GPIO内部上拉的输入模式,使电平确定

- 输出模式

在具有较少引脚数封装的设备上,默认启用未绑定GPIO上的上拉,以防止浮动输入。用户应注意避免在应用程序代码中禁用这些下拉菜单。

在176 PTP封装中的设备上,必须启用任何内部未绑定GPIO的上拉,以防止浮动输入。TI在controlSUITE/C2000Ware中提供了一些函数,用户可以调用这些函数来启用所使用封装的任何未绑定GPIO上的上拉。此函数GPIO_EnabledUnboundIOPullups()位于(Device)_Sysctrl.c文件中,默认情况下从InitSysCtrl()调用。用户应注意避免在应用程序代码中禁用这些下拉菜单。

总结

- GPIO有数字GPIO和模拟GPIO之分,通常称前者为GPIO,后者为AIO以作区分。

- GPIO具有输入输出两种功能,并且每一个GPIO都能进行引脚复用,选择性地工作在简单IO以输出电平或外设如ePWM、eCAP、SPI、I2C等。

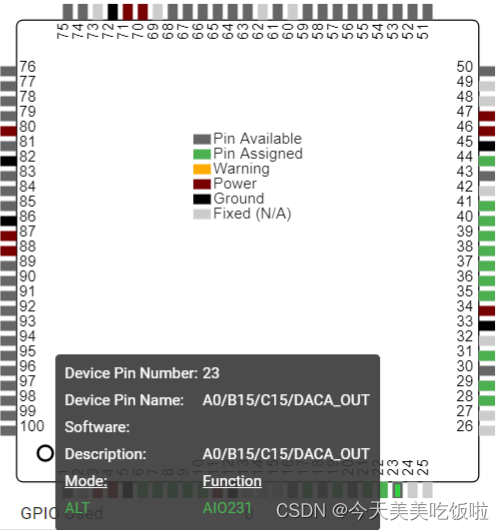

- 手册上说AIO只能工作在输入模式,感觉这里有点欠妥。AIO231,也就是A0/B15/C15/DACA_OUT。这个引脚就是能输出DACA_OUT信号的。不知道是不是我理解的有点问题。

- GPIO输出模式时,可以通过写GPxSET,GPxCLEAR,GPxTOGGLE以设置引脚的电平值。

- GPIO输入模式时,必须使能内部上拉,并选择输入限定方式。