最近要用到DAC生成数据波形,但是都是英文不好阅读,于是花费点时间翻译了大致数据内容并记录

一、特性

AD5308:16导联TSSOP中的8个缓冲8位DAC

A版本:±1 LSB INL,B版本:±0.75 LSB INR

AD5318:16导联TSSOP中的8个缓冲10位DAC

A版本:±4 LSB INL,B版本:±3 LSB INR

AD5328:16导联TSSOP中的8个缓冲12位DAC

A型:±16 LSB INL,B型:±12 LSB INR

低功率操作:0.7 mA@3 V

通过所有代码的设计保证单调性

在3 V时功率降低至120 nA,在5 V时功率下降至400 nA

双缓冲输入逻辑

缓冲/非缓冲/VDD参考输入选项

输出范围:0 V至VREF或0 V至2 VREF

通电复位至0 V

可编程性

单个通道断电

同时更新输出(LDAC)

低功耗,SPI-®,QSPI-™, 微导线-™, 和DSP兼容的3线串行接口

片上轨对轨输出缓冲放大器

温度范围:−40°C至+125°C

适用于汽车应用

二、应用

便携式电池供电仪器、数字增益和偏移调整、可编程电压和电流源

光网络、自动测试设备、移动通信、可编程衰减器、工业过程控制

三、说明

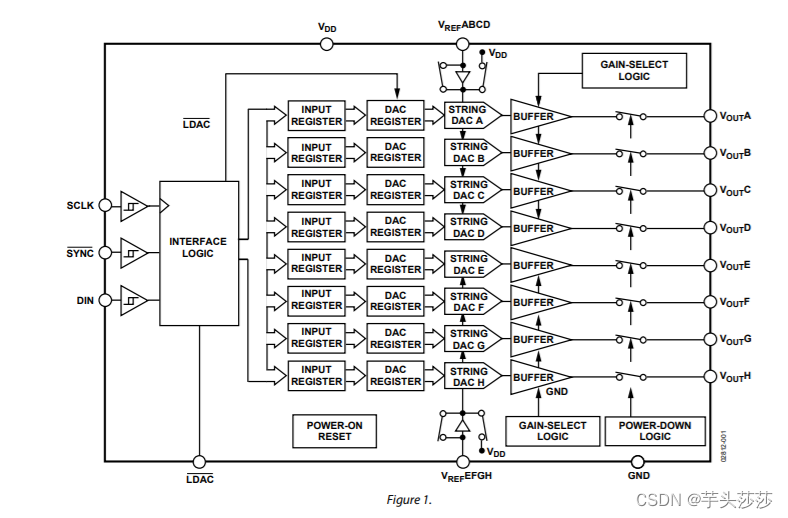

AD5308/AD5318/AD5328是16引脚TSSOP中的八进制8位、10位和12位缓冲电压输出DAC。它们在单个2.5 V至5.5 V电源下工作,通常消耗0.7 mA(3 V)。它们的片上输出放大器允许输出以0.7 V/μ。AD5308/AD5318/AD5328使用一个多功能的3线串行接口,其时钟频率高达30 MHz,与标准SPI、QSPI、MICROWIRE和DSP接口标准兼容。

八个DAC的参考源于两个参考引脚(每4个通道DAC一个参考,VREABCD,VREEFGH)。这些参考输入可以配置为缓冲、非缓冲或VDD输入。这些部件包含一个通电复位电路,它确保DAC输出高达0V的电源,并保持在那里,直到对设备进行有效写入。所有DAC的输出可以是

使用异步LDAC输入同时更新。(意思是SPI将数据传输进入后,需要再到单独控制LDAC管脚才能更新DAC)

这些部件具有断电功能,可将设备的电流消耗降低到5V时的400 nA(3V时为120 nA)。

DAC的八个通道可以单独断电。

所有三个部件都在同一个引脚中提供,这允许用户选择适合其应用的分辨率,而无需重新设计电路板。

四、功能框图

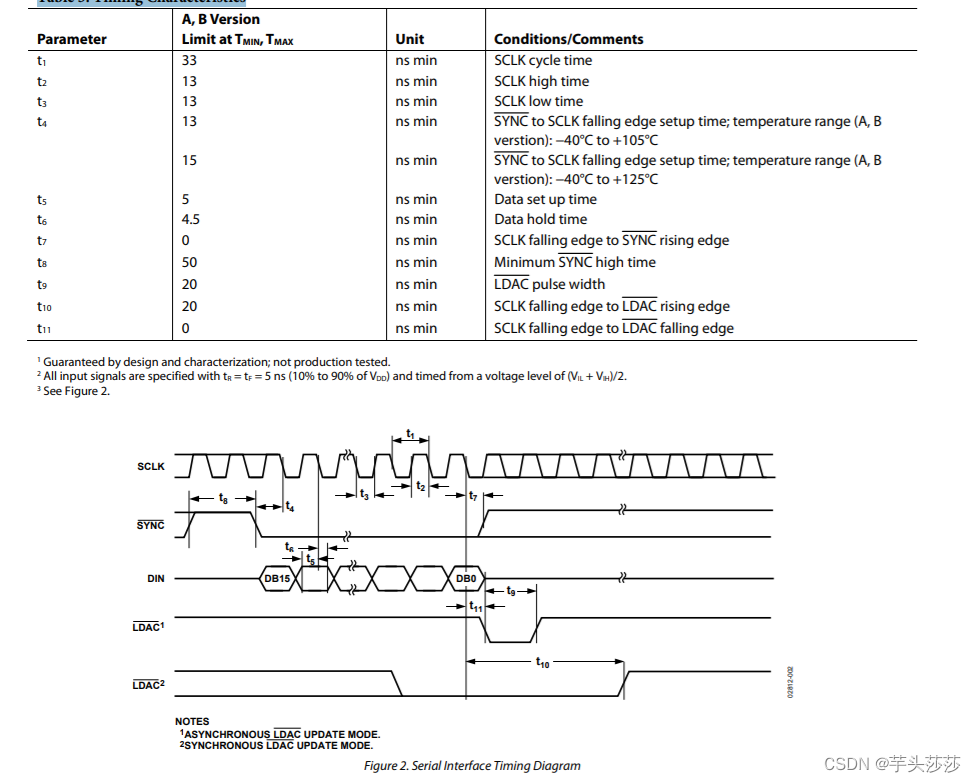

五、时间特性

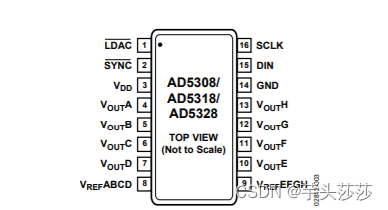

六、引脚配置和功能描述

(1) LDAC

该有效低控制输入将输入寄存器的内容传送到它们各自的DAC寄存器。如果输入寄存器具有新数据,则将此引脚脉冲设置为低允许更新任何或所有DAC寄存器。这允许同时更新所有DAC输出。

或者将这根引脚一直固定为低电平

(2)SYNC

主动低控制输入。这是输入数据的帧同步信号。当SYNC变低时,它接通SCLK和DIN缓冲器的电源,并启用输入移位寄存器。

数据在以下16个时钟的下降沿传输。如果SYNC在第16个下降沿之前取高,则SYNC的上升沿充当中断,设备将忽略写入序列。

简单说相当于SPI中的CS引脚,可以看上面时序图

(3)DIN

串行数据输入。该设备有一个16位移位寄存器。数据在串行时钟输入的下降沿被时钟记录到寄存器中。DIN输入缓冲器在每个写入周期后断电。

(4)SCLK

串行时钟输入。数据在串行时钟输入的下降沿被时钟输入到输入移位寄存器。数据传输速率可达30 MHz。SCLK输入缓冲器在每个写入周期后断电。

(5)VOUTA、VOUTB、VOUTC........这些是通道,还有通道的电源参考脚VREFABCD、VREFEFGH

七、操作理论

AD5308/AD5318/AD5328是基于CMOS工艺制造的八进制电阻串DAC,分辨率分别为8、10和12位。每个包含八个输出缓冲放大器,并通过三线串行接口写入。它们在2.5V至5.5V的单电源下工作,输出缓冲放大器以0.7V/μs的转换速率提供轨对轨输出摆动。DAC A、DAC B、DAC C和DAC D共享一个公共参考输入VREFABCD。DAC E、DAC F、DAC G和DAC H共享公共参考输入VREFEFGH。每个参考输入可以被缓冲以几乎不从参考源汲取电流,可以被非缓冲以给出从0.25V到VDD的参考输入范围,或者可以来自VDD。

设备具有断电模式,在该模式下,所有DAC都可以关闭,分别具有高阻抗输出。

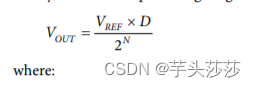

数模转换器

一个DAC通道的结构由电阻串DAC和输出缓冲放大器组成。

VREF引脚处的电压为相应的DAC提供参考电压。图29显示了DAC架构的框图。由于DAC的输入编码是直接二进制的,理想输出电压由下式给出:

D是加载到的二进制代码的十进制等效值(写入的值)

DAC寄存器:

N是DAC分辨率。

0 to 4095 for AD5328 (12 bits)

上电复位

AD5308/AD5318/AD5328具有通电复位功能,以便在规定状态下通电。通电状态为

•正常运行

•参考输入无缓冲

•0 V至VREF输出范围

•输出电压设置为0 V

•LDAC位设置为LDAC高

输入和DAC寄存器都用0填充,并保持不变

直到对设备进行有效的写入序列。这是

特别适用于需要了解

当设备通电时DAC输出的状态。

串行接口

AD5308/AD5318/AD5328通过多功能3线串行接口进行控制,该接口的时钟频率高达30 MHz,并与SPI、QSPI、MICROWIRE和DSP接口标准兼容。

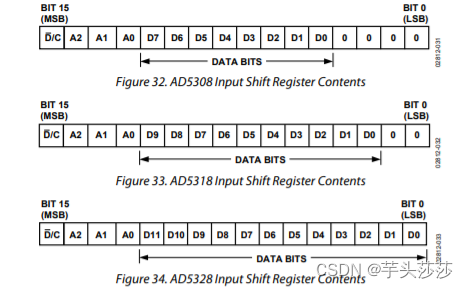

输入移位寄存器

输入移位寄存器为16位宽。在串行时钟输入SCLK的控制下,数据作为16位字加载到设备中。此操作的时序图如图2所示。

SYNC输入是一个电平触发输入,用作帧同步信号和芯片使能。只有当SYNC低时,数据才能传输到设备中。为了开始串行数据传输,SYNC应取低,观察最小SYNC到SCLK下降沿设置时间t4。SYNC变低后,串行数据被转移到设备的输入移位寄存器

16个时钟脉冲的SCLK的下降沿。为了结束传输,必须在第16个SCLK脉冲的下降沿之后将SYNC取高,观察最小SCLK下降沿到SYNC上升沿时间t7。串行数据传输结束后,数据自动从输入移位寄存器传输到所选DAC的输入寄存器。如果SYNC在SCLK的第16个下降沿之前取高,则数据传输中止,DAC输入不更新寄存器。

数据首先加载MSB(位15)。这一位确定它是DAC写入还是控制功能。

DAC写入

根据设备类型,16位字由1个控制位和3个地址位以及8、10或12位DAC数据组成。在DAC写入的情况下,MSB为0。

接下来的3个地址位确定数据是否用于DAC A、DAC B、DAC D、DAC E、DAC F、DAC G、DAC H。

AD5328使用所有12位DAC数据。AD5318使用10位并忽略2个LSB。(就是最低2位忽略)

AD5308使用8位,忽略最后4位(就是最低2位忽略)。这些被忽略的LSB应设置为0。

数据格式为直接二进制,所有0对应于0 V输出,所有1对应于满量程输出。

下图是地址表

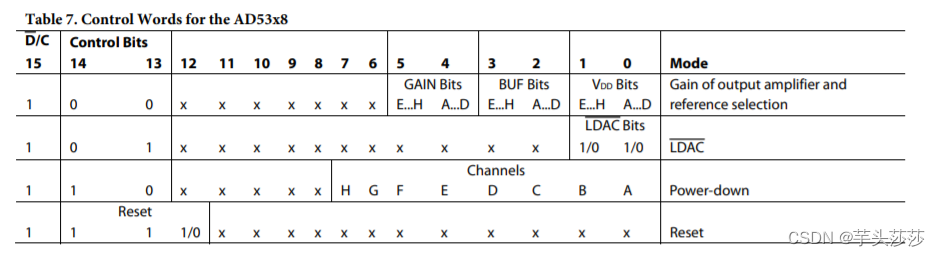

控制功能

在控制函数的情况下,MSB(位15)置为1。随后是两个控制位,用于确定模式。有四种不同的控制模式:参考和增益模式、LDAC模式、断电模式和复位模式。这些模式的写入顺序如表7所示。

参考和增益模式

此模式确定每组DAC的参考是缓冲的、非缓冲的还是来自VDD。它还决定输出放大器的增益。要设置两组的参考,请将控制位设置为(00),设置GAIN位、BUF位和VDD位。

缓冲器

这控制一组DAC的引用是缓冲的还是非缓冲的。第一组DAC(A、B、C和D)的参考通过设置位2来控制,第二组DAC(E、F、G和H)通过设置位3来控制。

0:无缓冲引用

1: 缓冲引用。

增益

通过设置第一组DAC(A、B、C和D)的位4和第二组DAC(E、F、G和H)的位5来控制DAC的增益。

0:0 V至VREF的输出范围。

1: 输出范围0 V至2 Vref。

表7。AD53x8的控制字

图34。AD5328输入移位寄存器内容

VDD做参考源的设置

当VDD用作参考时,(意思使用VDD作为参考源)设置这些位。第一组DAC(A、B、C和D)可以通过设置比特0来设置为使用VDD,第二组DAC(E、F、G和H)可以通过设定比特1来设置。VDD位优先于BUF位。

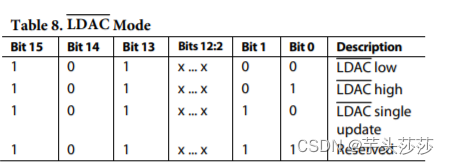

LDAC模式

LDAC模式控制,这个模式确定数据何时从输入寄存器传输到DAC寄存器。更新DAC寄存器时有三个选项,如表8所示。

LDAC低(00):此选项将LDAC设置为永久低,允许DAC寄存器连续更新。

LDAC高(01):此选项将LDAC设置为永久高。DAC寄存器被锁存,输入寄存器可以在不影响DAC寄存器内容的情况下进行更改。此模式是默认选项。

LDAC单次更新(10):此选项在LDAC上产生单脉冲,更新DAC寄存器一次

(11):预留

断电模式

AD5308/AD5318/AD5328的各个通道可以单独断电。此操作的控制模式为(1或0控制)。完成此写入序列后,已设置为1的通道将断电

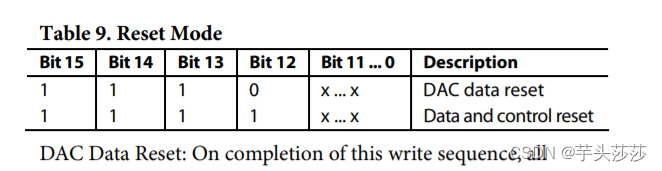

重置模式

该模式包括两种可能的重置功能,如表9所示。

DAC数据重置:完成此写入序列后,所有DAC寄存器和输入寄存器均填充0。

数据和控制重置:此功能执行DAC数据重置,并将所有控制位(增益、BUF、VDD、LDAC和断电通道)重置为其通电状态。

低功率串行接口

为了最大限度地降低设备的功耗,只有在设备被写入时,即SYNC下降时,接口才会完全通电。SCLK和DIN输入缓冲器在SYNC上升沿断电。牛逼

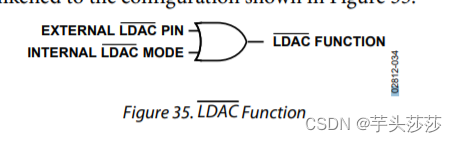

加载DAC输入(LDAC)函数

对DAC寄存器的访问由LDAC引脚和LDAC模式位控制。LDAC功能的操作可与图35所示的配置相比较

如果用户希望通过软件更新DAC,则应将LDAC引脚拉高,并根据需要设置LDAC模式位。

或者,如果用户希望通过硬件(即,LDAC引脚)控制DAC,则应将LDAC模式位设置为LDAC高(默认模式)。

这里我的理解:

第一种,如果要将写入的数据更新DAC输出,使用软件控制更新,那么就将引脚LDAC拉高,通过设置LDAC模式位即可更新。

第二种:使用LDAC引脚进行硬件触发更新,先将软件的LDAC模式位设置为高,然后再控制LDAC引脚的高低电平进行刷新DAC,低电平有效