对于顶层设计和

/

或包含

1000

个以上叶节点单元的层级单元

,

复杂性报告会显示每个叶节点单元类型的“

Rent Exponent”

(

Rent

指数

)

、“

Average Fanout

”

(

平均扇出

)

和分布。

Rent

指数是指在使用最小割

(min-cut)

算法以递归形式对设计进行分区时,

网表分区的端口数量和单元数量之间的关系。其计算方法与在全局布局期间布局器所使用的算法类似。因此,

它可明确指出布局器所遇到的困难

,

当设计层级与全局布局期间发现的物理分区精确匹配时尤其如此。

Rent

指数根据

Rent

规则定义如下

:

ports = constant x cells

Rent

log(ports) = Rent x log(cells) + constant

Rent

指数较高的设计表示此类设计中包含逻辑紧密相连的分组

,

并且这些分组与其他分组同样连接紧密。这通常可理解为全局布线资源使用率较高并且布线复杂性也更高。此报告中提供的 Rent

指数是根据未布局和未布线的网表来计算的。

完成布局后

,

相同设计的

Rent

指数可能改变

,

因为它基于物理分区而不是逻辑分区。

Report Design Analysis

命令不会报告布局后的 Rent

指数

,

因为建议改为在设计完成布局后再执行拥塞报告分析。执行以下任一操作时,

将以“

Complexity Mode

”

(

复杂性模式

)

来运行“

Report Design Analysis

”

(

设计分析报告):

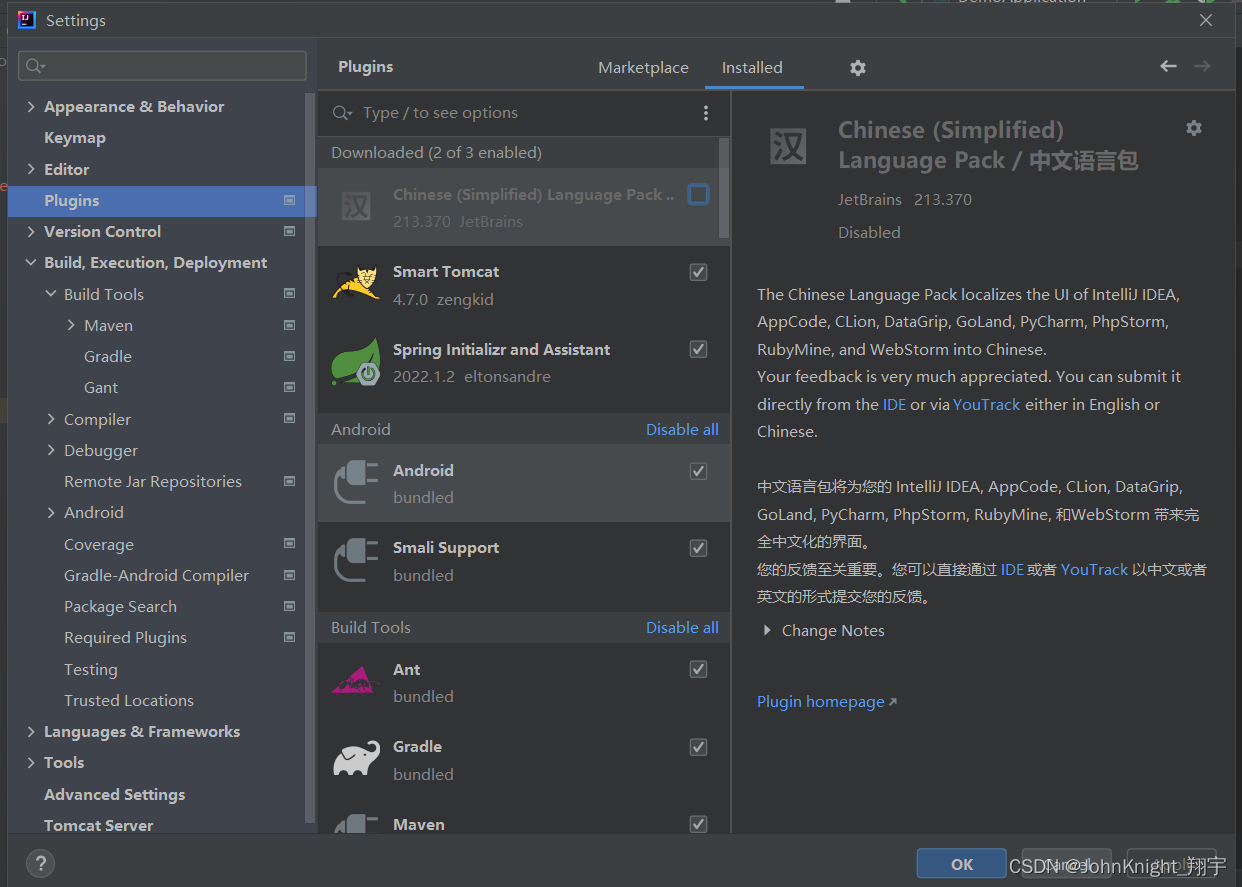

• 在“

Report Design Analysis

”对话框的“

Options

”选项卡中选中“

Complexity

”选项。

• 执行

report_design_analysis

Tcl

命令

,

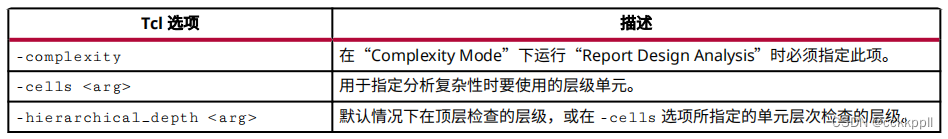

并使用下表中所示任意选项。

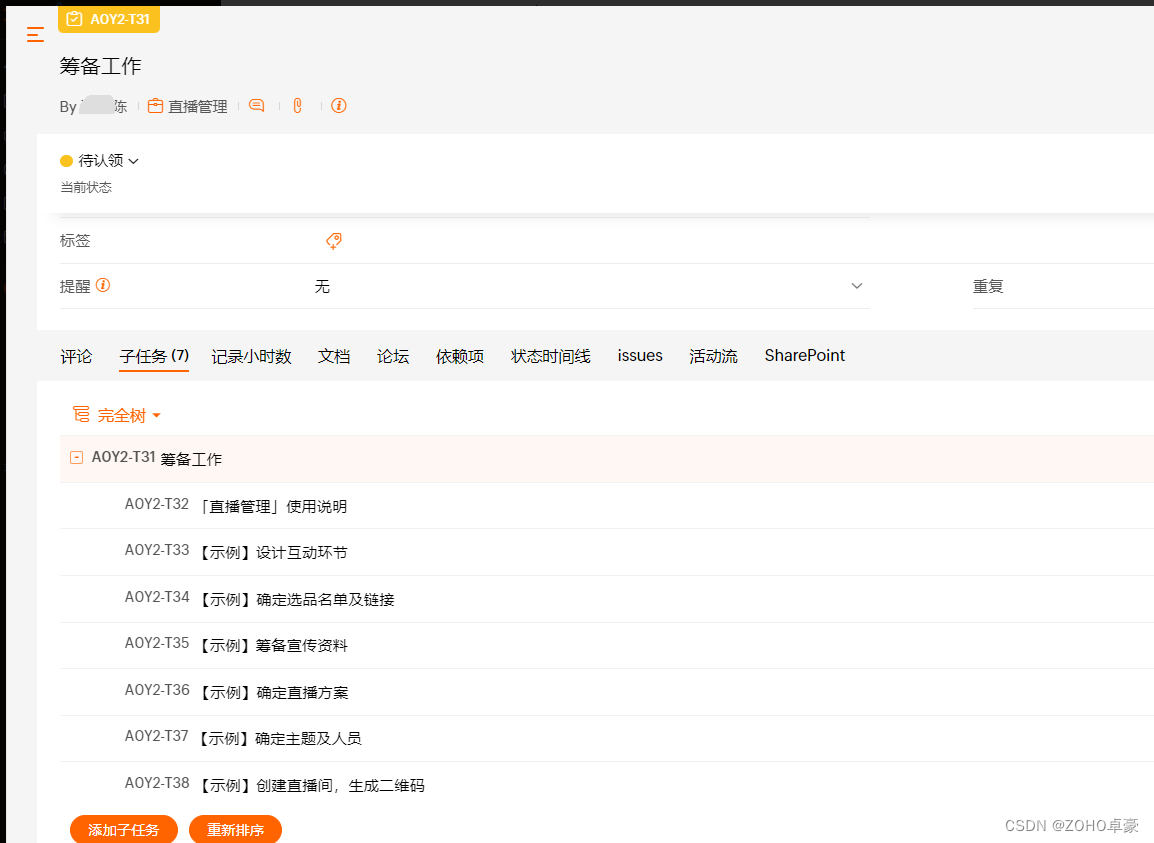

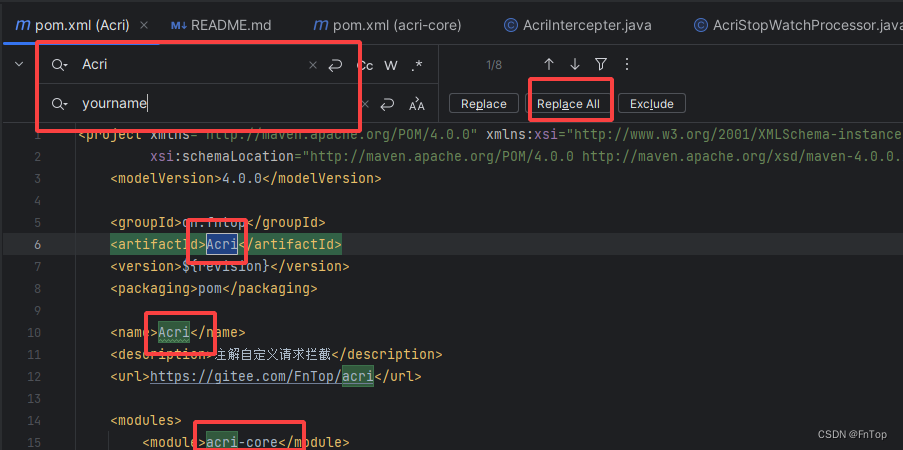

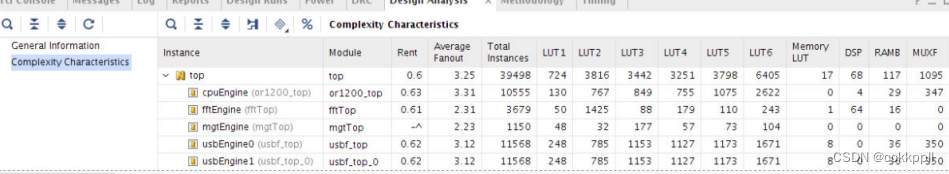

分析顶层设计复杂性

下图显示的示例报告来自“

Complexity Mode

”

(

复杂性模式

)

下的“

Report Design Analysis

”

(

设计分析报告

),

最多可报告至顶层模块下一层级。

Tcl

命令

:

report_design_analysis -complexity -hierarchical_depth 1

读取和解释复杂性报告

前例所示的“

Complexity Characteristics

”

(

复杂性特性

)

表显示了顶层以下每个层级的

Rent

指数和平均扇出。一般情况下,

复查这些指标时需要考量的范围包括

:

•

Rent

指数

:

介于

0.0

到

0.65

之间

:

判定复杂性处于较低到正常水平

,

不会导致任何潜在问题。

介于

0.65

到

0.85

之间

:

判定复杂性处于较高水平

,

当实例数量超过

25k

时尤其如此。

高于

0.85

:

复杂性非常高

,

如果实例数量同样很高

,

那么实现期间设计可能失败。

• 平均扇出

:

低于

4

:

判定为正常。

介于

4

到

5

之间

:

实现工具可能在布局设计时无法避免拥塞。就

SSI

器件而言

,

当实例总数大于

100k

时

,

布局器将难以找到能布局在 1

个

SLR

内或分布到

2

个以上

SLR

的解决方案。

高于

5

:

实现期间设计可能失败。

对于重要性较高的大型模块

,

必须解决

Rent

指数过高和

/

或平均扇出过高的问题。对于较小的模块

(

尤其是实例总数低于 10k

的情况下

),

Rent

指数和平均扇出可能较高

,

但仍可轻松成功完成布局布线。因此

,

必须始终将“

TotalInstances”

(

实例总数

)

列与

Rent

指数和平均扇出结合在一起进行审查。复杂性特性有时可能无法预测布线拥塞。诸如目标器件中的 I/O

位置约束、布局规划和宏原语位置等其他因素还会限 制布局解空间,

从而引起拥塞。完成布局后才能通过拥塞报告对此类约束的影响进行更准确的分析。

在解读“

Complexity Characteristics

”表时需要考虑的其他事项

:

• 模块中

LUT6

所占比例的增高通常会导致平均扇出增大

,

从而可能导致

Rent

指数增大。

• 大量

RAMB

和

DSP

的存在可能导致

Rent

指数增大

,

因为这些原语都具有大量连接。

•

Rent

指数较高或者平均扇出较高的层级实例有时不会导致问题

,

因为布局器在平面网表上工作

,

可将这些实例细分为更便于布局的逻辑组。如果存在明显不同寻常的模块,

此报告可提供有关可能存在网表问题的区域的指示信息。 当某个大型模块的 Rent

指数和

/

或平均扇出较高并导致拥塞和时序问题时

,

请考虑执行如下操作

:

• 减少模块的连接。保留层级

,

防止在综合内执行跨边界最优化

,

这样可减少

LUT6

的使用

,

从而降低网表密度。

• 尝试在综合中禁用

LUT

组合。

• 在实现期间使用“

Congestion Strategy

”

(

拥塞策略

)

或者使用

SpreadLogic

布局指令

,

这可能有助于缓解拥塞。如果设计目标为 SSI

器件

,

请尝试采用多种不同

SSI

布局指令。

• 在

SLR

层次针对

SSI

器件或者在通用时钟区域层次使用简单的布局规划使拥塞的逻辑组保持独立

,

或者引导全局布局向类似先前明确的良好布局相似的方向发展。