我的工作偏向硬件设计与调试,但是经过几年的发展,发觉不会调程序发展真的很受限制。最近越来越被这种限制折磨的很难受,所以开始学习调调程序。其实,本科与研究生阶段都有过做写代码的经历,算是入过门。但是,我还是比较喜欢跟电路板这种实实在在的东西打交道,所以工作毅然决然选择了硬件方向。现在遇到了些瓶颈,我暂以为有软件调试经验不足的原因,所以,开始重新学习软件了。

PGA的代码严格意义上不算是软件,而一旦调用IP核,软件的代码属性就更所剩无几了。但是,我固执的认为电路板才是硬件,其他凡是跟代码相关的都算是软件了。最开始接触FPGA的时候就是从UART开始的,现在重新接触FPGA,仍打算从UART开始。调试过程中遇到了一些问题,想记录一下,也希望能帮到一些跟我一样遇到了这些问题的人,因此就有了这篇文章。

FPGA型号:XC7K325TFFG900-3

软件:Vivado 2019.2 以及相应的Vitis、串口调试助手

整个工程建立的过程参照博客:【教程】Xilinx Vivado/Vitis 2020.1创建最简单的MicroBlaze工程运行Hello World C语言程序(不使用外部DDR3内存),并固化到SPI Flash_巨大八爪鱼的博客-CSDN博客![]() https://blog.csdn.net/ZLK1214/article/details/111824576?utm_medium=distribute.pc_relevant.none-task-blog-2~default~baidujs_baidulandingword~default-1-111824576-blog-86551813.pc_relevant_landingrelevant&spm=1001.2101.3001.4242.2&utm_relevant_index=4

https://blog.csdn.net/ZLK1214/article/details/111824576?utm_medium=distribute.pc_relevant.none-task-blog-2~default~baidujs_baidulandingword~default-1-111824576-blog-86551813.pc_relevant_landingrelevant&spm=1001.2101.3001.4242.2&utm_relevant_index=4

不同之处在于我用的是差分200MHz时钟,只需要修改clk_wid_1模块中的输入时钟参数即可。

遇到的问题:出现一个严重警告,大意是时序不对(现在无法复现了),导致串口输出乱码。

解决方法:

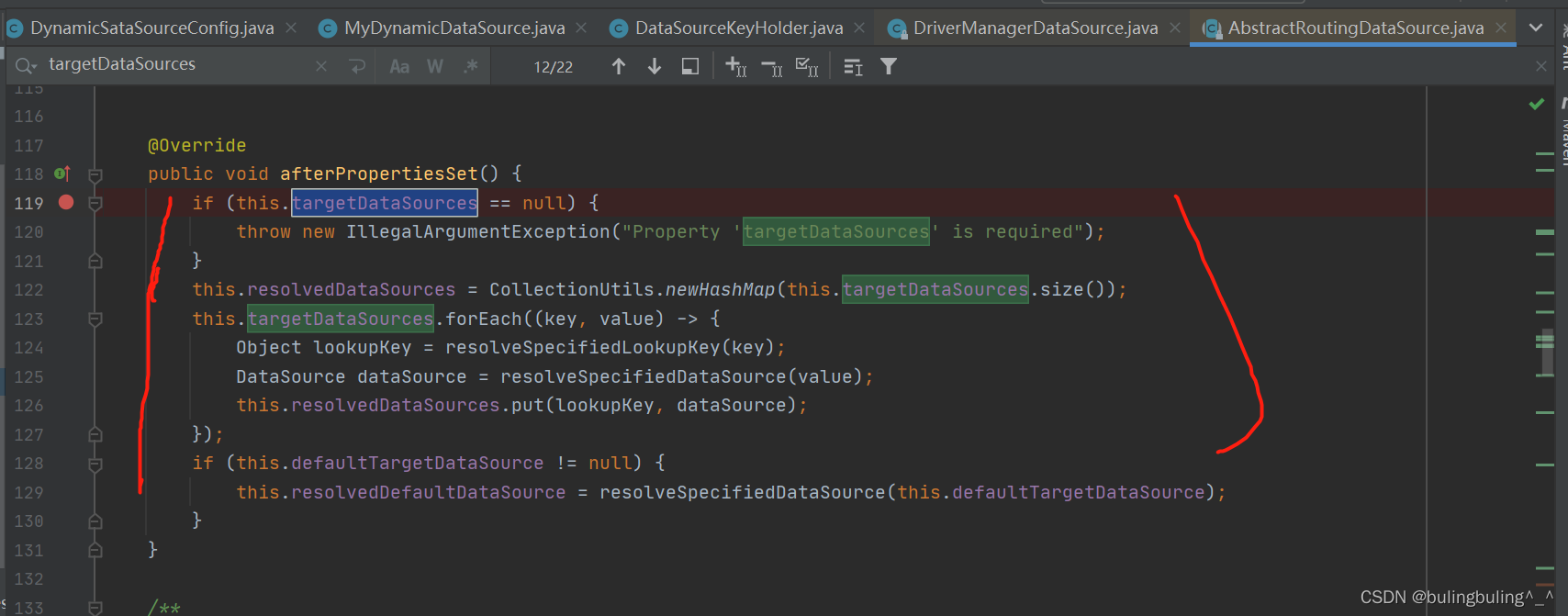

1. 对比了一下其他人的工程,发现下图中其他人的CLKFBOUT_MULT_F是4.5,CLKIN2_PERIOD是9,因此我选中了Allow Override Mode,修改了这两个值,严重警告就没了,串口输出正常。

2. 重新新建工程, 又来了一遍,没有警告,串口输出正常。(迷。。。。。)

![[3]ESP32连接MQTT服务端](https://img-blog.csdnimg.cn/c9fdaf530d80486da968e368a28a4195.png)