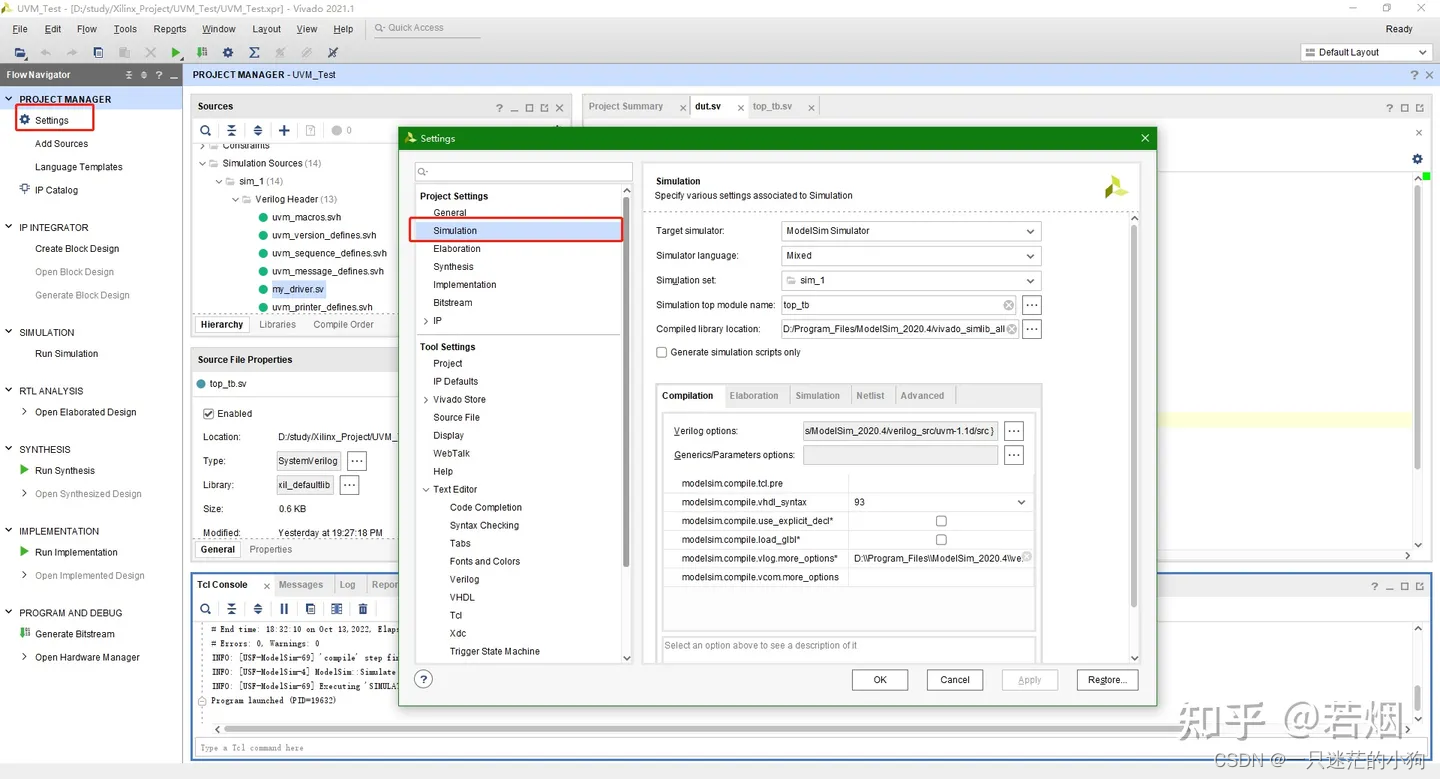

- 打开Vivado,打开对应工程,点击左侧Flow Navigator-->PROJECT MANAGER-->Settings,打开设置面板。

- 点击Project Settings-->Simulation选项卡,如下图所示。

-

将Target simulator设为Modelsim Simulator。

-

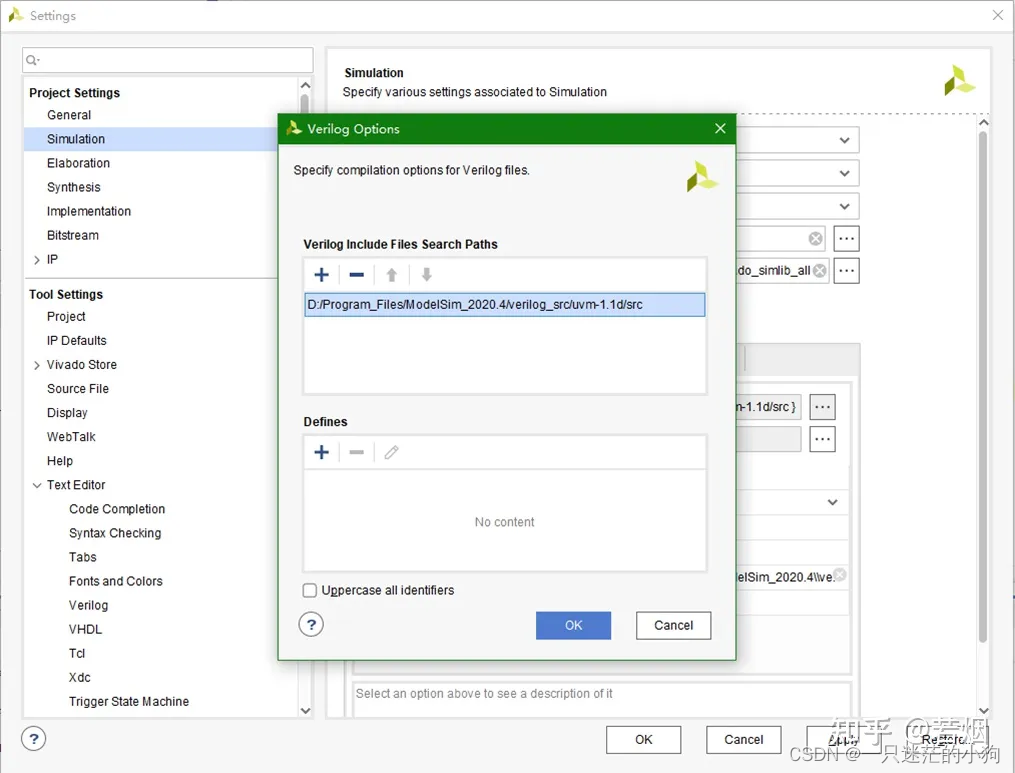

在下方的Compilation栏中,点击Verilog options右侧的…按钮,添加D:/Program_Files/ModelSim_2020.4/verilog_src/uvm-1.1d/src作为Verilog Include Files Search Paths,如下图所示。注意,D:/Program_Files/ModelSim_2020.4是我的Modelsim安装地址,Modelsim安装目录下就有对应的UVM库,这里选择verilog_src/uvm-1.1d/src。

-

在modelsim.compile.vlog.more_options中,输入D:/Program_Files/ModelSim_2020.4/verilog_src/uvm-1.1d/src/uvm_pkg.sv。同样,D:/Program_Files/ModelSim_2020.4是我的Modelsim安装地址,Modelsim安装目录下就有verilog_src/uvm-1.1d/src/uvm_pkg.sv。

-

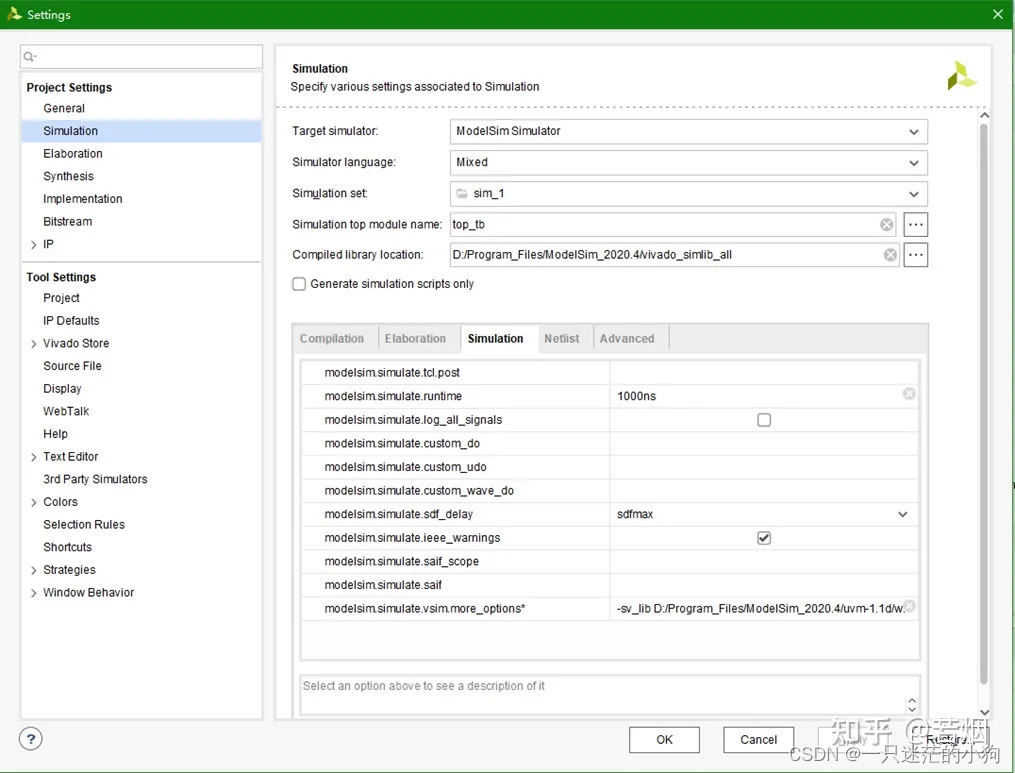

将Compilation栏切换为Simulation,在下方的modelsim.simulate.vsim.more_options中,输入-sv_lib D:/Program_Files/ModelSim_2020.4/uvm-1.1d/win64/uvm_dpi。,如下图所示。

-

在左上角Sources窗口中添加对应的设计文件和仿真文件,这里设计文件是dut.sv,仿真文件是top_tb.sv。

-

点击左侧Flow Navigator-->SIMULATION-->Run Simulation-->Run Behavior Simulation,运行行为级仿真。

-

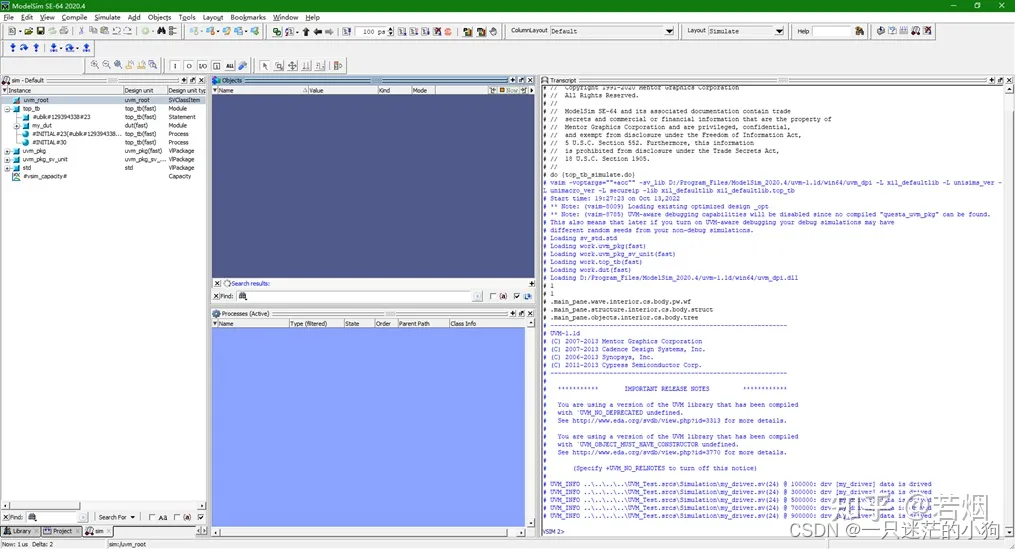

在Modelsim的Transcript窗口中,可以看到相应输出,当然也可以查看信号波形,如下图所示。

转自:Vivado & Modelsim联合进行UVM仿真指南 - 知乎

转自:Vivado & Modelsim联合进行UVM仿真指南 - 知乎

Vivado Modelsim联合进行UVM仿真指南

news2026/2/11 8:24:44

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如若转载,请注明出处:http://www.coloradmin.cn/o/1243789.html

如若内容造成侵权/违法违规/事实不符,请联系多彩编程网进行投诉反馈,一经查实,立即删除!相关文章

Kibana安装部署

目录 一、环境准备

二、安装部署

2.1 下载安装包到指定文件夹,并解压

2.2 重置kibana_system密码

2.3 编辑启动文件

2.3 进入界面

三、使用

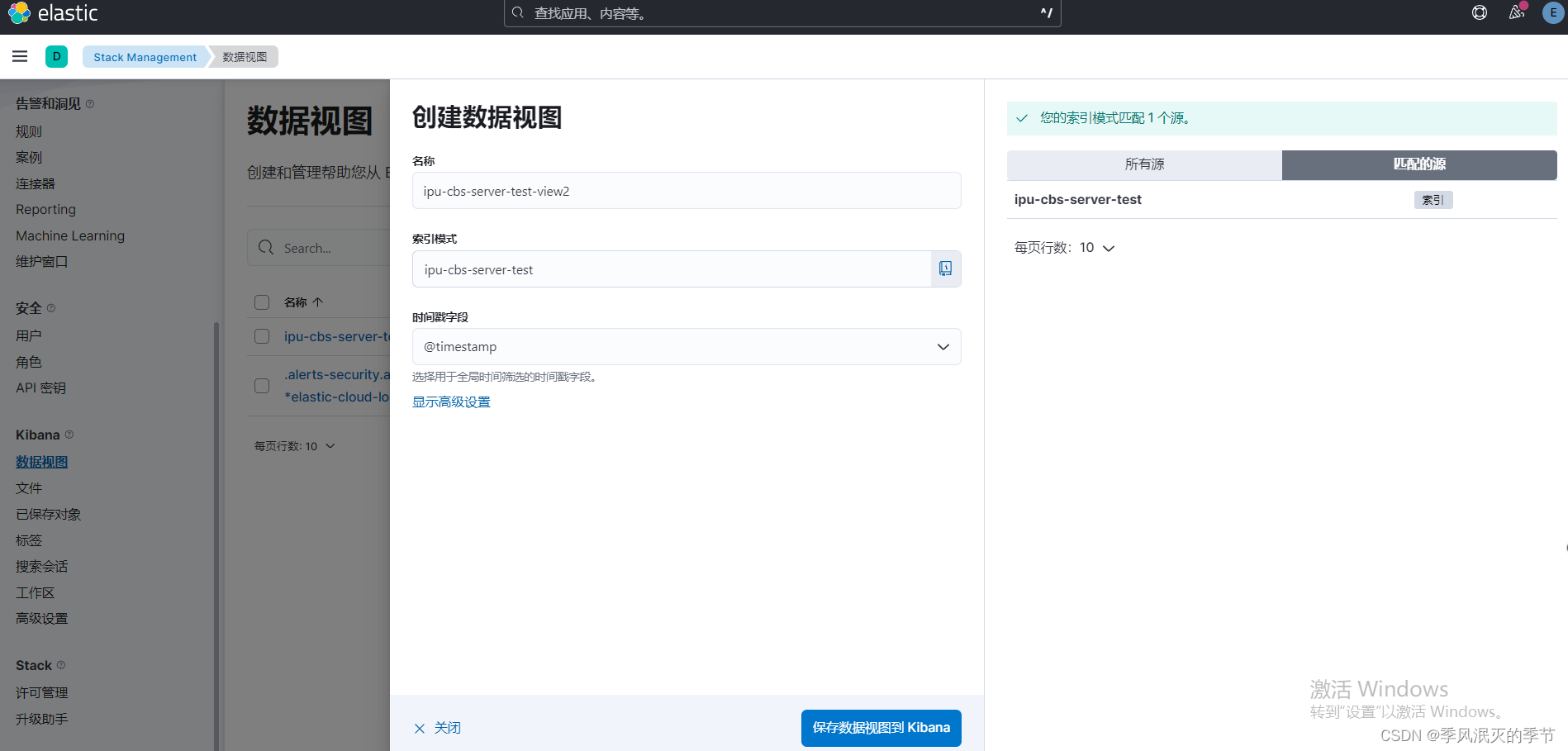

3.1 创建视图

3.2 视图优化 一、环境准备 部署模式:单节点部署。 官网地址:Elasticsearch 平…

【JavaSE】不允许你不会使用String类

🎥 个人主页:深鱼~🔥收录专栏:JavaSE🌄欢迎 👍点赞✍评论⭐收藏

目录

前言:

一、常用方法

1.1 字符串构造

1.2 String对象的比较

(1)比较是否引用同一个对象

注意…

C#中的迭代器和分部类

目录

一、迭代器

1.示例源码

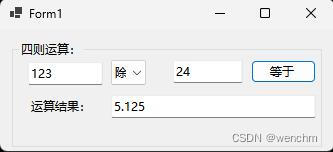

2.生成效果:

二、分部类

1.示例源码

2.生成效果 迭代器在集合类中经常使用,而分部类则提供了一种将一个类分成多个类的方法,这对于有大量代码的类非常实用。

一、迭代器 迭代器是可以返回相同类型的值的有…

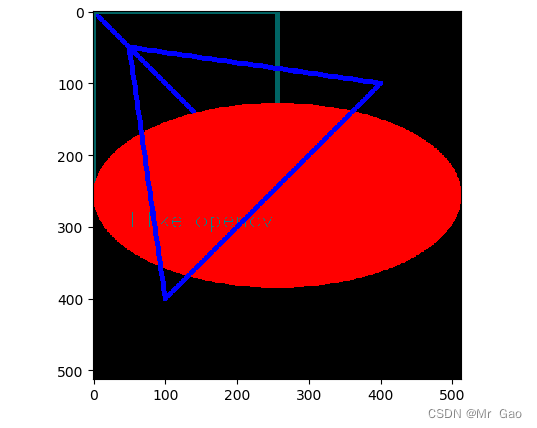

python-opencv在图片中绘制各种图形

python-opencv在图片中绘制各种图形

1.绘制直线

2.绘制矩形

3.绘制圆

4.绘制椭圆

5.绘制多边形

6.嵌入文字

实现代码都在下面了,代码中参数做了简单注释

import copy

import math

import matplotlib.pyplot as plt

import matplotlib as mpl

import numpy a…

全球三大网络安全威胁

网络安全IP数据云 - 免费IP地址查询 - 全球IP地址定位平台威胁日益复杂,涵盖了多个层面,从个人用户到大型企业,都面临着不同形式的网络安全威胁。以下是当前全球范围内广泛认可的三大网络安全威胁:

1. 恶意软件和病毒攻击&#x…

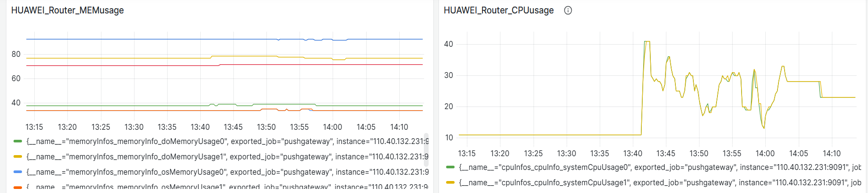

新一代网络监控技术——Telemetry

一、Telemetry的背景

传统的网络设备监控方式有SNMP、CLI、Syslog、NetStream、sFlow,其中SNMP为主流的监控数据方式。而随着网络系统规模的扩大,网络设备数量的增多,网络结构的复杂,相应监控要求也不断提升,如今这些…

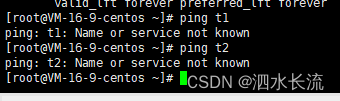

11.docker的网络-docker0的理解及bridge网桥模式的介绍与实例

1.docker0的基本理解

安装完docker服务后,我们首先查看一下宿主机的网络配置

ifconfig我们可以看到,docker服务会默认在宿主机上创建一个虚拟网桥docker0,该网桥网络的名字称为docker0。它在内核层连通了其他物理或者虚拟网卡,这…

微服务实战系列之Feign

前言

不知不觉,“微服务实战系列”已完成了六篇,每篇都聚焦一个主题,目的是便于各位盆友能够快速、全面地接收和消化。 博主从服务注册到服务监控,从服务路由到服务安全,从身份认证到加密技术均有涉猎。凡此均有关微服…

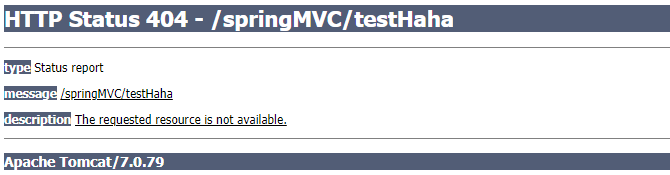

SpringMVC(三)

十、拦截器

1、拦截器的配置

SpringMVC中的拦截器用于拦截控制器方法的执行

SpringMVC中的拦截器需要实现HandlerInterceptor

SpringMVC的拦截器必须在SpringMVC的配置文件中进行配置:

<bean class"com.atguigu.interceptor.FirstInterceptor">…

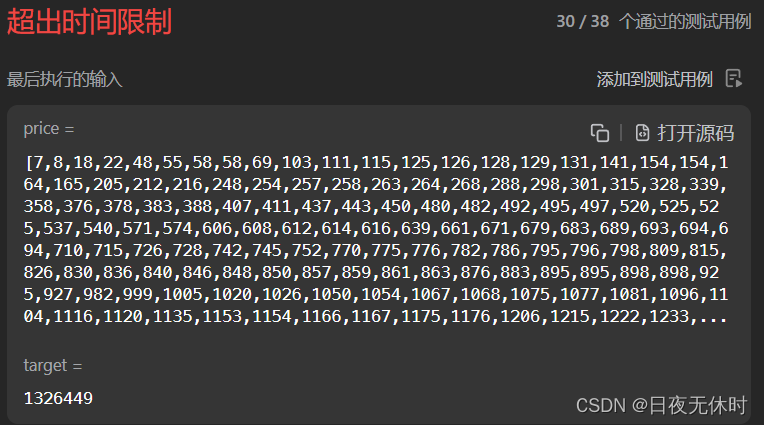

【双指针】和为 s 的两个数字

和为 s 的两个数字 文章目录 和为 s 的两个数字题目描述算法思路暴力枚举双指针 代码编写Java代码C代码编写 LCR 179. 查找总价格为目标值的两个商品 - 力扣(LeetCode) 题目描述

购物车内的商品价格按照升序记录于数组 price。请在购物车中找到两个商品…

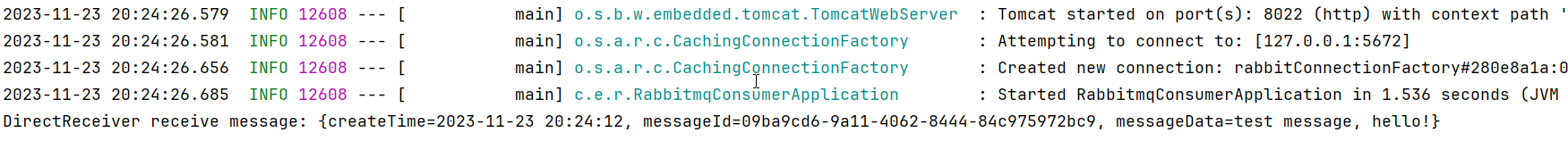

『RabbitMQ』入门指南(安装,配置,应用)

前言

RabbitMQ 是在 AMQP(Advanced Message Queuing Protocol) 协议标准基础上完整的,可复用的企业消息系统。它遵循 Mozilla Public License 开源协议,采用 Erlang 实现的工业级的消息队列(MQ)服务器,建立在 Erlang …

UML建模图文详解教程01——Enterprise Architect的安装与使用

版权声明

本文原创作者:谷哥的小弟作者博客地址:http://blog.csdn.net/lfdfhl Enterprise Architect概述

官方网站:https://www.sparxsystems.cn/products/ea/;图示如下:

Enterprise Architect是一个全功能的、基于…

ES 万条以外分页检索功能实现及注意事项

背景

以 ES 存储日志,且需要对日志进行分页检索,当数据量过大时,就面临 ES 万条以外的数据检索问题,如何利用滚动检索实现这个需求呢?本文介绍 ES 分页检索万条以外的数据实现方法及注意事项。

需求分析 用 ES 存储数…

单个视频生成视频二维码,手把手图文教程

单个视频生成视频二维码帮助教程(图文教程),手把手教程如下:

STEP1 注册帐号

使用视频二维码,您需要注册酷播云用户帐号(免费5G空间,普通用户够用)。

参考如图1-1,按照…

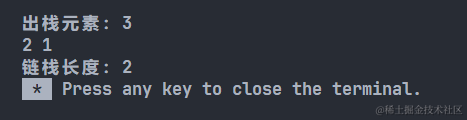

【数据结构/C++】栈和队列_链栈

链头 栈顶。 #include<iostream>

using namespace std;

// 链栈

typedef int ElemType;

typedef struct Linknode {ElemType data;struct Linknode *next;

} *LiStack;

// 初始化

void InitLiStack(LiStack &S) {S (LiStack)malloc(sizeof(struct Linknode));S->…

安全框架springSecurity+Jwt+Vue-2(后端开发)

一、创建项目及配置

①:创建新的项目及常用包 ②:引入依赖和配置

devtools:项目的热加载重启插件 <dependency><groupId>org.springframework.boot</groupId><artifactId>spring-boot-starter-web</artifactId&…

RK3399平台开发系列讲解(内核入门篇)ConfigFS 的核心数据结构

🚀返回专栏总目录 文章目录 一、关键数据结构二、config_item 的结构体三、属性和方法沉淀、分享、成长,让自己和他人都能有所收获!😄 📢虚拟文件系统 ConfigFS 是一个特殊的文件系统,旨在提供一种动态配置 Linux 内核和设备的机制。

一、关键数据结构 ConfigFS 的核…

[23] 4K4D: Real-Time 4D View Synthesis at 4K Resolution

paper | proj | code 提出一种基于K-Planes的4D point cloud Representation;提出一种Hybrid appearance model,包含image blending model和SH model。其中,image blending model将3D点映射回原图中求得,SH model通过模型预测求得…

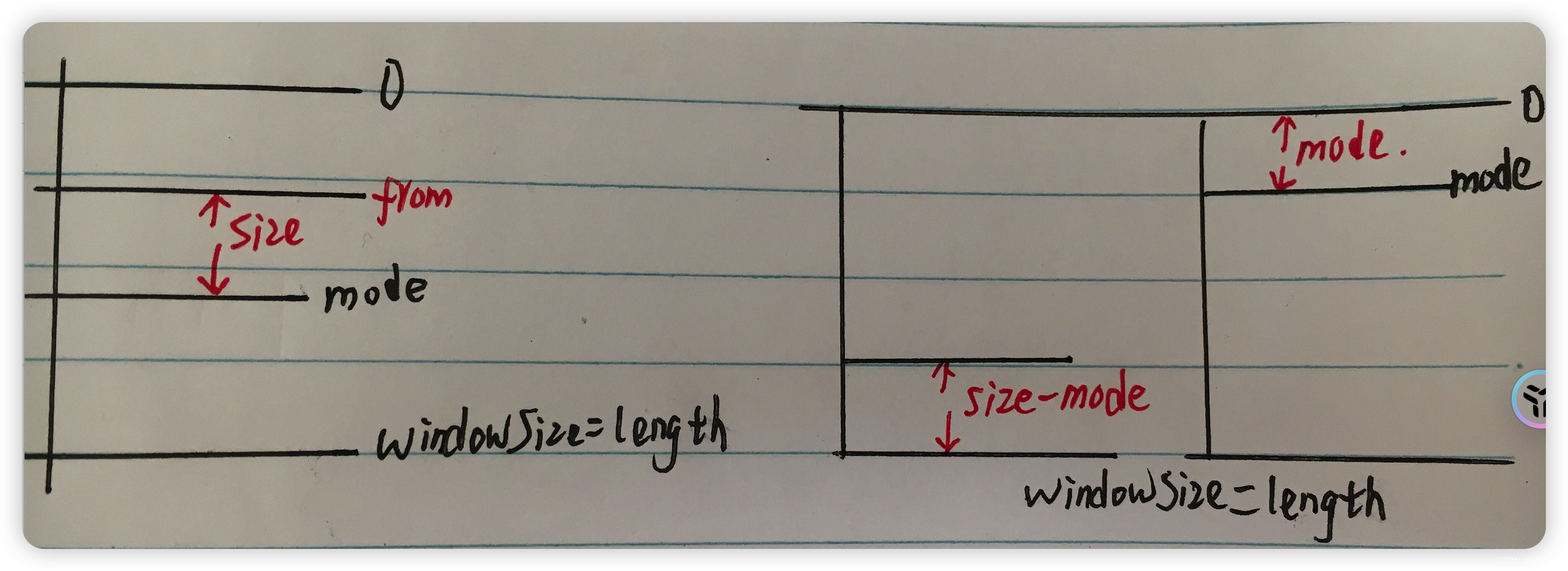

机器学习/sklearn笔记:MeanShift

1 算法介绍

一种基于质心的算法通过更新候选质心使其成为给定区域内点的均值候选质心的位置是通过一种称为“爬山”技术迭代调整的,该技术找到估计的概率密度的局部最大值

1.1 基本形式

给定d维空间的n个数据点集X,那么对于空间中的任意点x的均值漂移…

HCIP --- HCIA(部分汇总)--- 点对点网络

抽象语言 --- 电信号 抽象语言 --- 编码 编码 --- 二进制 二进制 --- 电信号 处理电信号 OSI/RM ---- 开放式系统互联参考模型 --- 1979 --- ISO --- 国际标准化组织 核心思想 --- 分层 应用层 --- 提供各种应用程序,抽象语言转换成编码,人机交互…

![[23] 4K4D: Real-Time 4D View Synthesis at 4K Resolution](https://img-blog.csdnimg.cn/2fe2494acd46467b84c20b186df5f5a1.png)