双非硕士 研一下学期视觉转FPGA(在b站跟小梅哥视频)

长路漫漫,但希望前途光明

此篇文章开始省去建工程的操作,如果有不懂的同学可以看我之前的两篇文章。

1.新建文件名为:led_flash,等待右侧弹出Verilog代码框。

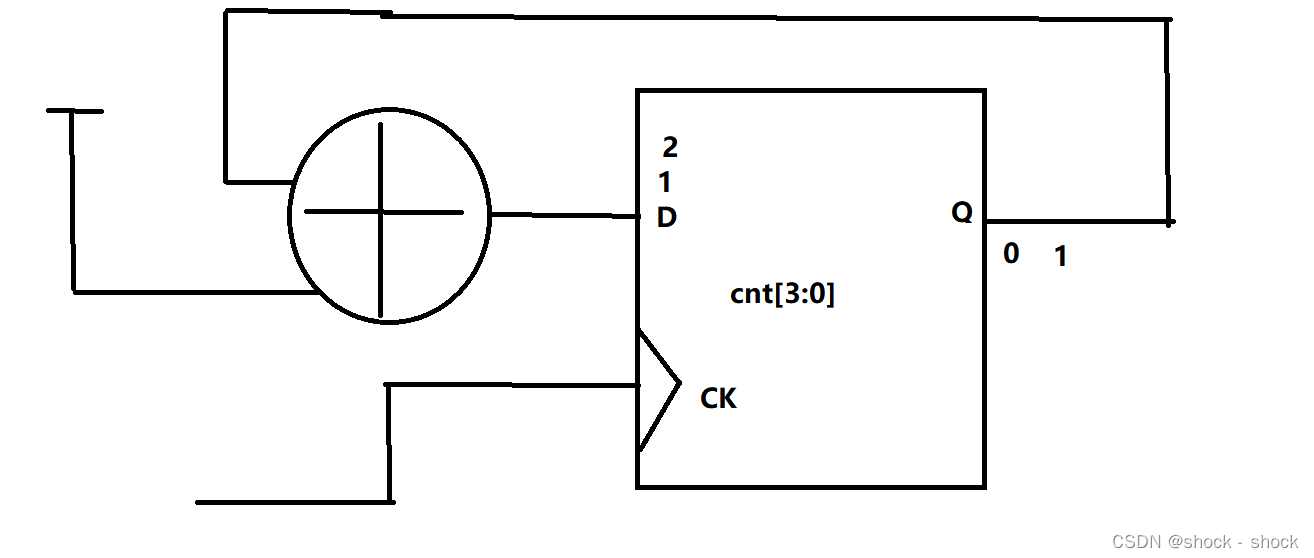

2.计数器逻辑图如下

3.以1秒频率闪烁的LED灯的代码内容如下:

//设计一个以1秒频率闪烁的LED灯(亮灭各500ms)

module led_flash(

Reset_n,//复位端口,加_n是使用低电平复位

Clk,//时钟端口

Led,

);

input Clk;

input Reset_n;

output reg Led;

reg [24:0]counter;

always@(posedge Clk or negedge Reset_n) //posedge Clk 为时序描述的标准格式

// <=是非阻塞赋值的意思

if(!Reset_n)

counter <= 0;

else if(counter == 250000000-1)

counter<=0;

else

counter <= counter+1'd1;

always@(posedge Clk or negedge Reset_n)

if(!Reset_n)

Led <= 0;

else if(counter == 25000000)

Led <=!Led;

// always@(posedge Clk or negedge Reset_n) //posedge Clk 为时序描述的标准格式

// // <=是非阻塞赋值的意思

// if(!Reset_n)begin

// counter <= 0;

// Led <=0;

// end

// else if(counter == 25000000-1)begin

// Led <=!Led;

// counter<=0;

// end

// else

// counter <= counter+1'd1;

endmodule4.进行仿真测试,操作步骤与前面两篇文章类似,这里就不重复了,直接上仿真测试的代码:

`timescale 1ns/1ns

module led_flash_tb();

reg Clk;

reg Reset_n;

wire Led;

led_flash led_flash(

.Reset_n(Reset_n),//复位端口,加_n是使用低电平复位

.Clk(Clk),//时钟端口

.Led(Led)

);

//时钟信号

initial Clk =1;

always #10 Clk=!Clk;

initial begin

Reset_n=0;

#201;

Reset_n=1;

#2000000000;

$stop;

end

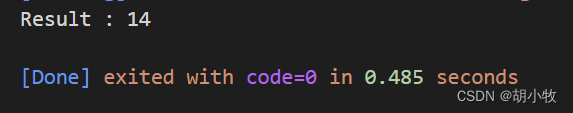

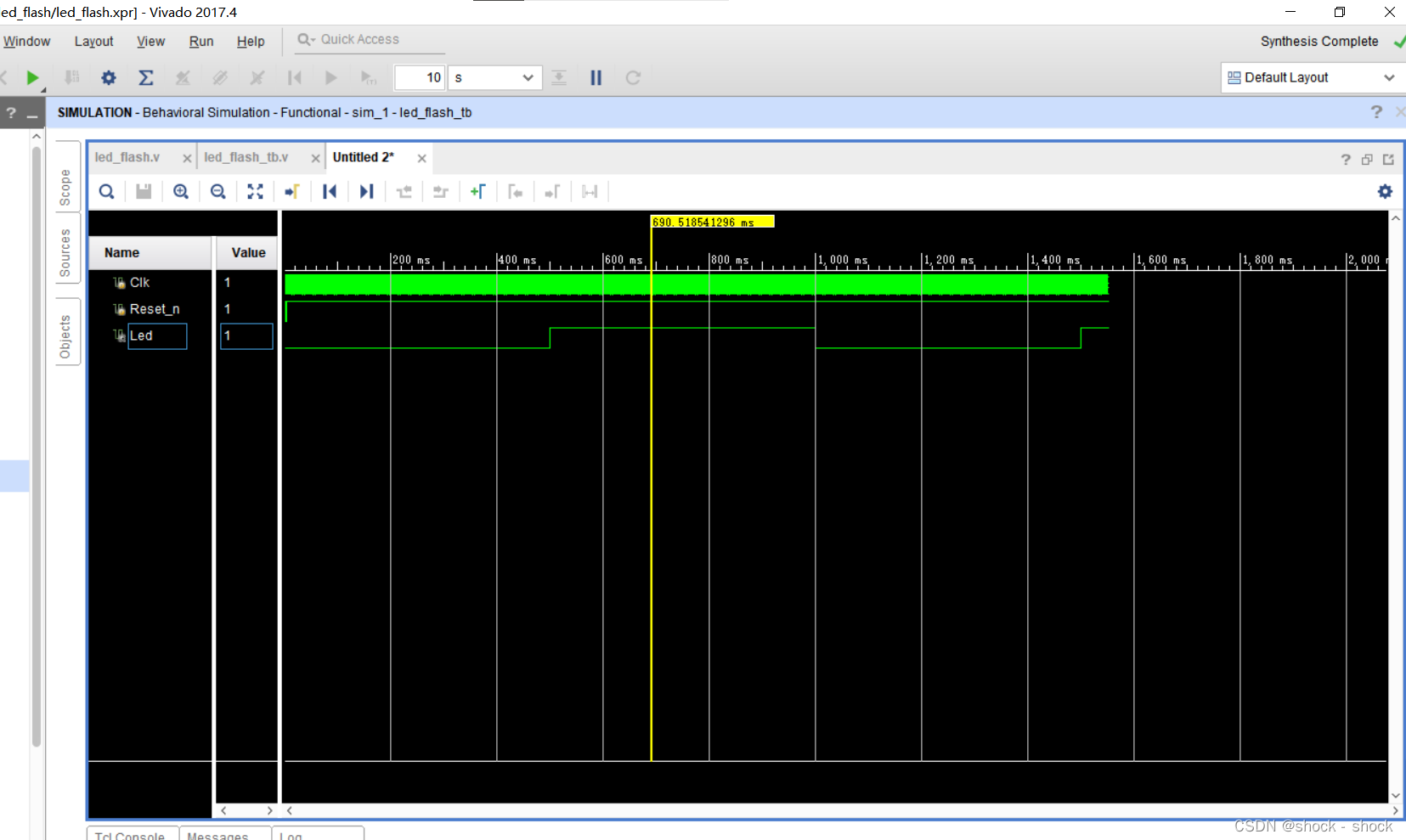

endmodule经过仿真实验,可以看到波形图如下所示:

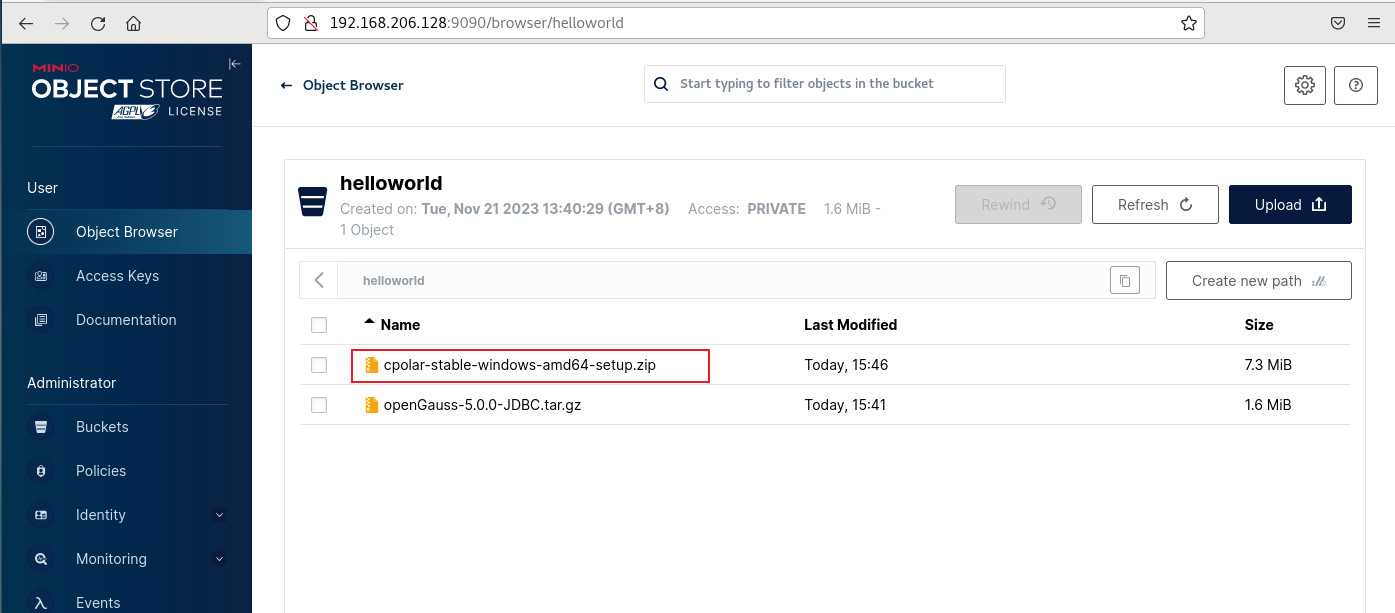

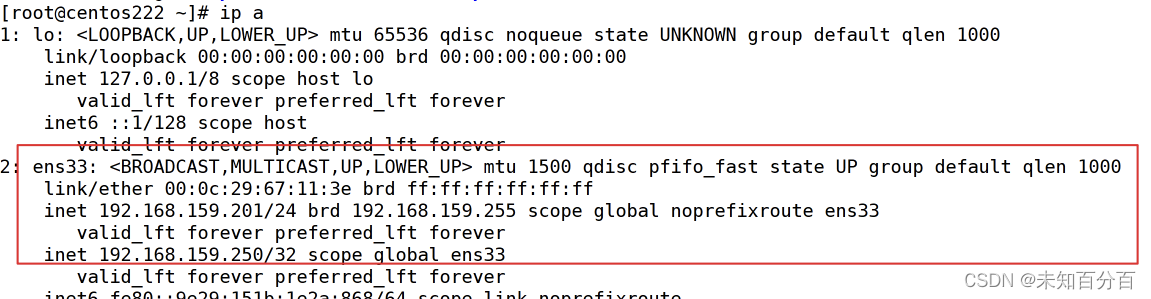

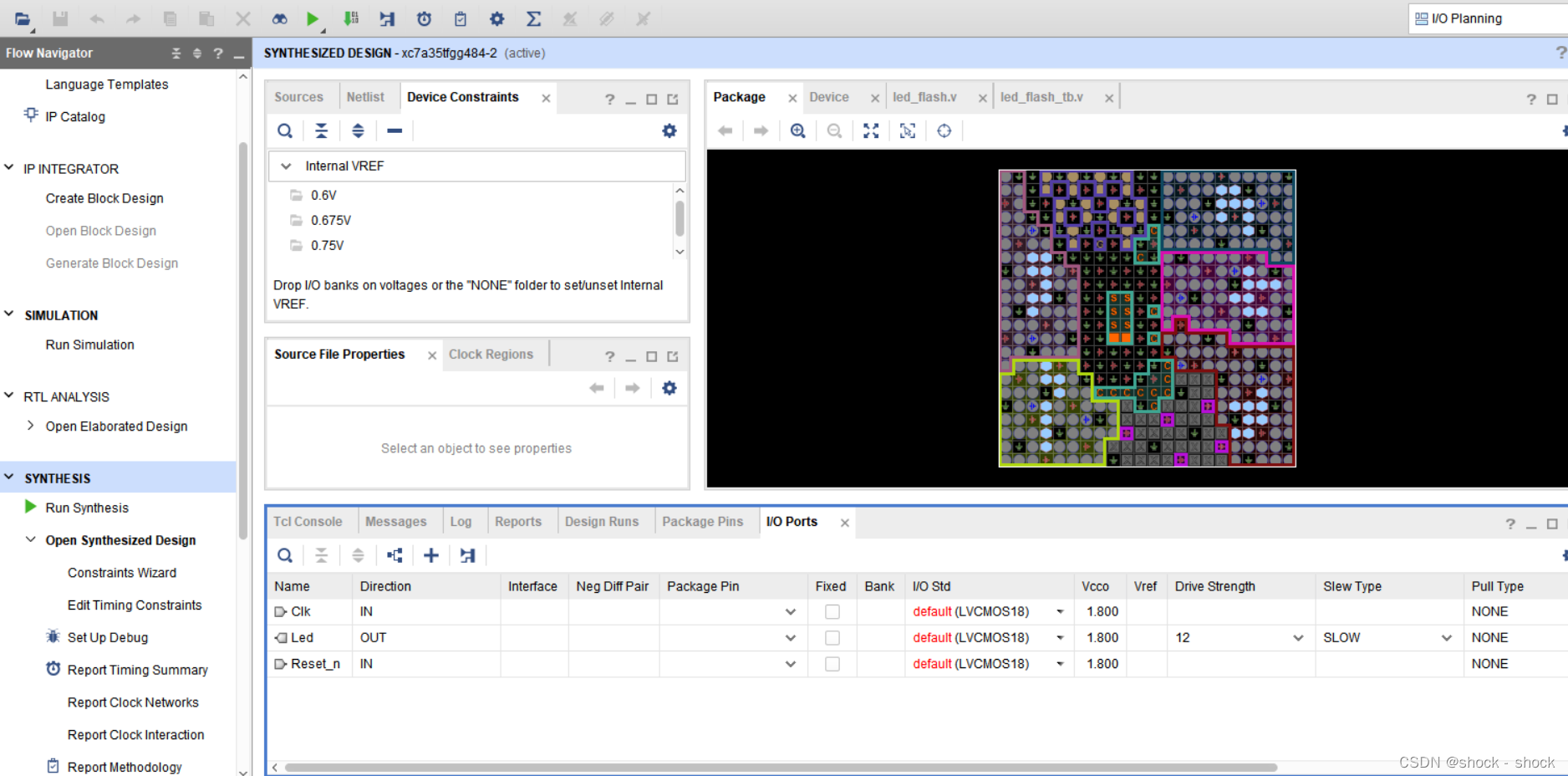

5.进行板机验证,首先进行管脚验证,双击左侧选择栏中的Open Synthesized Design,右侧会出现以下界面

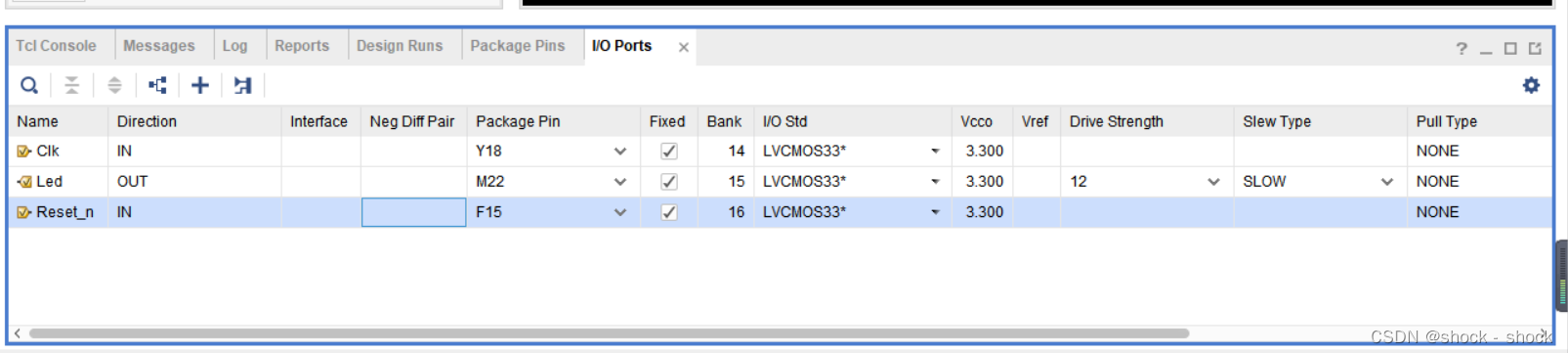

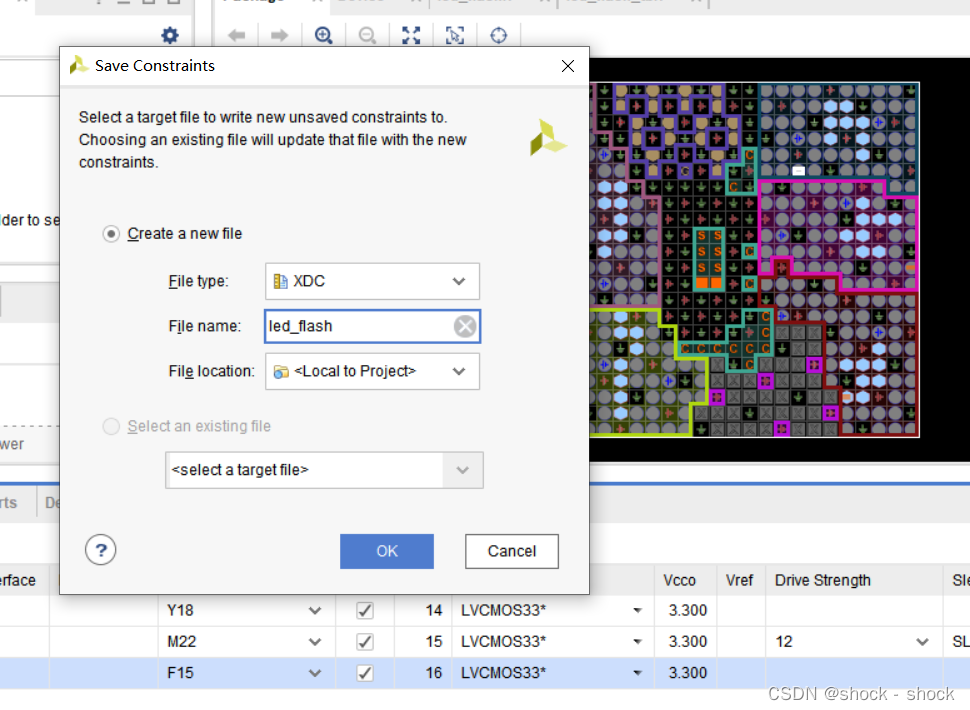

将I/O全部修改为LVCMOS33,并输入引脚名,输入好后 Ctrl+s保存,如下图所示

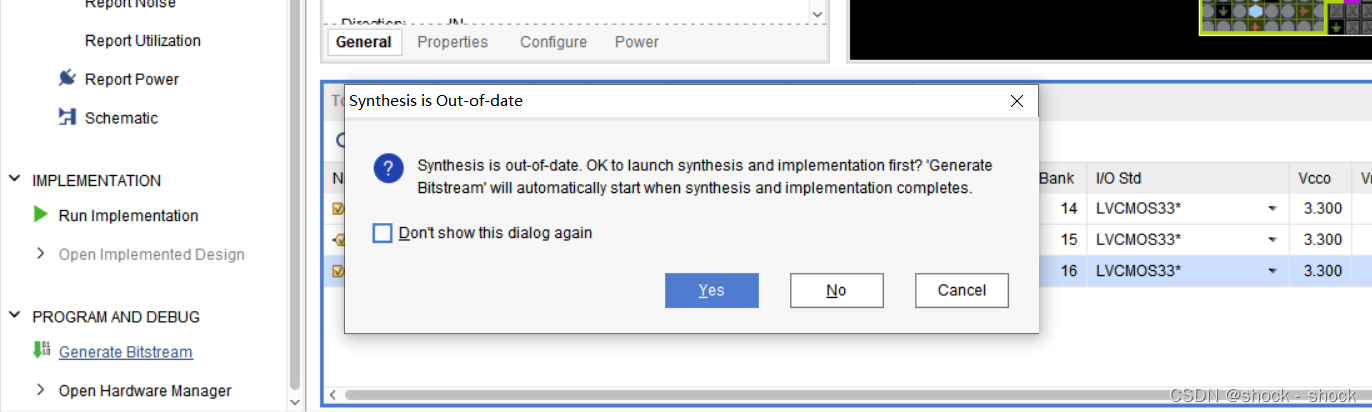

点击Generate Bitstream

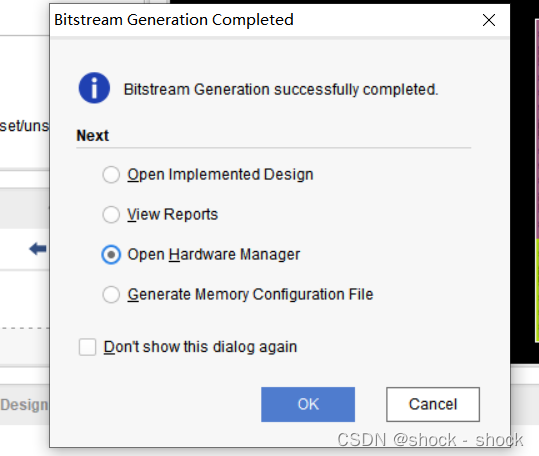

再选择Open Hardware Manager即可在开发板上运行。

好了,以上就是通过vivado模拟实现1秒亮灯一次的fpga程序。