时序分析关键概念

1、最大和最小延迟分析

时序分析属静态验证

,

旨在验证在硬件上加载并运行设计后

,

其时序行为的可预测性。它会将各种制造和环境变化因素组合到延迟模型中并按时序角及其变化量加以分组,

将所有这些要素一并纳入考量范围。针对所有建议的时序角分析时序即可,

针对每个角

,

按最消极的条件执行所有检查。例如

,

以

AMD FPGA

为目标的设计必须通过以下

4

项分析

:

• 慢速角

(Slow Corner)

中的最大延迟分析

• 慢速角

(Slow Corner)

中的最小延迟分析

• 快速角

(Fast Corner)

中的最大延迟分析

• 快速角

(Fast Corner)

中的最小延迟分析

根据执行的检查

,

将使用展现出最消极情况的延迟。因此下列检查与延迟类型始终关联

:

•

含建立时间和恢复时间检查的最大延迟

•

保持和移除检查的最小延迟

2、含建立时间和恢复时间检查的最大延迟

• 针对源时钟路径和数据

/

复位路径累积延迟

,

使用给定角

(corner)

的最差情况延迟

(

最慢延迟

)

。

• 针对目标时钟路径累积延迟同样使用该角

(corner)

的最佳情况延迟

(

最快延迟

)

。

3、保持和移除检查的最小延迟

• 针对源时钟路径和数据

/

复位路径累积延迟

,

使用给定角

(corner)

的最佳情况延迟

(

最快延迟

)

。

• 针对目标时钟路径累积延迟同样使用该角

(corner)

的最差情况延迟

(

最慢延迟

)

。

映射到多个角时

,

可使用以下检查

:

•

建立

/

恢复

(

最大延迟分析

)

•

保持

/

移除

(

最小延迟分析

)

4、建立

/

恢复

(

最大延迟分析

)

• 源时钟

(Slow_max)

,

数据路径

(Slow_max)

,

目标时钟

(Slow_min)

• 源时钟

(Fast_max)

,

数据路径

(Fast_max)

,

目标时钟

(Fast_min)

5、保持

/

移除

(

最小延迟分析

)

• 源时钟

(Slow_min)

,

数据路径

(Slow_min)

,

目标时钟

(Slow_max)

• 源时钟

(Fast_min)

,

数据路径

(Fast_min)

,

目标时钟

(Fast_max)

在同一路径上从不混用来自不同时序角

(corner)

的延迟进行裕量计算。

大多数情况下

,

建立或恢复违例发生时存在慢速

(Slow)

角延迟

,

保持或移除违例发生时存在快速

(Fast)

角延迟。但由于偶有例外(

尤其是对于

I/O

时序

),

AMD

建议您在

2

个角上都执行

2

项分析。

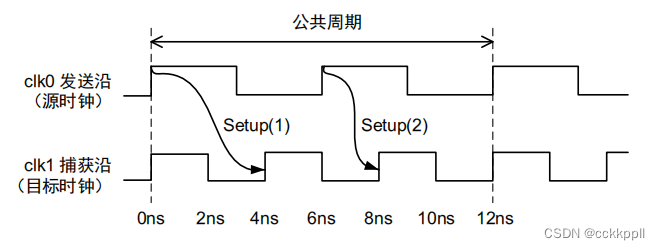

6、建立

/

恢复关系

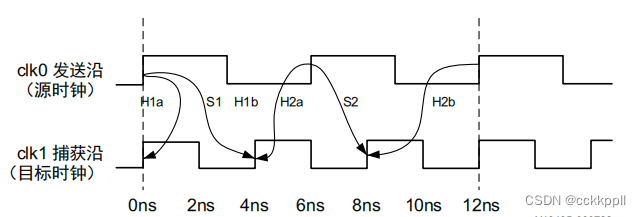

仅对

2

个时钟之间最消极的建立关系执行建立时间检查。默认情况下

,

此项检查对应于发送沿与捕获沿之间最小正增量。以 2

个触发器之间的路径为例

,

这

2

个触发器易受其各自时钟的上升沿影响。此路径的发送沿和捕获沿均仅为时 钟上升沿。

其时钟具体定义如下

:

•

clk0

的周期为

6 ns

,

首个上升沿位于

0 ns

,

下降沿位于

3 ns

。

•

clk1

的周期为

4 ns

,

首个上升沿位于

0 ns

,

下降沿位于

2 ns

。

如下图所示

,

存在

2

个唯一的建立关系

:

Setup(1)

和

Setup(2)

从

clk0

到

clk1

的最小正增量为

2 ns

,

对应于

Setup(2)

。“

Common Period

”

(

公共周期

)

为

12 ns

,

对应于

2

个时钟的 2

个同步对齐之间的时间。

7、保持

/

移除关系

保持时间检查

(

也称为保持关系

)

与建立关系直接相连。虽然建立时间分析可确保在最消极的场景中仍可安全捕获数据,

但保持关系可确保

:

• 由建立发送沿所发送的数据不会被位于建立捕获沿之前的活动沿

(

下图中分别对应于建立沿

S1

和

S2

的

H1a

和 H2a)

所捕获。

• 由位于建立发送沿之后的下一个活动源时钟沿发送的数据不会被建立捕获沿

(

下图中分别对应于建立沿

S1

和

S2

的H2a 和

H2b

)

所捕获。

保持分析期间

,

时序引擎仅报告任意

2

个时钟之间最消极的保持关系。最消极的保持关系并非始终与最差建立关系关联。时序引擎必须复查所有可能的建立关系及其对应的保持关系才能识别最消极的保持关系。 仍以建立关系示例中的路径为例。存在 2

项唯一的建立关系。